# <u>EECS150 – Digital Design</u> <u>Lecture 4 – Synchronous</u> <u>Digital Systems Review Part 2</u>

January 27, 2011

John Wawrzynek Electrical Engineering and Computer Sciences University of California, Berkeley

http://www-inst.eecs.berkeley.edu/~cs150

Spring 2011

EECS150 lec04-SDS-review2

Page 1

## <u>Outline</u>

- Topics in the review, you have already seen in CS61C, and possibly EE40:

- 1. Digital Signals.

- 2. General model for synchronous systems.

- 3. Combinational logic circuits

- 4. Flip-flops, clocking

# **Only Two Types of Circuits Exist**

- Combinational Logic Blocks (CL)

- State Elements (registers)

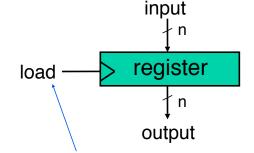

# State Elements: circuits that store info

- Examples: registers, memories

- Register: Under the control of the "load" signal, the register captures the input value and stores it indefinitely.

often replace by clock signal (clk)

- The value stored by the register appears on the output (after a small delay).

- Until the next load, changes on the data input are ignored (unlike CL, where input changes change output).

- These get used for short term storage (ex: register file), and to help move data around the processor.

Spring 2011

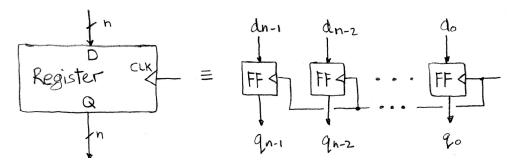

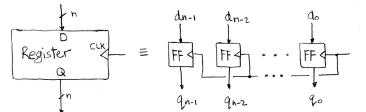

#### **Register Details...What's inside?**

- n instances of a "Flip-Flop"

- Flip-flop name because the output flips and flops between and 0,1

- D is "data", Q is "output"

- Also called "d-type Flip-Flop"

Spring 2011

EECS150 lec04-SDS-review2

Page 5

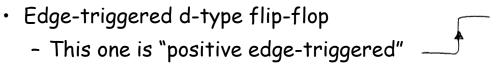

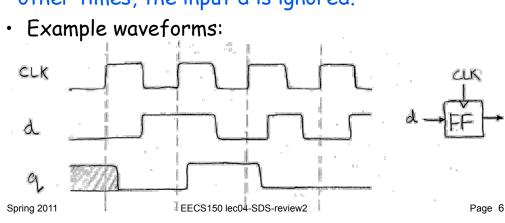

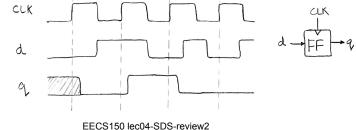

## Flip-flop Timing

• "On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored."

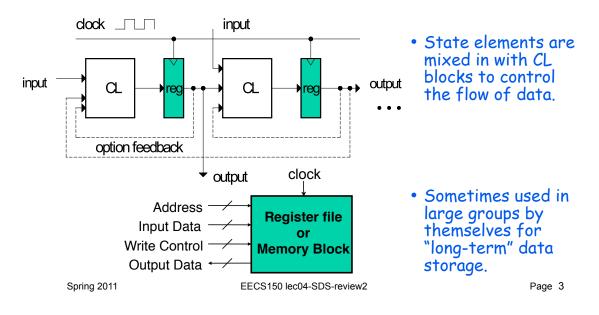

#### **Uses for State Elements**

- 1) As a place to store values for some indeterminate amount of time:

- Register files (like \$1-\$31 on the MIPS)

- Memory (caches, and main memory)

- 2) Help control the flow of information between combinational logic blocks.

- State elements are used to hold up the movement of information at the inputs to combinational logic blocks and allow for orderly passage.

```

Spring 2011

```

EECS150 lec04-SDS-review2

Page 7

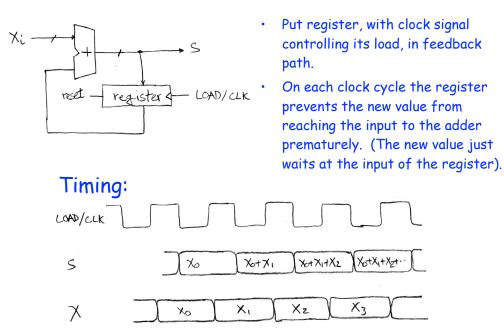

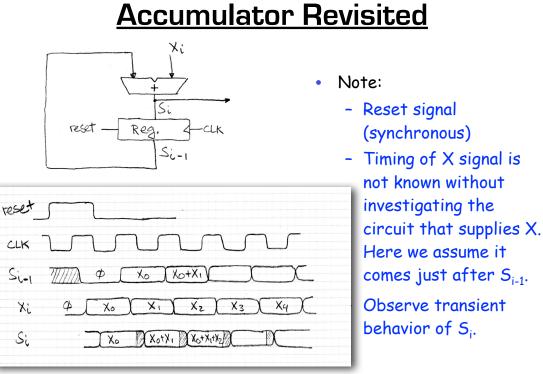

## Accumulator Circuit Example

Assume X is a vector of N integers, presented to the input of our accumulator circuit one at a time (one per clock cycle), so that after N clock cycles, S hold the sum of all N numbers.

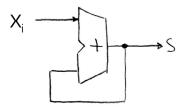

$\chi_i \rightarrow sum \rightarrow S$

S=0; Repeat N times S = S + X;

We need something like this:

- But not quite.

- Need to use the clock signal to hold up the feedback to match up with the input signal.

#### **Accumulator Circuit**

Spring 2011

EECS150 lec04-SDS-review2

Page 9

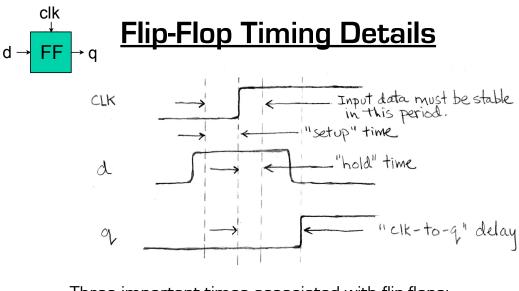

#### **Register Details (again)**

• A n-bit wide register is nothing but a set of flip-flops (1-bit wide registers) with a common load/clk signal.

• A flip-flop captures its input on the edge of the clock (rising edge in this case - positive edge flip-flop). The new input appears at the output after a short delay.

Three important times associated with flip-flops:

setup time hold time

clock-to-q delay.

Spring 2011

EECS150 lec04-SDS-review2

Page 11

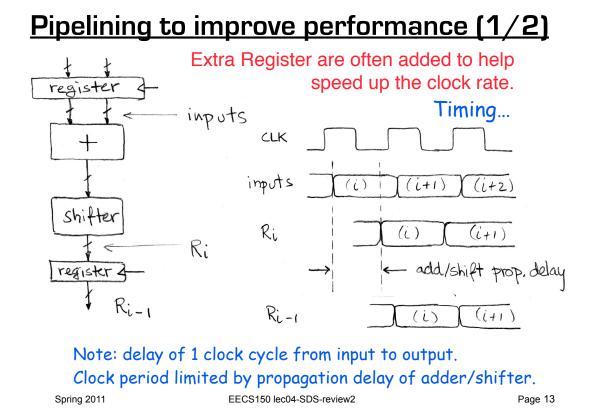

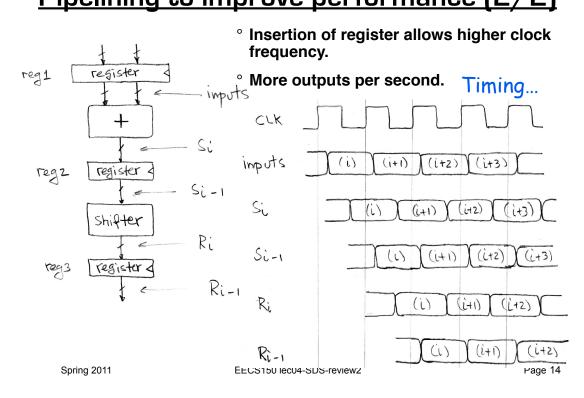

# Pipelining to improve performance (2/2)

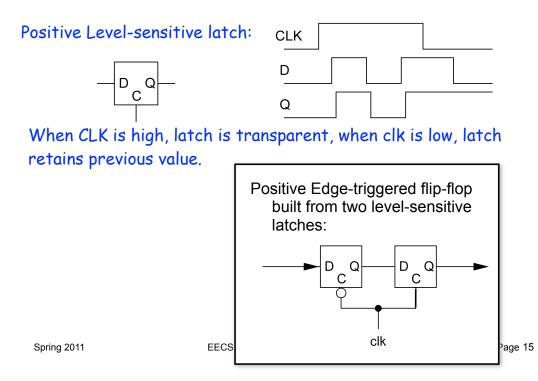

#### Level-sensitive Latch

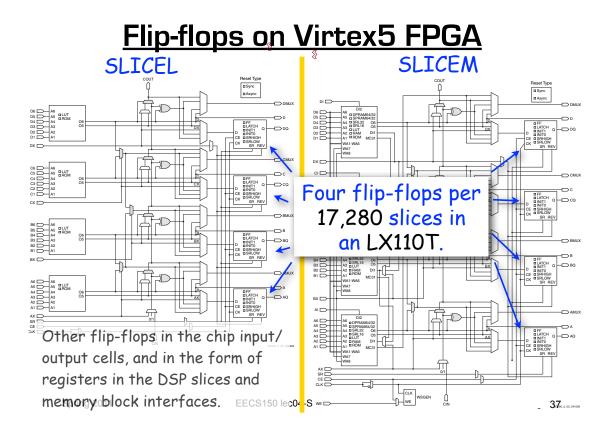

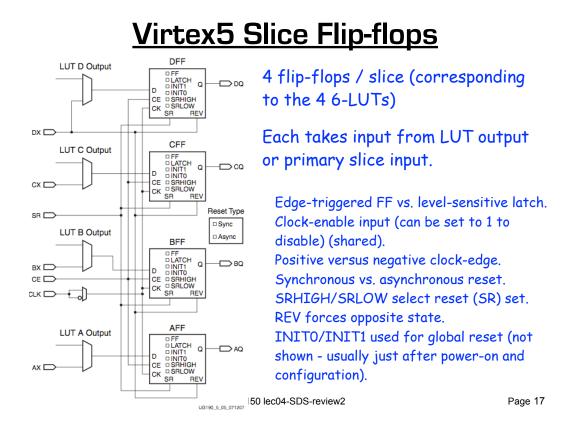

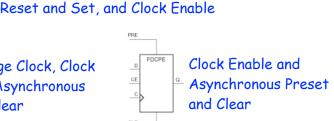

## Virtex5 Flip-flops "Primitives"

Provided by the CAD tools. This maps to single slice flip-flop.

Negative-Clock Edge, Synchronous

| Logic Table |        |    |   |   |    |        |  |

|-------------|--------|----|---|---|----|--------|--|

| Ir          | Inputs |    |   |   |    | Output |  |

| R           | s      | CE | D | С | Q  |        |  |

| 1           | -      | -  | - | t | 0  |        |  |

| 0           | 1      | -  | - | t | 1  |        |  |

| 0           | 0      | 0  | - | - | No | Change |  |

| 0           | 0      | 1  | 1 | Ť | 1  |        |  |

| 0           | 0      | 1  | 0 | t | 0  |        |  |

| -           |        | _  |   |   | _  | _      |  |

Negative-Edge Clock, Clock Enable, and Asynchronous Preset and Clear

Spring 2011

FDCPE\_1 D CE

PRE

CLR

EECS150 lec04-SDS-review2