###

### Lecture #13: Combinational Logic & Gates

2004-07-12

## **Andy Carle**

CS 61C L13 Combinational Logic (1)

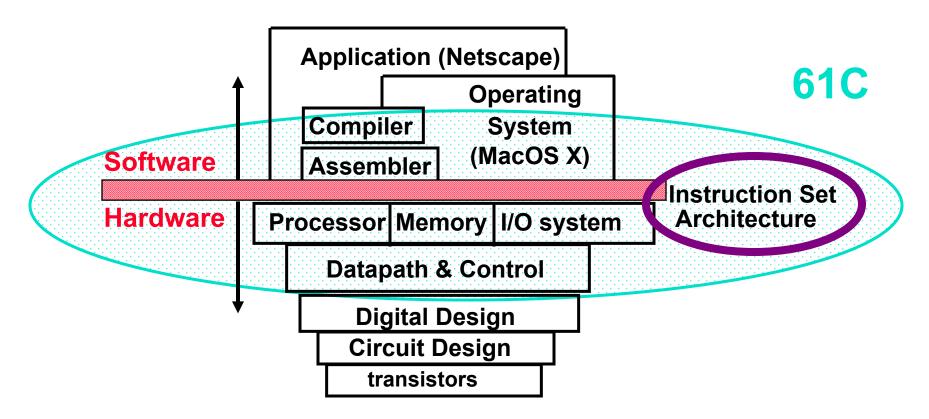

## What are "Machine Structures"?

# Coordination of many *levels of abstraction*

### We'll investigate lower abstraction layers! (contract between HW & SW)

CS 61C L13 Combinational Logic (2)

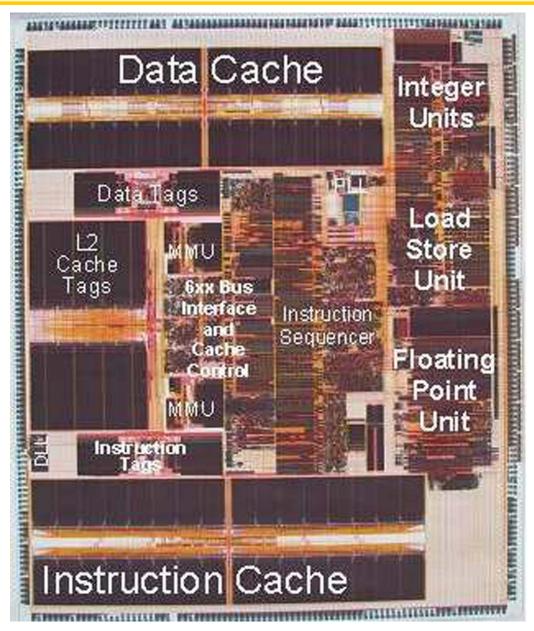

### Physical Hardware - PowerPC 750

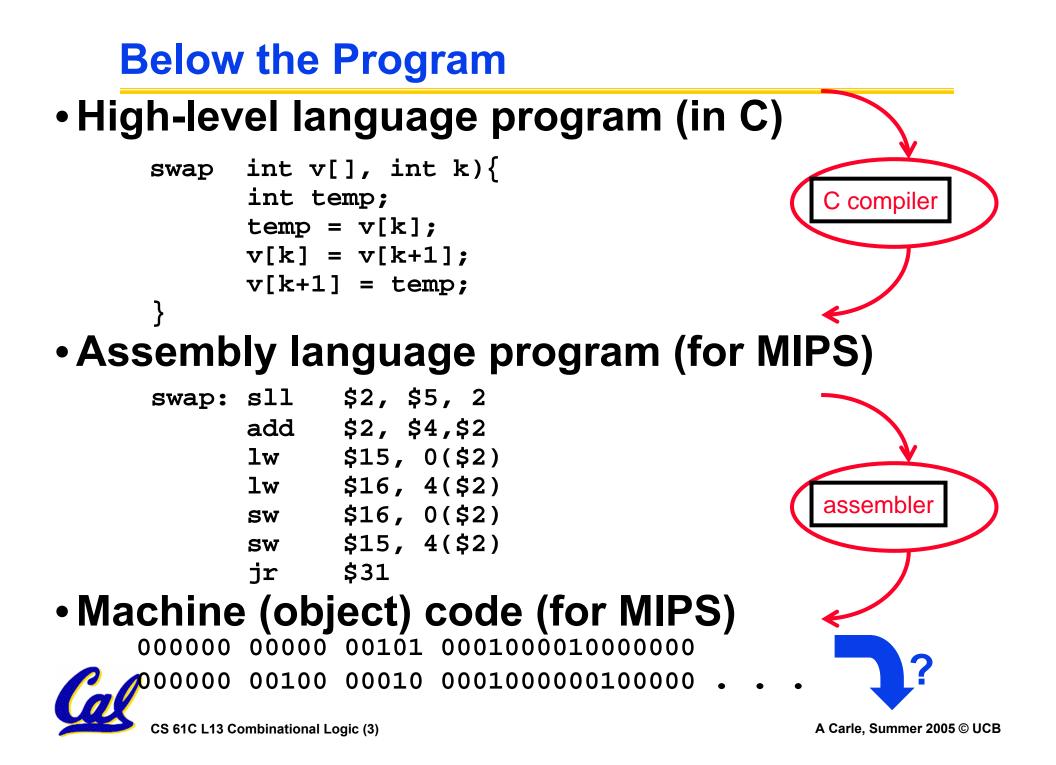

**Digital Design Basics (1/2)**

- Next 3 weeks: we'll study how a modern processor is built starting with basic logic elements as building blocks.

- Why study logic design?

- Understand what processors can do fast and what they can't do fast (avoid slow things if you want your code to run fast!)

- Background for more detailed hardware courses (CS 150, CS 152)

# **Digital Design Basics (2/2)**

- ISA is very important abstraction layer

- Contract between HW and SW

- Can you peek across abstraction?

- Can you depend "across abstraction"?

- Voltages are analog, quantized to 0/1

- Circuit delays are fact of life

- Two types

- Stateless Combinational Logic (&,|,~)

- State circuits (e.g., registers)

## Outline

- Truth Tables

- Transistors

- Logic Gates

- Combinational Logic

- Boolean Algebra

### **Truth Tables (1/6)**

|                   |                       | a | b | С | d | у          |

|-------------------|-----------------------|---|---|---|---|------------|

|                   | _                     | 0 | 0 | 0 | 0 | F(0,0,0,0) |

|                   |                       | 0 | 0 | 0 | 1 | F(0,0,0,1) |

|                   |                       | 0 | 0 | 1 | 0 | F(0,0,1,0) |

|                   |                       | 0 | 0 | 1 | 1 | F(0,0,1,1) |

| a                 |                       | 0 | 1 | 0 | 0 | F(0,1,0,0) |

|                   |                       | 0 | 1 | 0 | 1 | F(0,1,0,1) |

|                   |                       | 0 | 1 | 1 | 0 | F(0,1,1,0) |

| C                 | $\widetilde{\langle}$ | 0 | 1 | 1 | 1 | F(0,1,1,1) |

|                   | ~                     | 1 | 0 | 0 | 0 | F(1,0,0,0) |

| $d \rightarrow 1$ |                       | 1 | 0 | 0 | 1 | F(1,0,0,1) |

|                   |                       | 1 | 0 | 1 | 0 | F(1,0,1,0) |

|                   |                       | 1 | 0 | 1 | 1 | F(1,0,1,1) |

|                   |                       | 1 | 1 | 0 | 0 | F(1,1,0,0) |

|                   |                       | 1 | 1 | 0 | 1 | F(1,1,0,1) |

|                   |                       | 1 | 1 | 1 | 0 | F(1,1,1,0) |

|                   |                       | 1 | 1 | 1 | 1 | F(1,1,1,1) |

|                   |                       |   |   |   |   |            |

CS 61C L13 Combinational Logic (8)

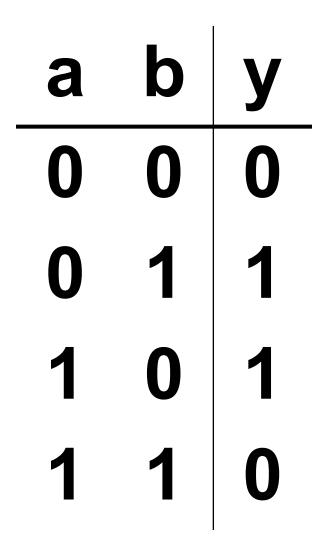

## TT (2/6) Ex #1: 1 iff one (not both) a,b=1

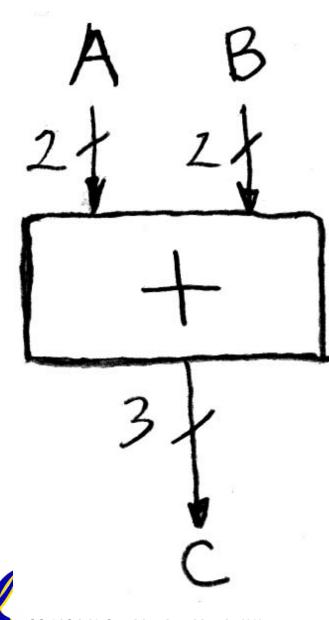

## TT (3/6): Example #2: 2-bit adder

| А        | В        | C             |

|----------|----------|---------------|

| $a_1a_0$ | $b_1b_0$ | $c_2 c_1 c_0$ |

| 00       | 00       | 000           |

| 00       | 01       | 001           |

| 00       | 10       | 010           |

| 00       | 11       | 011           |

| 01       | 00       | 001           |

| 01       | 01       | 010           |

| 01       | 10       | 011           |

| 01       | 11       | 100           |

| 10       | 00       | 010           |

| 10       | 01       | 011           |

| 10       | 10       | 100           |

| 10       | 11       | 101           |

| 11       | 00       | 011           |

| 11       | 01       | 100           |

| 11       | 10       | 101           |

| 11       | 11       | 110           |

CS 61C L13 Combinational Logic (10)

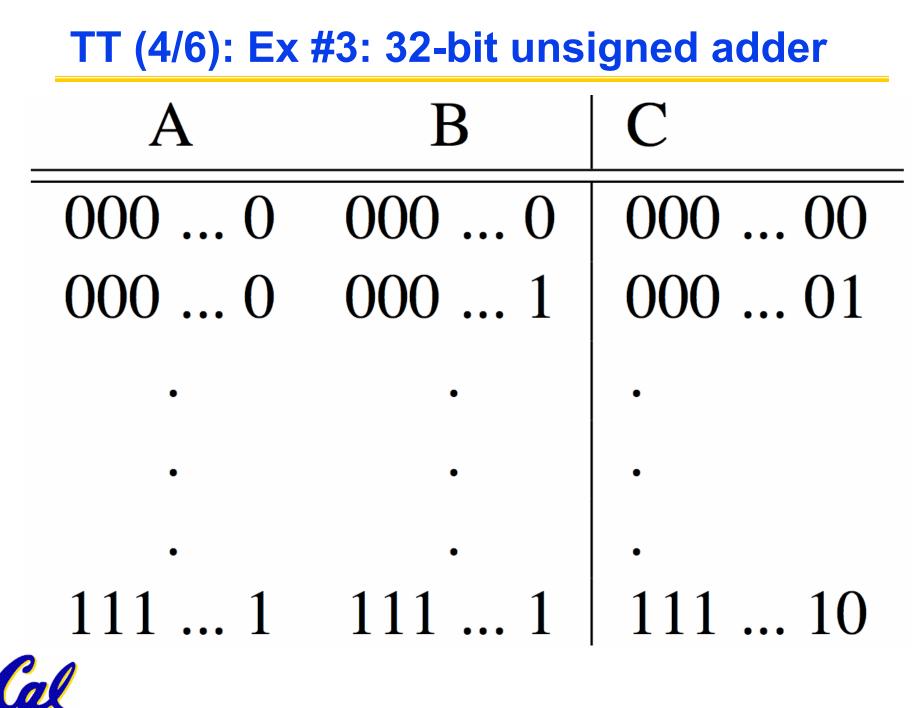

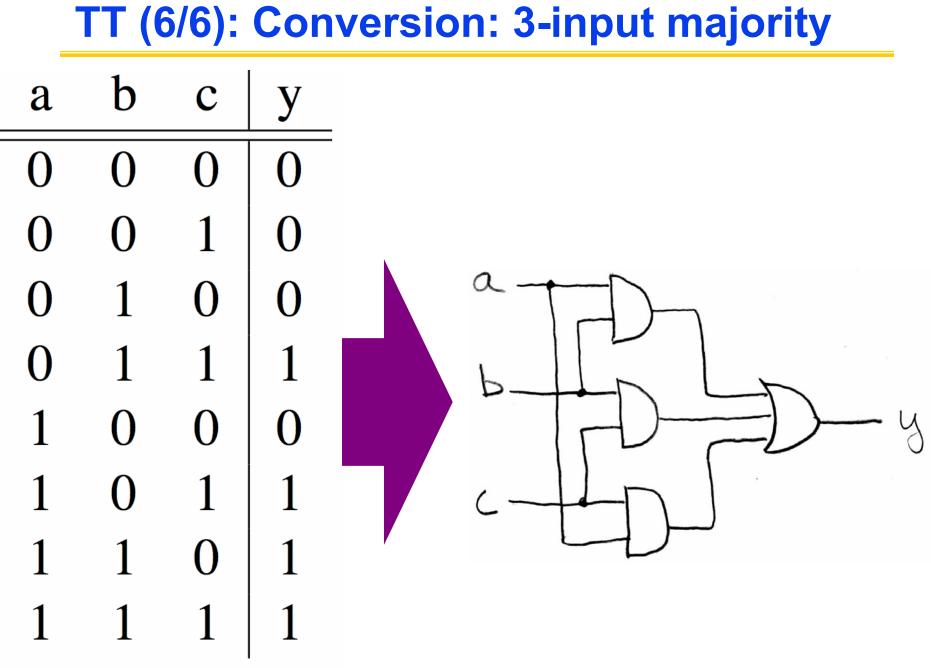

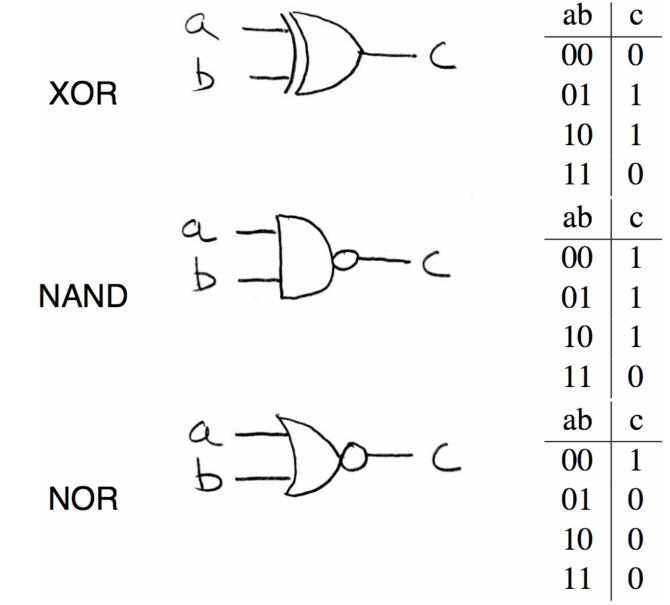

## TT (5/6): Conversion: 3-input majority

| a | b | C | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

# Transistors (1/3)

#### **CMOSFET Transistors:**

- \* Physically exist!

- \* Voltages are quantized

- \* Only 2 Types:

- P-channel:

- 0 on gate -> pull up (1)

- N-channel:

- 1 on gate -> pull down (0)

#### \* Undriven otherwise.

# Transistors (2/3)

**CMOSFET Transistors:**

\* have delay and require power

\* can be combined to perform logical operations and maintain state.

- logical operations will be our starting point for digital design

- state tomorrow

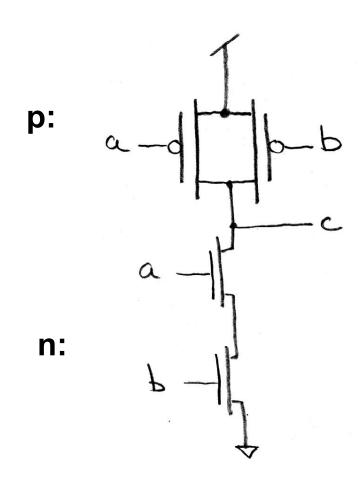

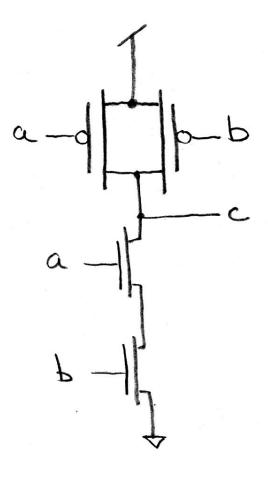

## Transistors (3/3): CMOS -> Nand

Logic Gates (1/4)

- Transistors are too low level

- Good for measuring performance, power.

- Bad for logical design / analysis

- Gates are collections of transistors wired in a certain way

- Can represent and reason about gates with truth tables and Boolean algebra

- We will mainly review the concepts of truth tables and Boolean algebra in this class. It is assumed that you've seen these before.

Section B.2 in the textbook has a review

CS 61C L13 Combinational Logic (17)

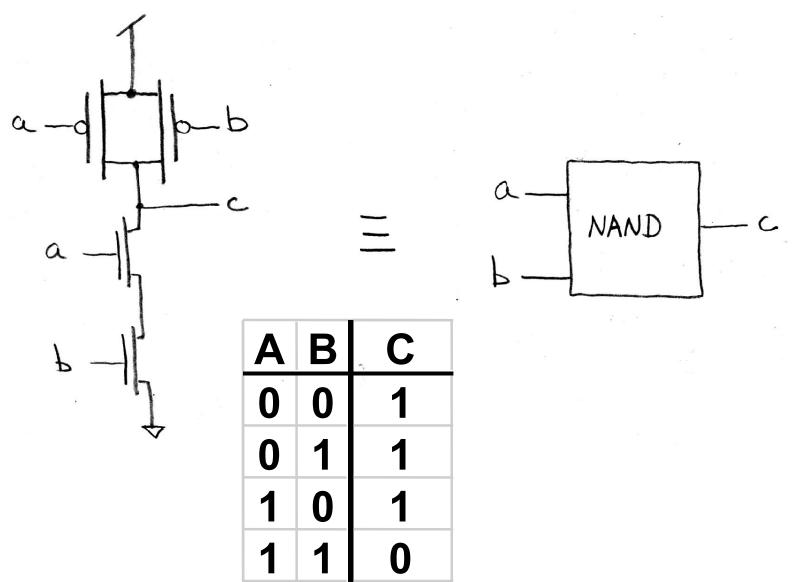

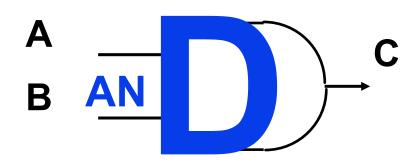

### Logic Gates (2/4)

## **AND Gate**

### Definition

CS 61C L13 Combinational Logic (19)

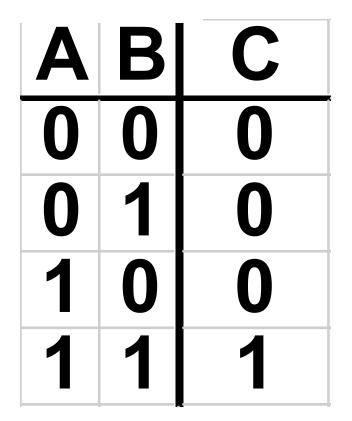

### Logic Gates (4/4)

**Boolean Algebra (1/7)**

- George Boole, 19<sup>th</sup> Century mathematician

- Developed a mathematical system (algebra) involving logic, later known as "Boolean Algebra"

- Primitive functions: AND, OR and NOT

- The power of BA is there's a one-to-one correspondence between circuits made up of AND, OR and NOT gates and equations in BA

BA (2/7): e.g., majority circuit

$y = a \cdot b + a \cdot c + b \cdot c$

y = ab + ac + bc

## BA (3/7):Laws of Boolean Algebra

| $x\cdot \overline{x}=0$                         | $x + \overline{x} = 1$                               |

|-------------------------------------------------|------------------------------------------------------|

| $x \cdot 0 = 0$                                 | x + 1 = 1                                            |

| $x \cdot 1 = x$                                 | x + 0 = x                                            |

| $x \cdot x = x$                                 | x + x = x                                            |

| $x \cdot y = y \cdot x$                         | x + y = y + x                                        |

| (xy)z = x(yz)                                   | (x+y) + z = x + (y+z)                                |

| x(y+z) = xy + xz                                | x + yz = (x + y)(x + z)                              |

| xy + x = x                                      | (x+y)x = x                                           |

| $\overline{x\cdot y}=\overline{x}+\overline{y}$ | $\overline{(x+y)} = \overline{x} \cdot \overline{y}$ |

complementarity laws of 0's and 1's identities idempotent law commutativity associativity distribution uniting theorem DeMorgan's Law

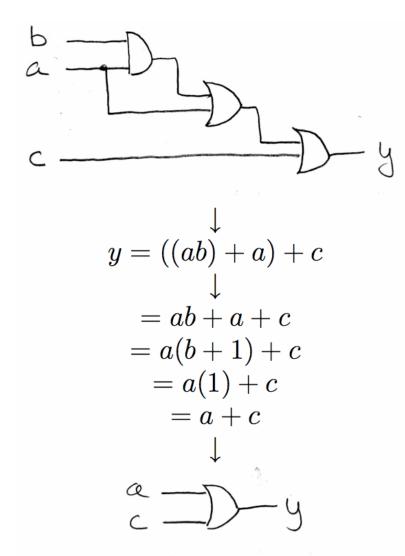

# **BA (4/7): Circuit & Algebraic Simplification**

original circuit

equation derived from original circuit

algebraic simplification

simplified circuit

## **BA (5/7): Simplification Example**

$$y = ab + a + c$$

=  $a(b+1) + c$  distribution, identity

=  $a(1) + c$  law of 1's

=  $a + c$  identity

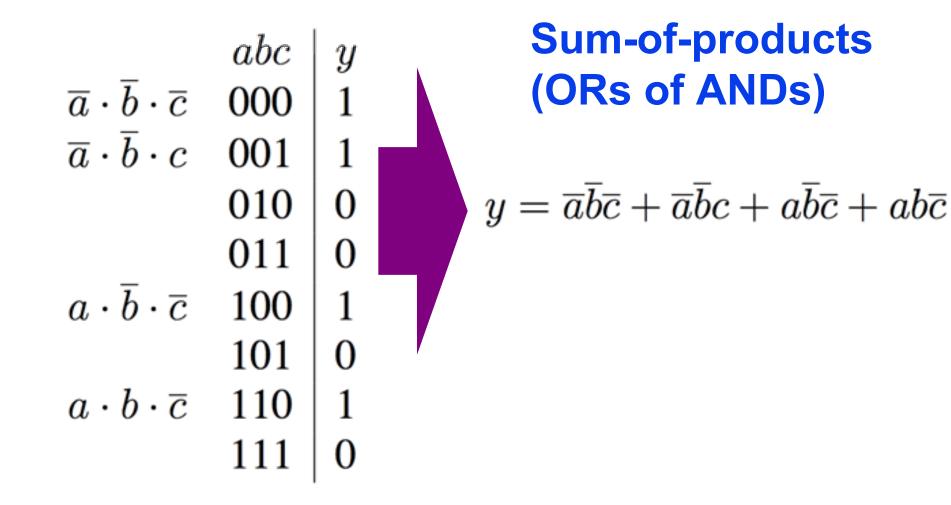

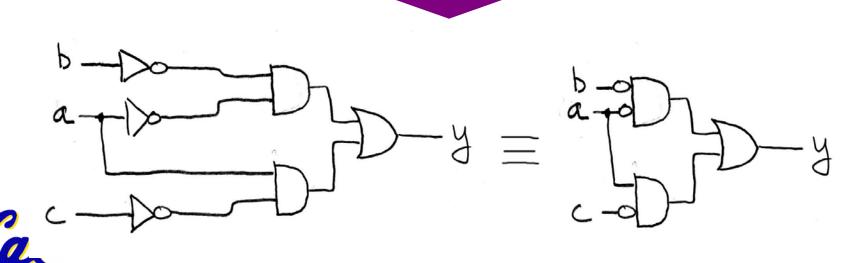

**BA (6/7): Canonical forms (1/2)**

## **BA (7/7): Canonical forms (2/2)**

$$y = \overline{a}\overline{b}\overline{c} + \overline{a}\overline{b}c + a\overline{b}\overline{c} + ab\overline{c}$$

$$= \overline{a}\overline{b}(\overline{c} + c) + a\overline{c}(\overline{b} + b) \quad distribution$$

$$= \overline{a}\overline{b}(1) + a\overline{c}(1) \quad complementarity$$

$$= \overline{a}\overline{b} + a\overline{c} \quad identity$$

CS 61C L13 Combinational Logic (27)

**Combinational Logic**

A *combinational* logic block is one in which the output is a function only of its current input.

- Combinational logic cannot have memory.

- Everything we've seen so far is CL

- CL will have delay ( f(transistors) )

- More later.

- A.  $(a+b) \cdot (a+b) = b$

- **B.** N-input gates can be thought of as cascaded 2-input gates. I.e.,  $(a \land bc \land d \land e) = a \land (bc \land (d \land e))$ where  $\Delta$  is one of AND, OR, XOR, NAND

- C. You can use NOR(s) with clever wiring to simulate AND, OR, & NOT

61C L13 Combinational Logic (29)

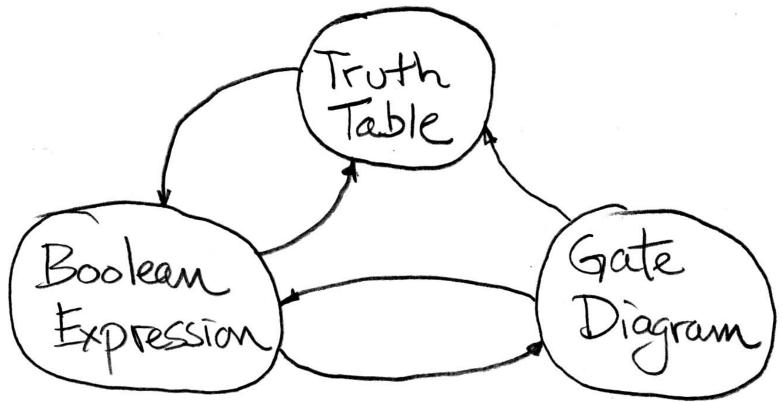

"And In conclusion..."

• Use this table and techniques we learned to transform from 1 to another

CS 61C L13 Combinational Logic (30)