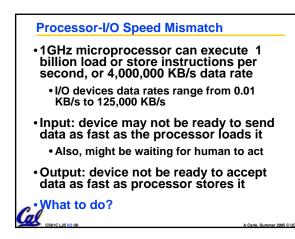

| • I/O Speed: byt<br>(from mouse to | es trans<br>Gigabit L/ | ferred per<br>AN: 10-milli | second<br>on-to-1)      |

|------------------------------------|------------------------|----------------------------|-------------------------|

| Device                             | Behavior               | Partner                    | Data Rate<br>(KBytes/s) |

| Keyboard                           | Input                  | Human                      | 0.01                    |

| Mouse                              | Input                  | Human                      | 0.02                    |

| Voice output                       | Output                 | Human                      | 5.00                    |

| Floppy disk                        | Storage                | Machine                    | 50.00                   |

| Laser Printer                      | Output                 | Human                      | 100.00                  |

| Magnetic Disk                      | Storage                | Machine                    | 10,000.00               |

| Wireless Network                   | l or O                 | Machine                    | 10,000.00               |

| Graphics Display                   | Output                 | Human                      | 30,000.00               |

| Wired LAN Network                  | l or O                 | Machine                    | 125,000.00              |

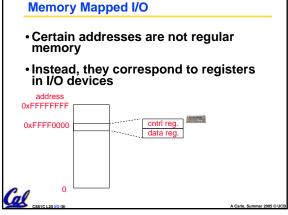

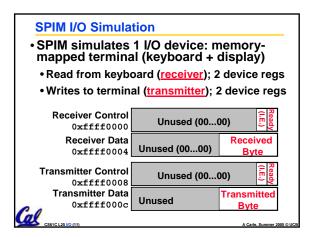

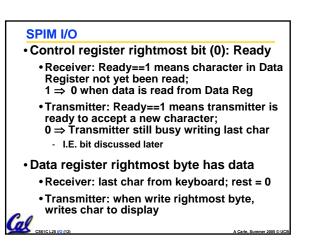

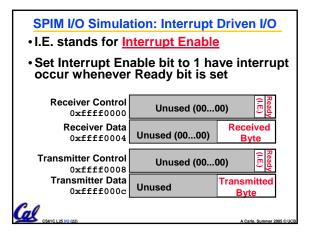

| I/O Examp<br>• Input: Read | le<br>from keyboard into \$v0                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Waitloop:                  | <pre>lui \$t0, 0xffff #ffff0000 lw \$t1, 0(\$t0) #control andi \$t1,\$t1,0x1 beq \$t1,\$zero, Waitloop lw \$v0, 4(\$t0) #data</pre>  |

| Output: Writ               | te to display from \$a0                                                                                                              |

| Waitloop:                  | <pre>lui \$t0, 0xffff #ffff0000 lw \$t1, 8(\$t0) #control andi \$t1,\$t1,0x1 beq \$t1,\$zero, Waitloop sw \$a0, 12(\$t0) #data</pre> |

| • Processor w              | vaiting for I/O called " <u>Polling</u> "                                                                                            |

| "Ready" bit                | from processor's point of view!                                                                                                      |

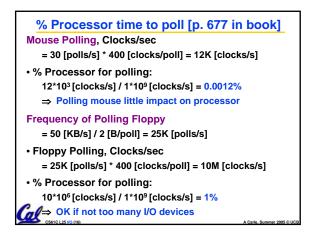

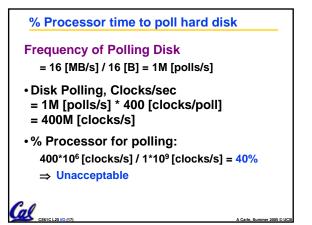

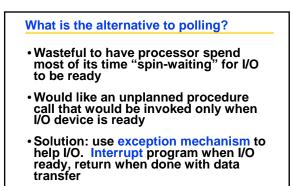

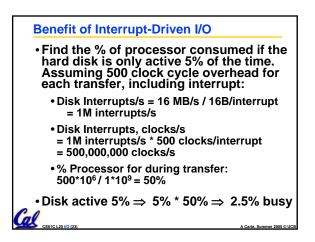

## Cost of Polling? • Assume for a processor with a 1GHz clock it takes 400 clock cycles for a polling operation (call polling routine, accessing the device, and returning). Determine % of processor time for polling • Mouse: polled 30 times/sec so as not to miss user movement • Floppy disk: transfers data in 2-Byte units and has a data rate of 50 KB/second. No data transfer can be missed. • Hard disk: transfers data in 16-Byte chunks and can transfer at 16 MB/second. Again, no transfer can be missed.

Cal CS61C L25

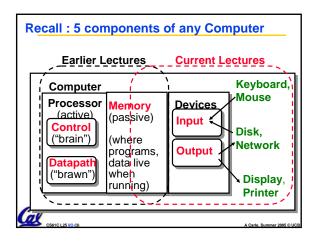

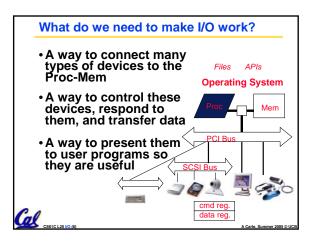

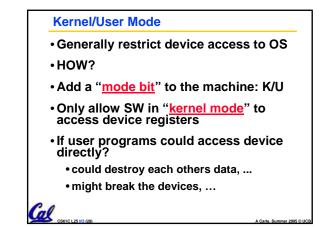

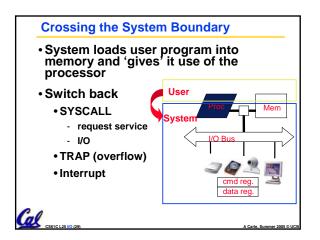

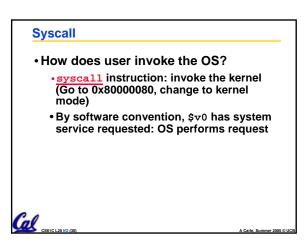

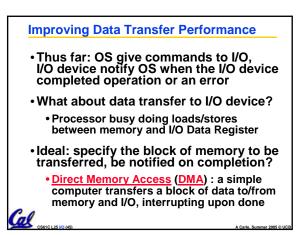

### **OS: I/O Requirements**

#### • The OS must be able to prevent:

- The user program from communicating with the I/O device directly

- If user programs could perform I/O directly:

No protection to the shared I/O resources

- •3 types of communication are required:

- The OS must be able to give commands to the I/O devices

- The I/O device notify OS when the I/O device has completed an operation or an error

- Data transfers between memory and I/O device

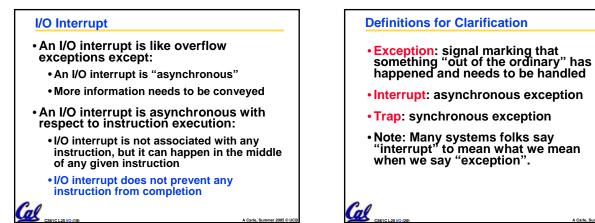

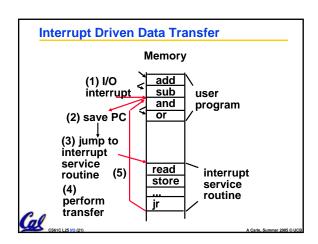

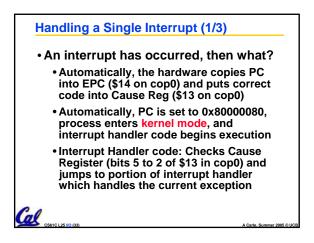

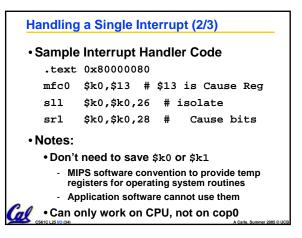

# Handling a Single Interrupt (3/3)

- When the interrupt is handled, copy the value from EPC to the PC.

- Call instruction **rfe** (return from exception), which will return process to user mode and reset state to the way it was before the interrupt

- What about multiple interrupts?

Cal

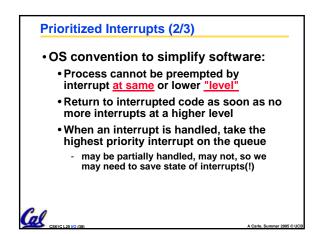

#### **Multiple Interrupts**

• Problem: What if we're handling an Overflow interrupt and an I/O interrupt (printer ready, for example) comes in?

#### • Options:

Cal

- drop any conflicting interrupts: unrealistic, they may be important

- simultaneously handle multiple interrupts: unrealistic, may not be able to synchronize them (such as with multiple I/O interrupts)

- queue them for later handling: sounds good

Cal

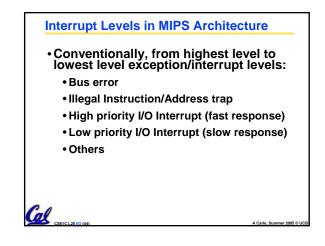

- Question: Suppose we're dealing with a computer running a nuclear facility. What if we're handling an Overflow interrupt and a Nuclear Meltdown Imminent interrupt comes in?

- Answer: We need to categorize and prioritize interrupts so we can handle them in order of urgency: emergency vs. luxury.

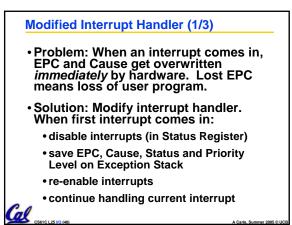

# Modified Interrupt Handler (2/3) • When next (or any later) interrupt comes in:

- interrupt the first one

- disable interrupts (in Status Register)

- save EPC, Cause, Status and Priority Level (and maybe more) on Exception Stack

- determine whether new one preempts old one

- if no, re-enable interrupts and continue with old one

- if yes, may have to save state for the old one, then re-enable interrupts, then handle new one

Modified Interrupt Handler (3/3)

Notes:

Cal

- Disabling interrupts is dangerous

- So we disable them for as short a time as possible: long enough to save vital info onto Exception Stack

- This new scheme allows us to handle many interrupts effectively.

| Example: code in DMA controller                                    |

|--------------------------------------------------------------------|

| <ul> <li>DMA code from Disk Device to Memory</li> </ul>            |

| .data                                                              |

| Count: .word 4096                                                  |

| Start: .space 4096<br>.text                                        |

| Initial: lw \$s0, Count # No. chars<br>la \$s1, Start # @next char |

| Wait: lw \$s2, DiskControl                                         |

| andi \$\$2,\$\$2,1 # select Ready                                  |

| beg \$s2,\$0,Wait # spinwait                                       |

| lb \$t0, DiskData # get byte                                       |

| sb \$t0, 0(\$s1) # transfer                                        |

| addiu \$s0,\$s0,-1 # Count                                         |

| addiu \$s1,\$s1,1 # Start++                                        |

| bne \$s0,\$0,Wait # next char                                      |

| DMA "computer" in parallel with CPU                                |

| CS61C L25 VO (46) A Carle, Summer 2005 © U(                        |

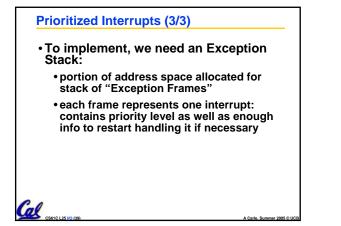

#### Details not covered

- MIPS has a field to record all pending interrupts so that none are lost while interrupts are off; in Cause register

- The Interrupt Priority Level that the CPU is running at is set in memory

- MIPS has a field in that can mask interrupts of different priorities to implement priority levels; in Status register

- MIPS has limited nesting of saving KU,IE bits to recall in case higher priority interrupts; in Status Register

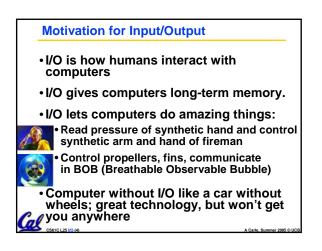

# "And in conclusion..." • I/O gives computers their 5 senses • I/O speed range is 100-million to one

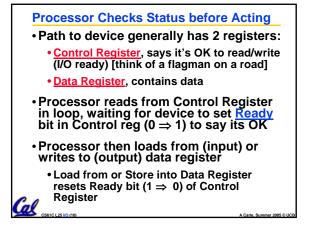

- Processor speed means must synchronize with I/O devices before use

- Polling works, but expensive

processor repeatedly queries devices

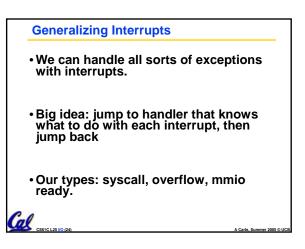

- Interrupts works, more complex

devices causes an exception, causing OS to run and deal with the device

- I/O control leads to Operating Systems

Cal