####

#### Lecture #15: State 2 and Blocks

2006-07-24

**Andy Carle**

# Outline

- Review

- Clocks

- •FSMs

# Combinational Logic Blocks

# **Review (1/3)**

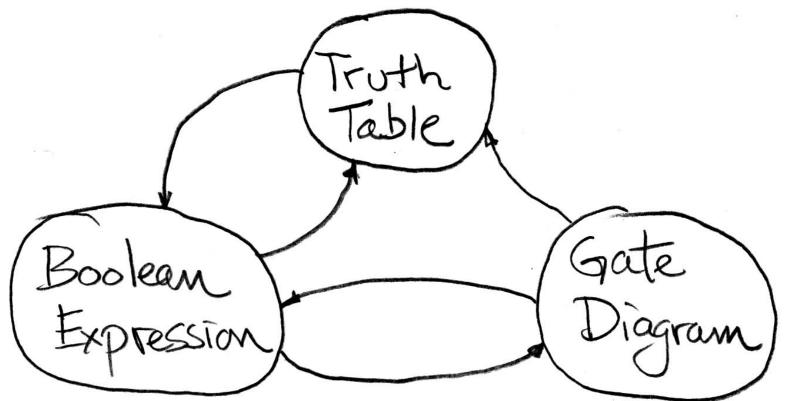

• Use this table and techniques we learned to transform from 1 to another

A Carle, Summer 2006 © UCB

CS 61C L15 State & Blocks (3)

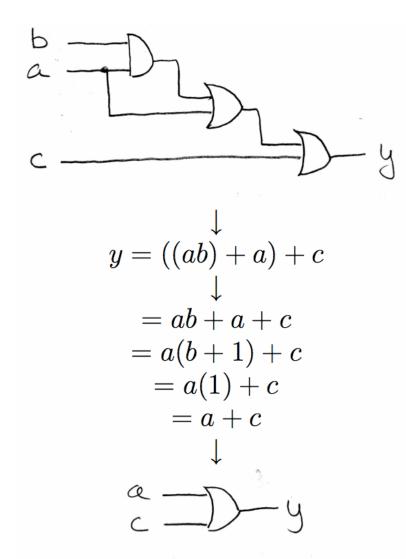

# (2/3): Circuit & Algebraic Simplification

original circuit

equation derived from original circuit

algebraic simplification

simplified circuit

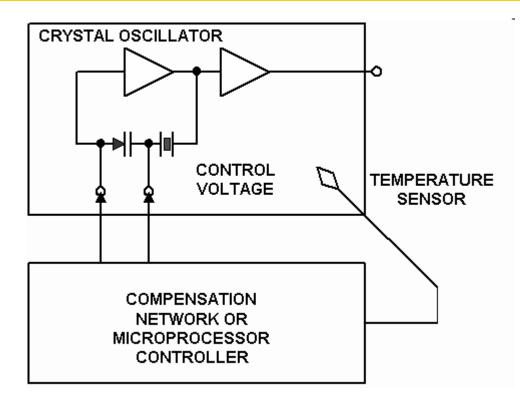

#### • Need a regular oscillator:

### • Wire up three inverters in feedback?...

- Not stable enough

- •1->0 and 0->1 transitions not symmetric.

# Solution: Base oscillation on a natural resonance. But of what?

### Controller puts AC across crystal:

- At anything but resonant freqs → destructive interference

- Cal

- Resonant freq → CONSTRUCTIVE!

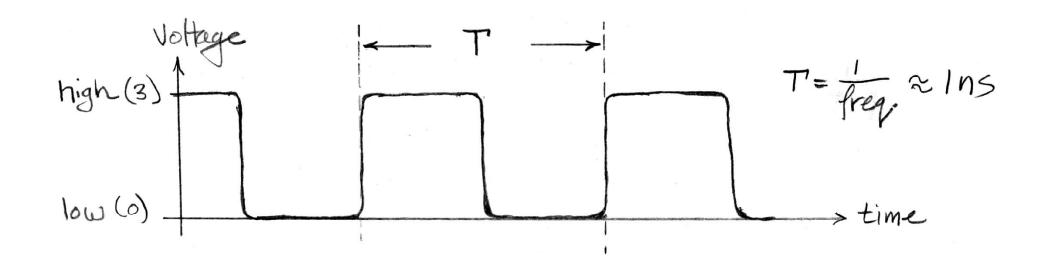

#### **Signals and Waveforms: Clocks**

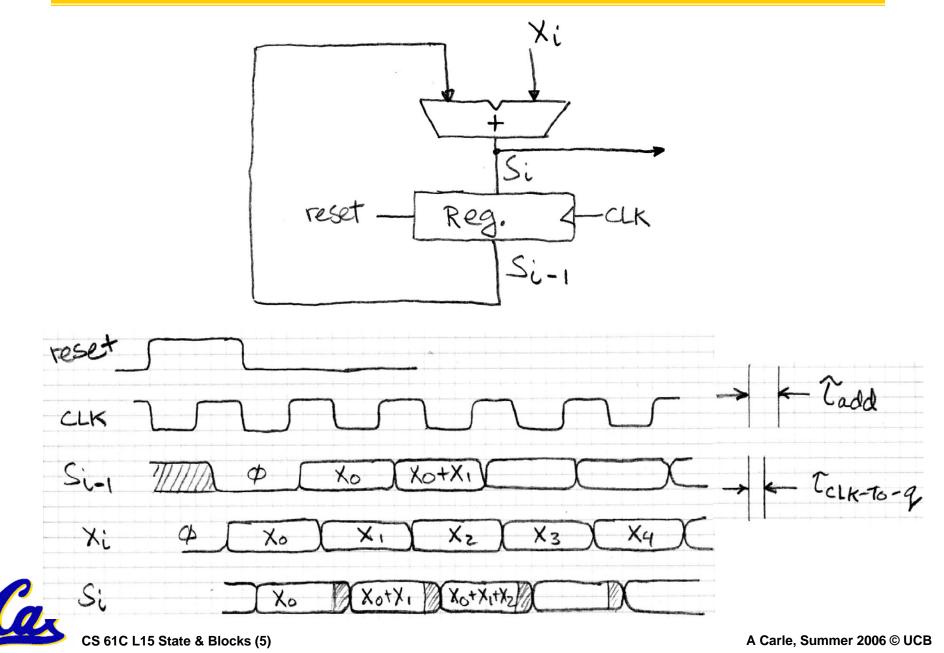

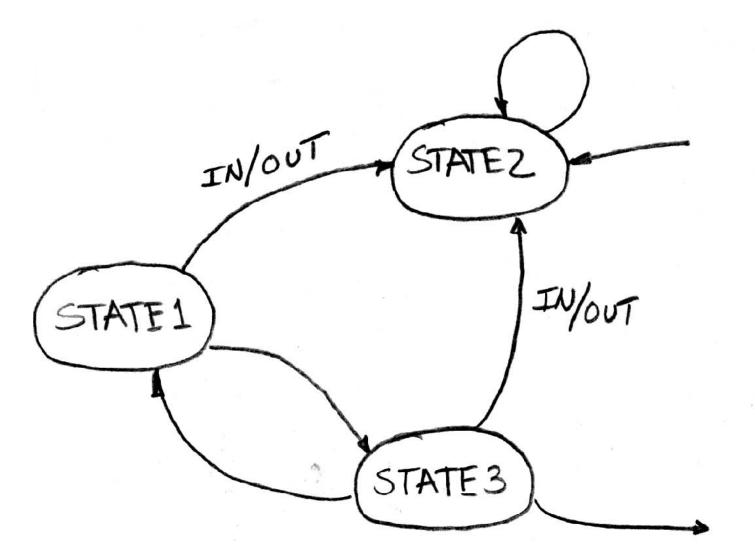

#### With state elements, we can build circuits whose output is a function of inputs and current state.

State transitions will occur on clock edges.

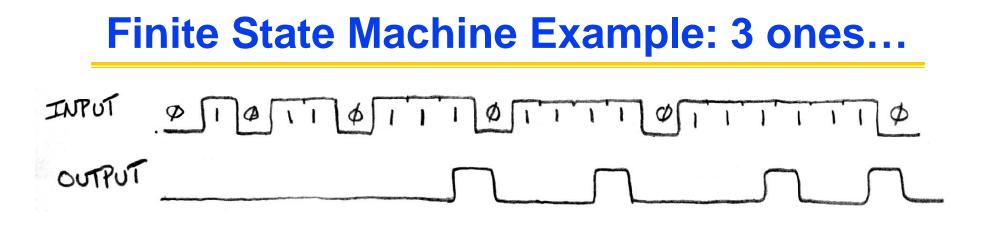

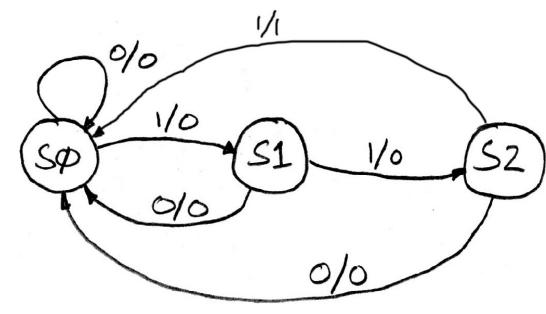

#### **Finite State Machines Introduction**

Draw the FSM...

| PS | Input | NS | Output |

|----|-------|----|--------|

| 00 | 0     | 00 | 0      |

| 00 | 1     | 01 | 0      |

| 01 | 0     | 00 | 0      |

| 01 | 1     | 10 | 0      |

| 10 | 0     | 00 | 0      |

| 10 | 1     | 00 | 1      |

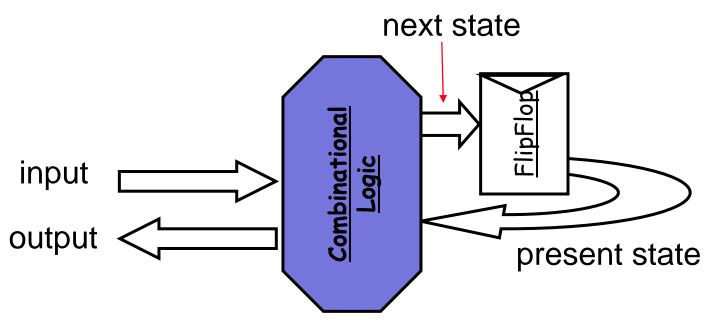

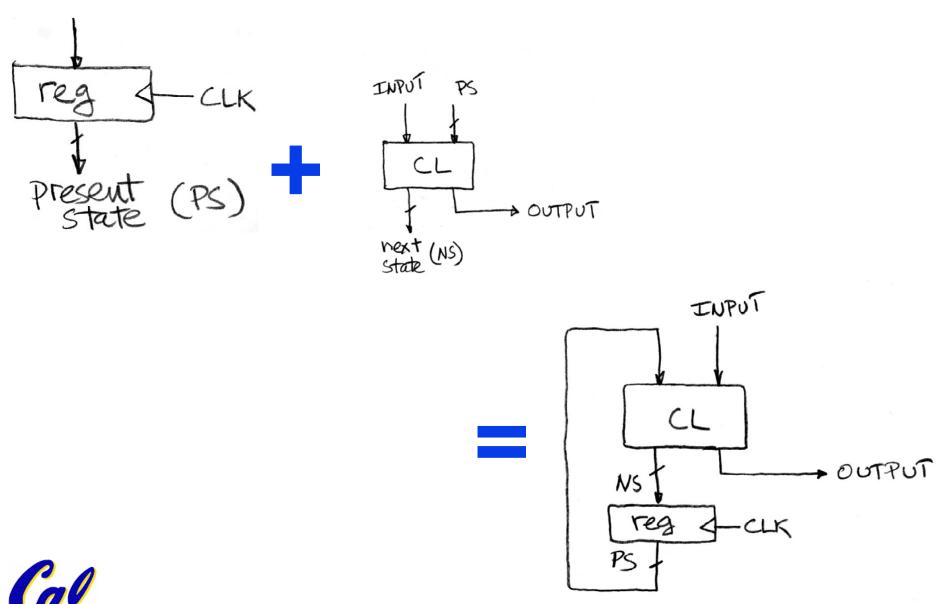

#### Hardware Implementation of FSM

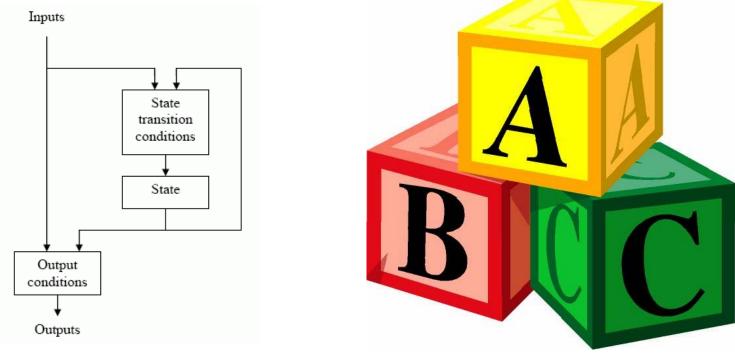

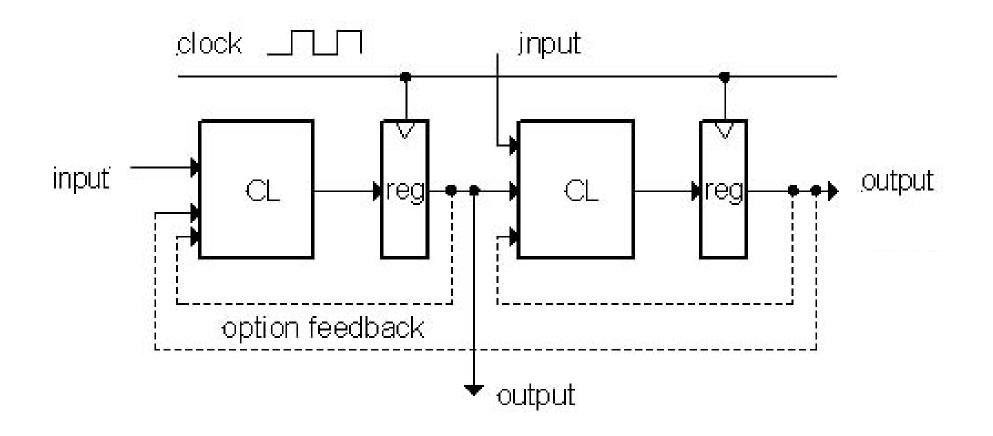

### **General Model for Synchronous Systems**

- Two bit counter:

- •4 States: 0, 1, 2, 3

- When input c is high, go to next state

- (3->0)

- When input is low, don't change state

- On the transition from state 3 to state 0, output a 1. At all other times, output 0.

# **CL Blocks**

- Let's use our skills to build some CL blocks:

- Multiplexer (mux)

- Adder

- ALU

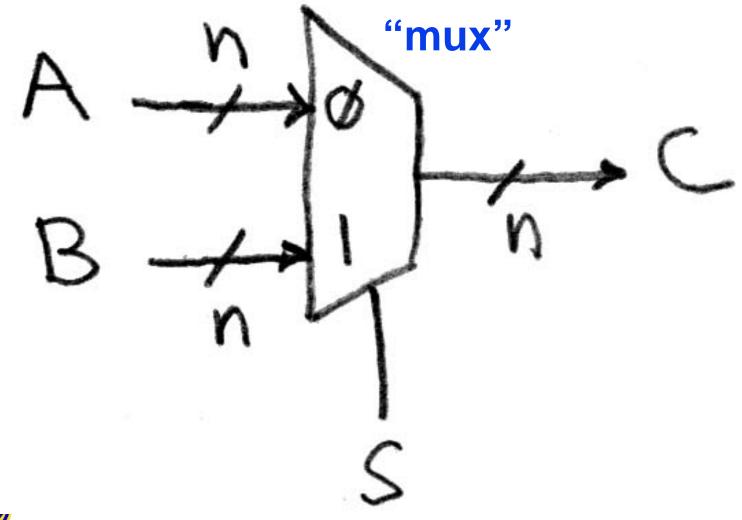

#### Data Multiplexor (here 2-to-1, n-bit-wide)

#### N instances of 1-bit-wide mux

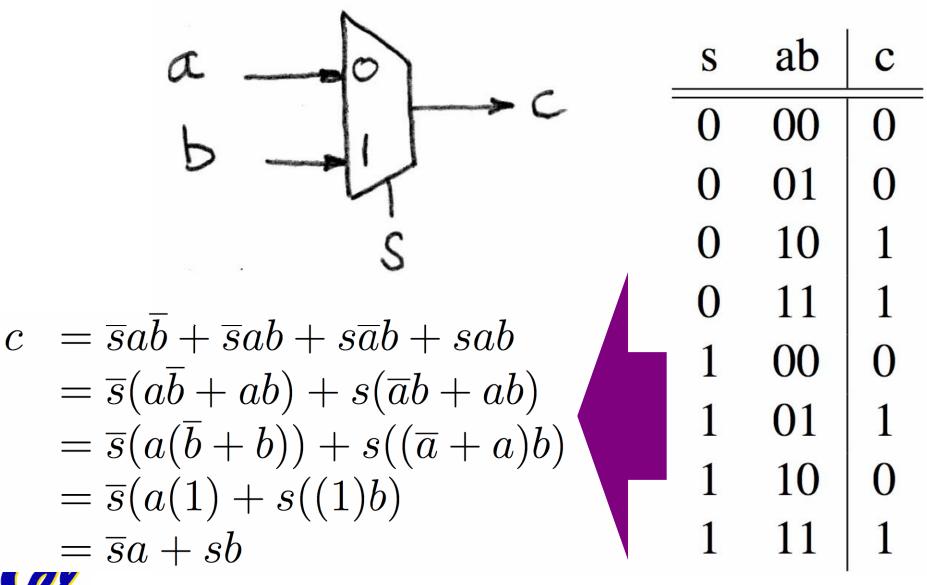

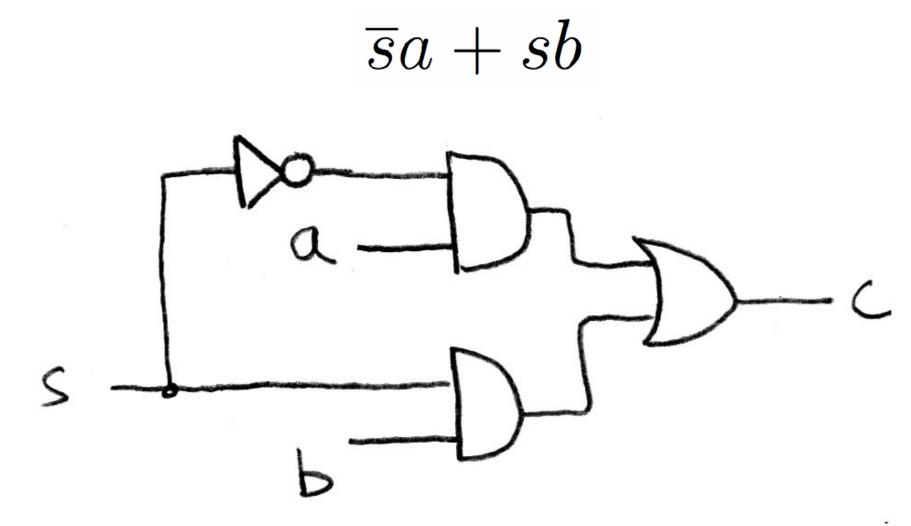

#### How do we build a 1-bit-wide mux?

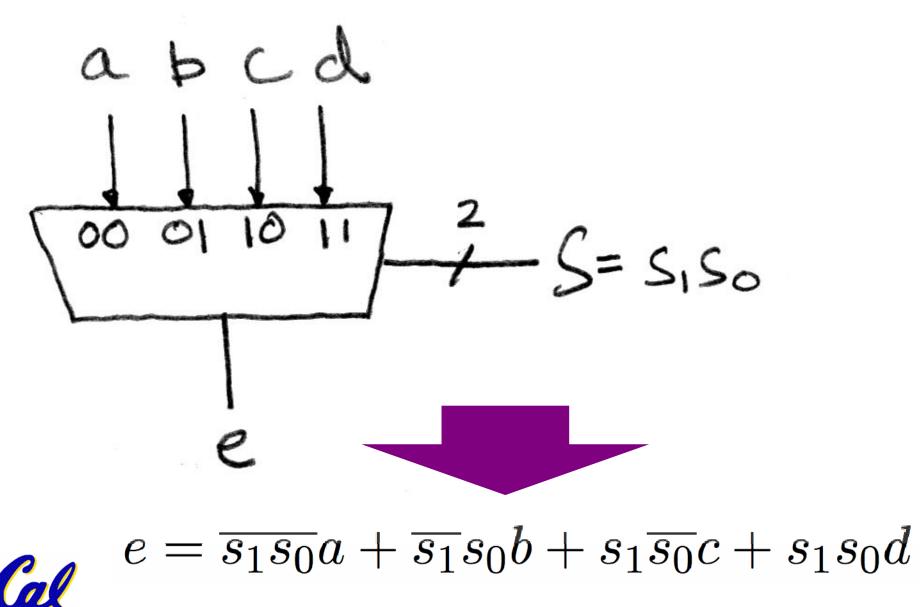

**4-to-1 Multiplexor?**

CS 61C L15 State & Blocks (19)

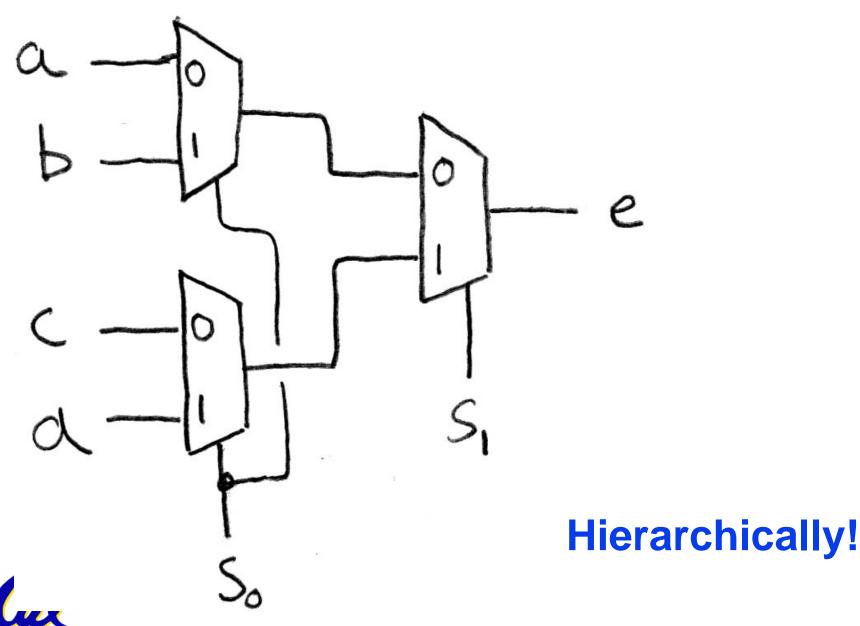

#### **An Alternative Approach**

CS 61C L15 State & Blocks (20)

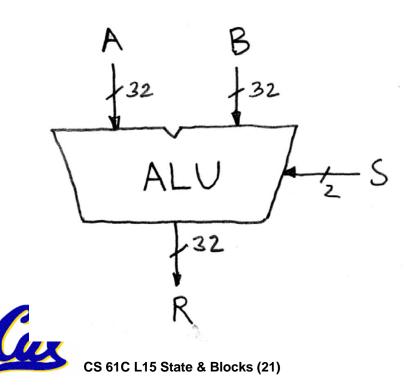

## **Arithmetic and Logic Unit**

- Most processors contain a logic block called "Arithmetic/Logic Unit" (ALU)

- We'll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR

when S=00, R=A+B when S=01, R=A-B when S=10, R=A AND B when S=11, R=A OR B

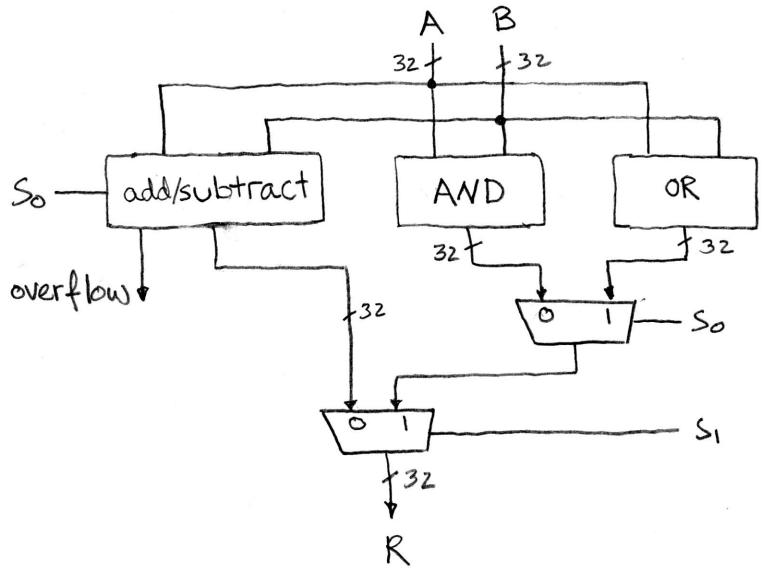

#### **Our simple ALU**

**Adder/Subtracter Design -- how?**

- Truth-table, then determine canonical form, then minimize and implement as we've seen before

- Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

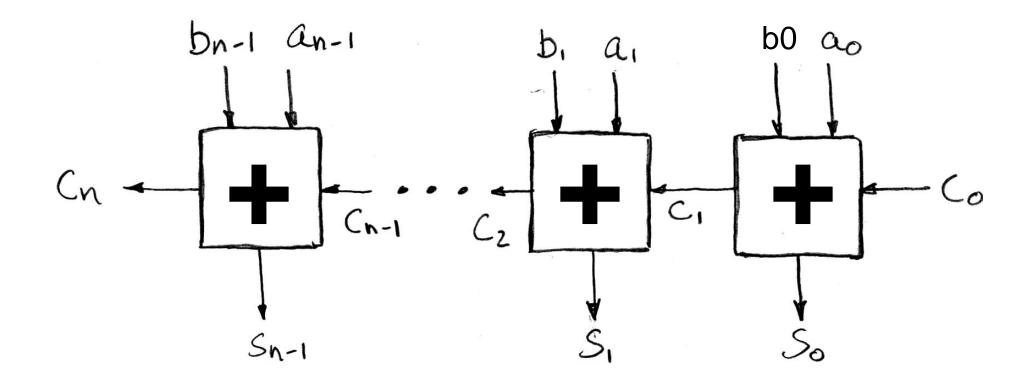

#### **N 1-bit adders** $\Rightarrow$ **1 N-bit adder**

#### Adder/Subtracter – One-bit adder LSB...

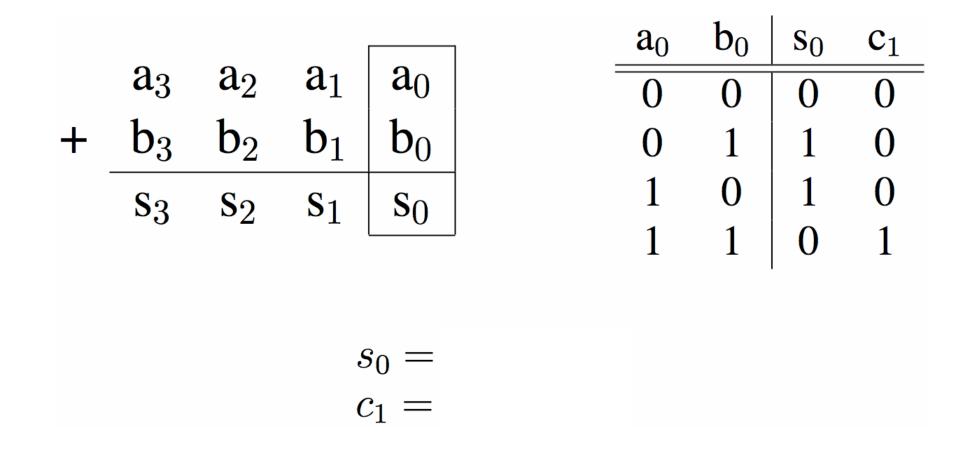

### Adder/Subtracter – One-bit adder (1/2)...

|   |            |            |                       |                |   | $\mathbf{a}_i$ | $\mathbf{b}_i$ | $\mathbf{c}_i$ | $\mathbf{s}_i$ | $\mathbf{c}_{i+1}$ |

|---|------------|------------|-----------------------|----------------|---|----------------|----------------|----------------|----------------|--------------------|

|   |            |            |                       |                |   | 0              | 0              | 0              | 0              | 0                  |

|   |            |            |                       |                |   | 0              | 0              | 1              | 1              | 0                  |

|   | $a_3$      |            | <b>a</b> <sub>1</sub> |                |   | 0              | 1              | 0              | 1              | 0                  |

| + | $b_3$      | $b_2$      | $b_1$                 | $\mathbf{b}_0$ |   | 0              | 1              | 1              | 0              | 1                  |

|   | <b>S</b> 3 | <b>S</b> 2 | <b>s</b> <sub>1</sub> | S <sub>0</sub> | - | 1              | 0              |                |                |                    |

|   | 0          | -          |                       |                |   | 1              | 0              | 1              | 0              | 1                  |

|   |            |            |                       |                |   | 1              | 1              | 0              | 0              | 1                  |

|   |            |            |                       |                |   | 1              | 1              | 1              | 1              | 1                  |

$s_i = c_{i+1} =$

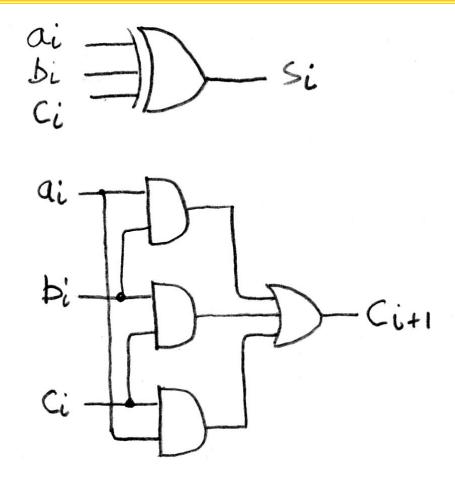

#### Adder/Subtracter – One-bit adder (2/2)...

$$s_i = \operatorname{XOR}(a_i, b_i, c_i)$$

$$c_{i+1} = \operatorname{MAJ}(a_i, b_i, c_i) = a_i b_i + a_i c_i + b_i c_i$$

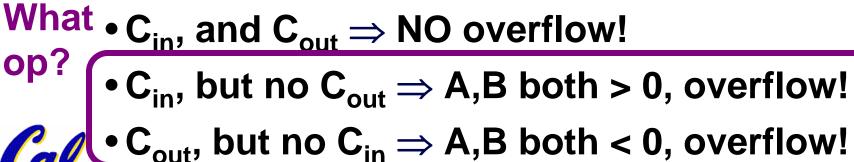

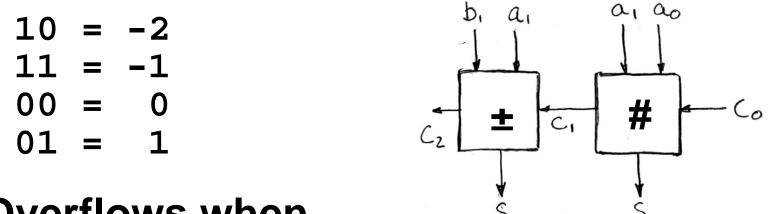

Consider a 2-bit signed # & overflow:

- $\cdot 10 = -2 + -2 \text{ or } -1$

- •11 = -1 + -2 only

- $\bullet 00 = 0 \text{ NOTHING!}$

- •01 = 1 + 1 only

- Highest adder

- $C_1 = Carry-in = C_{in}, C_2 = Carry-out = C_{out}$

- No  $C_{out}$  or  $C_{in} \Rightarrow$  NO overflow!

a ao

#

b, a,

<u>+</u>

$C_2$

C,

Consider a 2-bit signed # & overflow:

- Overflows when...

- C<sub>in</sub>, but no C<sub>out</sub> ⇒ A,B both > 0, overflow!

C<sub>out</sub>, but no C<sub>in</sub> ⇒ A,B both < 0, overflow!</li>

# overflow $= c_n \operatorname{XOR} c_{n-1}$

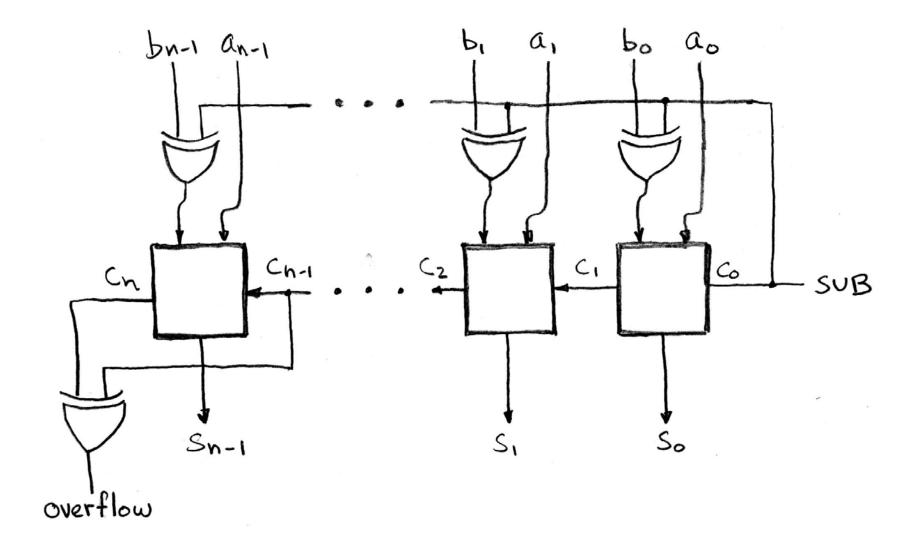

#### **Extremely Clever Subtractor**

- A. Truth table for mux with 4 control signals has 2<sup>4</sup> rows

- B. We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl

- C. If 1-bit adder delay is T, the N-bit adder delay would also be T

"And In conclusion..."

- Use muxes to select among input

- S input bits selects 2S inputs

- Each input can be n-bits wide, indep of S

- Implement muxes hierarchically

- ALU can be implemented using a mux

- Coupled with basic block elements

- N-bit adder-subtractor done using N 1bit adders with XOR gates on input

- XOR serves as conditional inverter

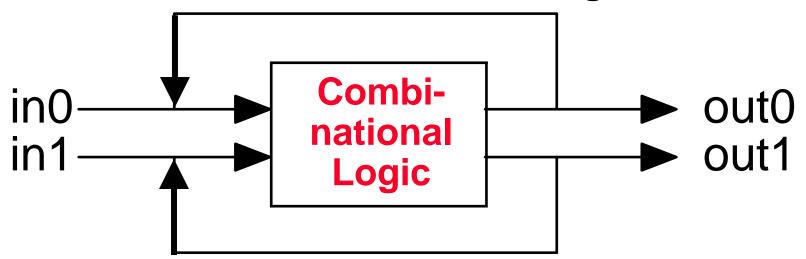

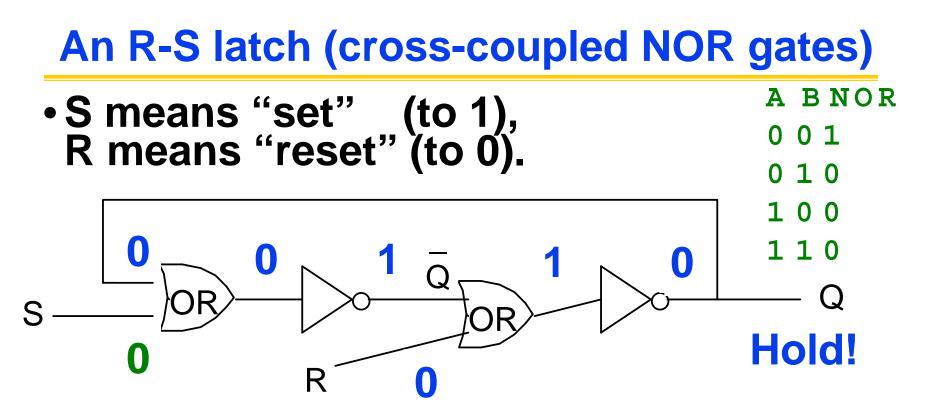

# **State Circuits Overview (Extra Slides)**

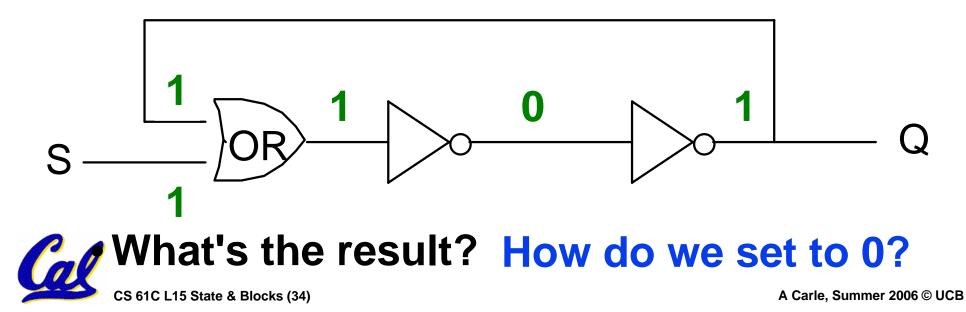

• State circuits have feedback, e.g.

- Output is function of inputs + fed-back signals.

- Feedback signals are the circuit's state.

- What aspects of this circuit might cause complications?

#### A simpler state circuit: two inverters

- When started up, it's internally stable.

- Provide an or gate for coordination:

Adding Q' gives standard RS-latch:

- Truth table

- SRQ

- 0 0 hold (keep value)

- 010

- 101

- 1 1 unstable

CS 61C L15 State & Blocks (35)

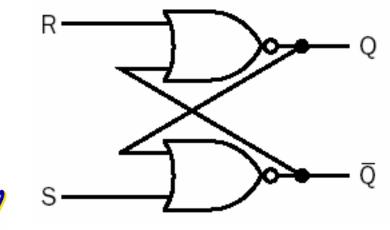

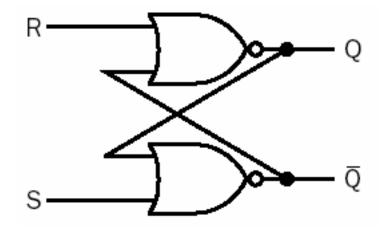

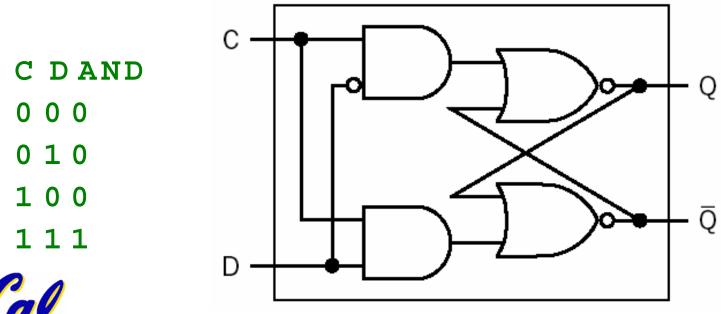

# An R-S latch (in detail)

#### **Truth table**

A B NOR 0 0 1 0 1 0

100

110

1 11 x x unstable

CS 61C L15 State & Blocks (36)

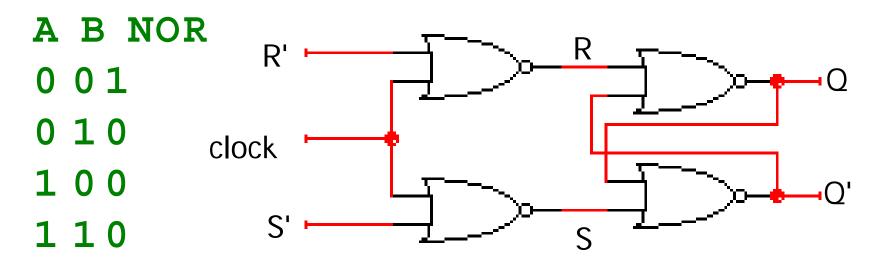

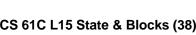

# **Controlling R-S latch with a clock**

Can't change R and S while clock is active.

#### Clocked latches are called *flip-flops*.

D flip-flop are what we really use

- Inputs C (clock) and D.

- When C is 1, latch open, output = D (even if it changes, "transparent latch")

- When C is 0, latch closed, output = stored value.

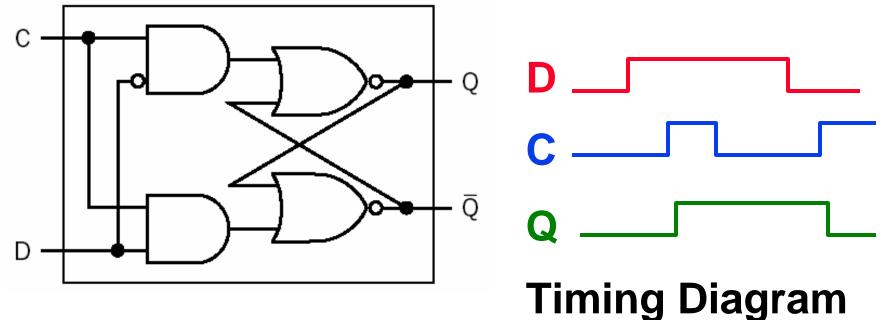

# **D** flip-flop details

### • We don't like transparent latches

• We can build them so that the latch is only open for an instant, on the rising edge of a clock (as it goes from  $0 \Rightarrow 1$ )

- This is a "rising-edge D Flip-Flop"

- When the CLK transitions from 0 to 1 (rising edge) ...

- $Q \leftarrow D$ ; Qbar  $\leftarrow not D$

- All other times: Q ← Q; Qbar ← Qbar