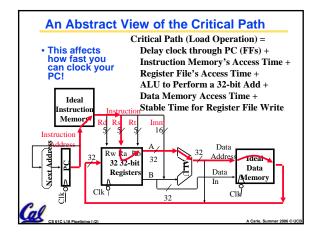

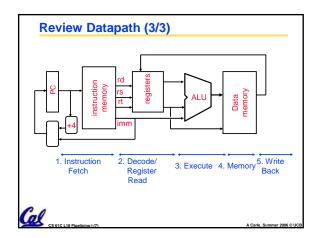

## Review Datapath (1/3)

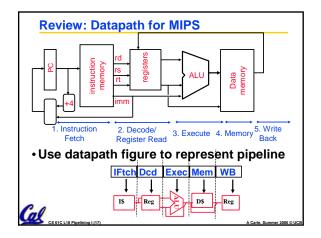

- Datapath is the hardware that performs operations necessary to execute programs.

- Control instructs datapath on what to do next.

- · Datapath needs:

Cal

- access to storage (general purpose registers and memory)

- computational ability (ALU)

- helper hardware (local registers and PC)

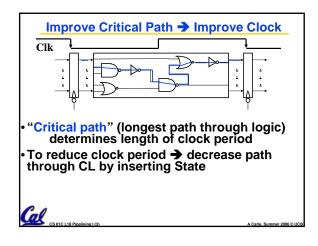

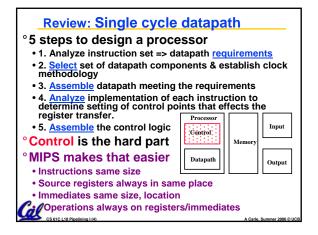

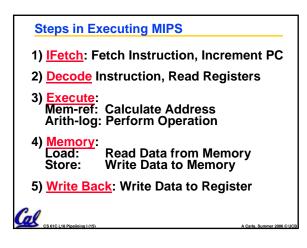

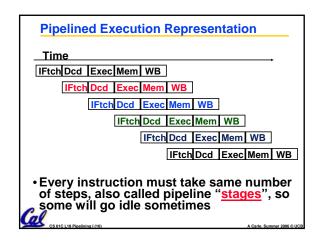

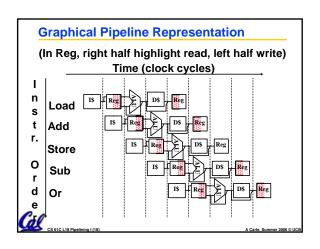

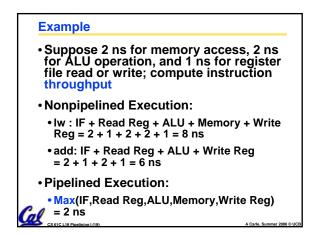

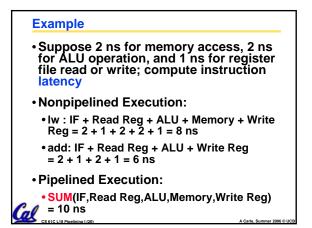

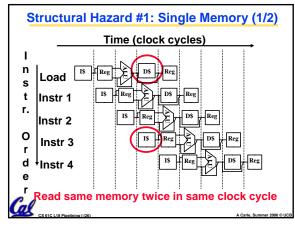

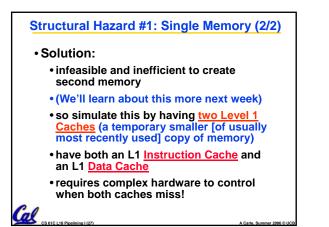

## Review Datapath (2/3) Five stages of datapath (executing an instruction): Instruction Fetch (Increment PC) Instruction Decode (Read Registers) ALU (Computation) Memory Access Write to Registers ALL instructions must go through ALL five stages.

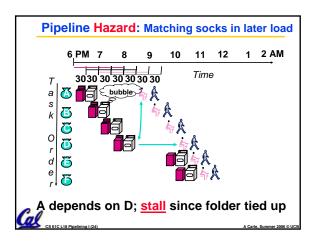

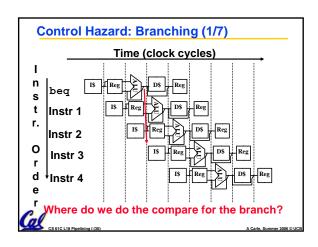

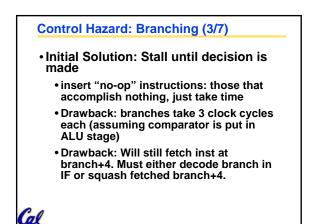

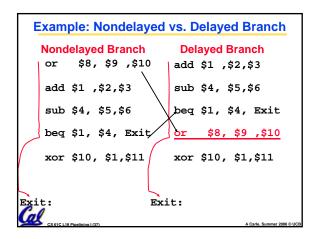

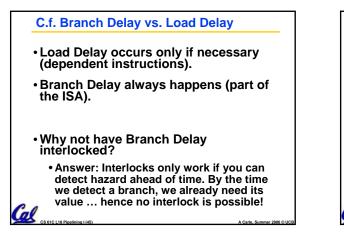

## Control Hazard: Branching (2/7)

- We put branch decision-making hardware in ALU stage

- therefore two more instructions after the branch will *always* be fetched, whether or not the branch is taken

- Desired functionality of a branch

al

al

- if we do not take the branch, don't waste any time and continue executing normally

- if we take the branch, don't execute any instructions after the branch, just go to the desired label

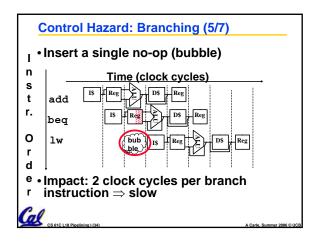

- Stage 2, only one unnecessary instruction is fetched, so only one no-op is needed

- Side Note: This means that branches are idle in Stages 3, 4 and 5.

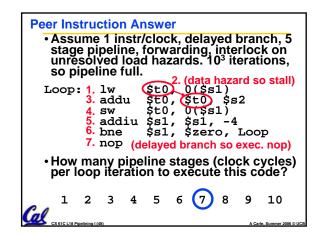

| Peer Instruction                                                                                                             |                  |

|------------------------------------------------------------------------------------------------------------------------------|------------------|

| Assume 1 instr/clock, delayed branch, 5 stage                                                                                | 1                |

| pipeline, forwarding, interlock on unresolved                                                                                | 2                |

| load hazards (after 10 <sup>3</sup> loops, so pipeline full)                                                                 | 3                |

| Loop: lw \$t0, 0(\$s1)<br>addu \$t0, \$t0, \$s2<br>sw \$t0, 0(\$s1)<br>addiu \$s1, \$s1, -4<br>bne \$s1, \$zero, Loop<br>nop | 4<br>5<br>7<br>8 |

| •How many pipeline stages (clock cycles) per                                                                                 | 9                |

| loop iteration to execute this code?                                                                                         | 10               |

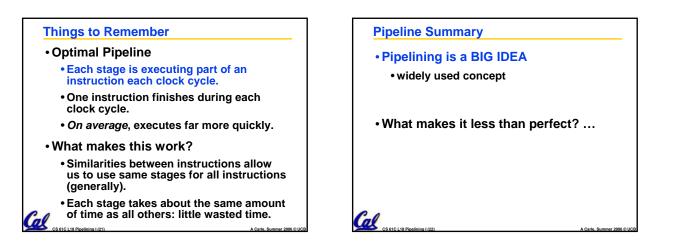

## "And in Conclusion.."

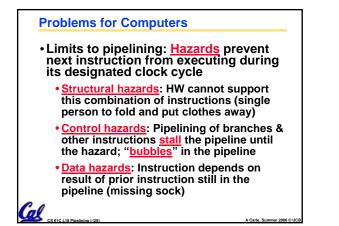

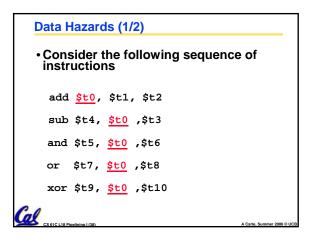

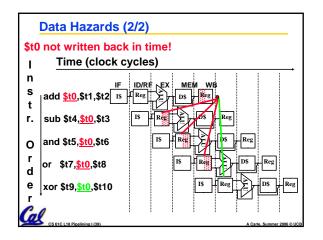

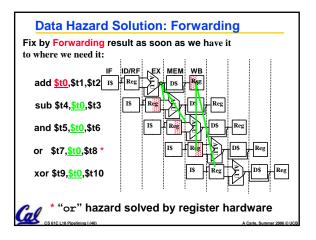

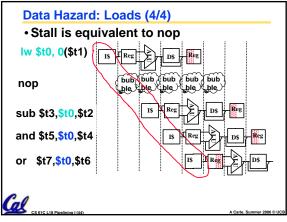

- Pipeline challenge is hazards

- Forwarding helps w/many data hazards

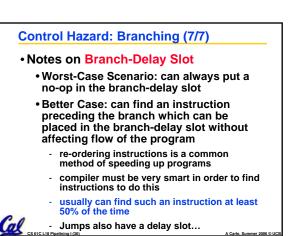

- Delayed branch helps with control hazard in 5 stage pipeline

CS 61C L18 Predining 1 (49) A Carle, Sum