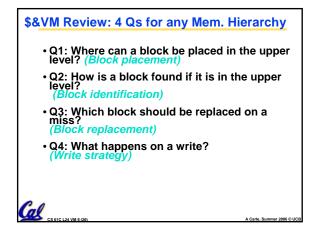

| Comparing the 2 I                                  | evels of hierarchy           |  |  |  |

|----------------------------------------------------|------------------------------|--|--|--|

| Cache Version                                      | Virtual Memory vers.         |  |  |  |

| Block or Line                                      | Page                         |  |  |  |

| Miss                                               | Page Fault                   |  |  |  |

| Block Size: 32-64B                                 | Page Size: 4K-8KB            |  |  |  |

| Placement:<br>Direct Mapped,<br>N-way Set Associat | Fully Associative            |  |  |  |

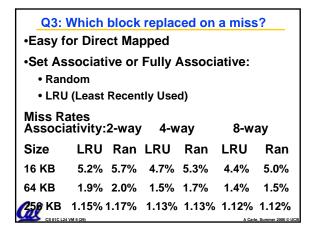

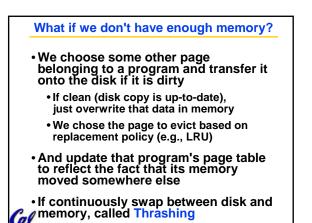

| Replacement:<br>LRU or Random                      | Least Recently Used<br>(LRU) |  |  |  |

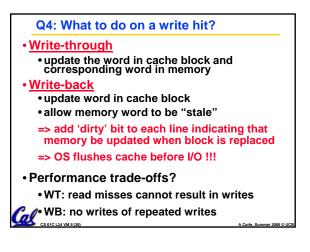

| Write Thru or Back                                 | Write Back                   |  |  |  |

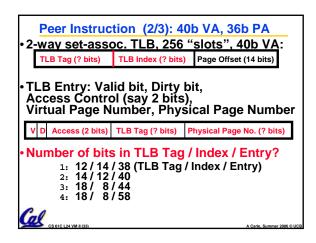

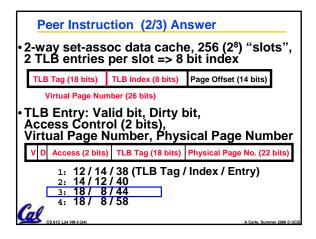

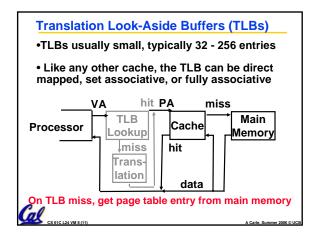

|                                                                                                                                                                                                                                                                                                                                                                                                                               | Typical            | TLB For             | mat   |     |       |                  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------|-----|-------|------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                               | Virtual<br>Address | Physical<br>Address | Dirty | Ref | Valid | Access<br>Rights |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |                     |       |     |       |                  |  |  |

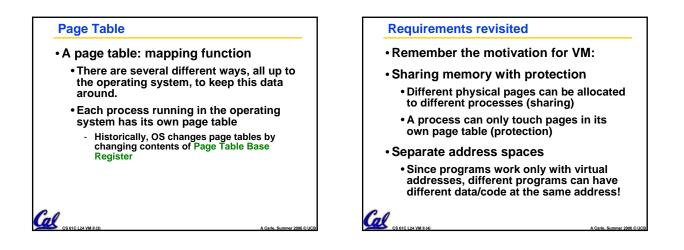

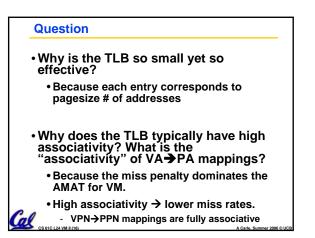

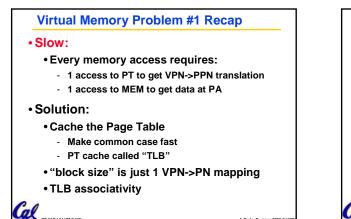

| <ul> <li>TLB just a cache on the page table mappings</li> <li>TLB access time comparable to cache<br/>(much less than main memory access time)</li> <li><u>Dirty</u>: since use write back, need to know whether<br/>or not to write page to disk when replaced</li> <li><u>Ref</u>: Used to help calculate LRU on replacement</li> <li>Cleared by OS periodically, then checked to<br/>see if page was referenced</li> </ul> |                    |                     |       |     |       |                  |  |  |

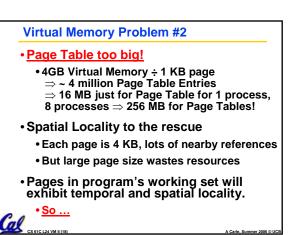

## **Solutions**

Cal

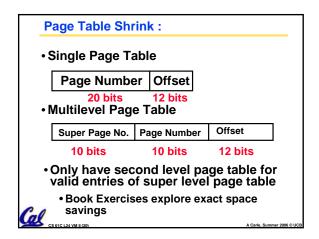

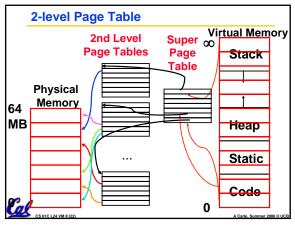

## • Page the Page Table itself!

- Works, but must be careful with neverending page faults

- Pin some PT pages to memory

- 2-level page table

- Solutions tradeoff in-memory PT size for slower TLB miss

- Make TLB large enough, highly associative so rarely miss on address translation

- CS 162 will go over more options and in greater depth