# **CS61CL Machine Structures**

# Lec 7 – Introduction to Digital Design

David Culler Electrical Engineering and Computer Sciences University of California, Berkeley

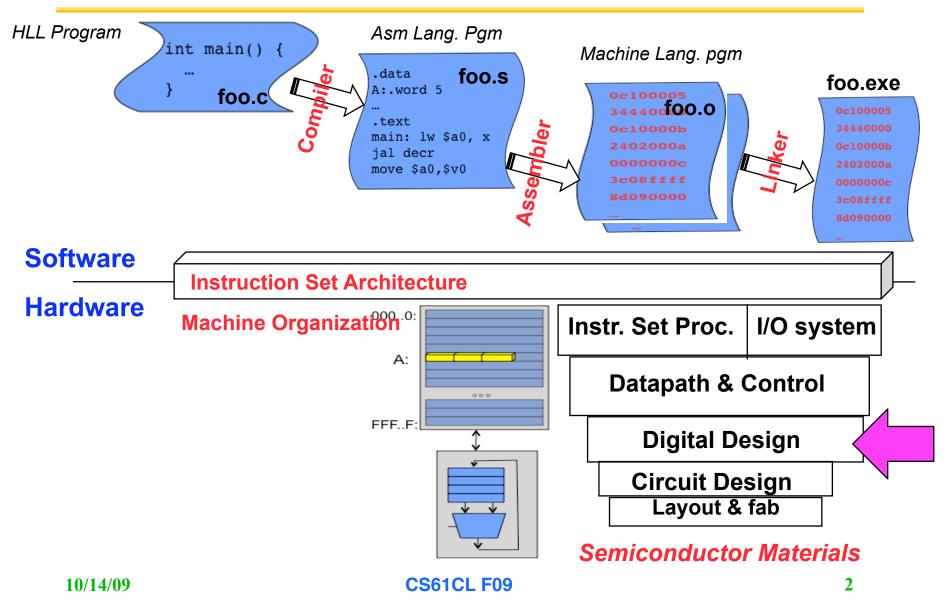

# **CS61CL Road Map**

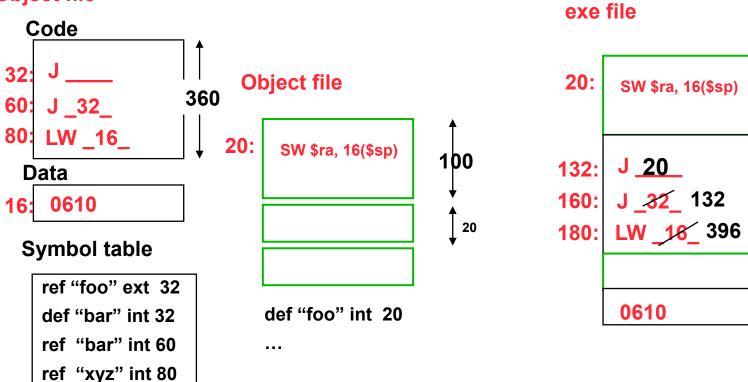

# Linking

#### **Object file**

- Resolve names to addresses

- Relocate code and data blocks

Adjust internally resolved addresses

ddef "xyz" int 16

#### Questions

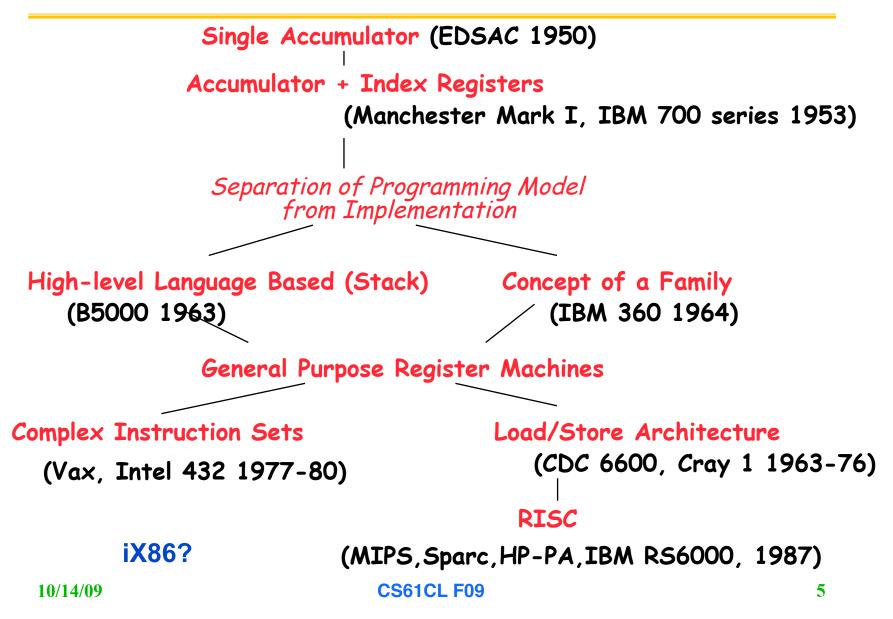

## **Evolution of Instruction Sets**

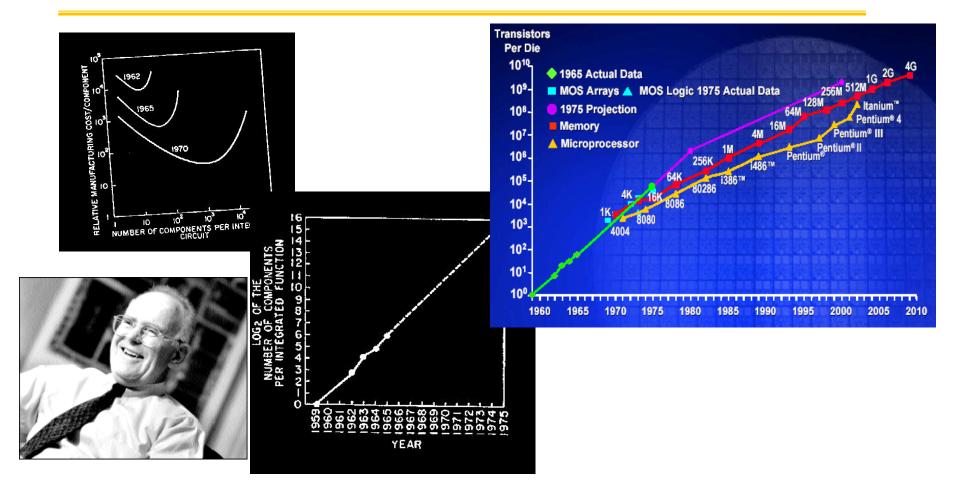

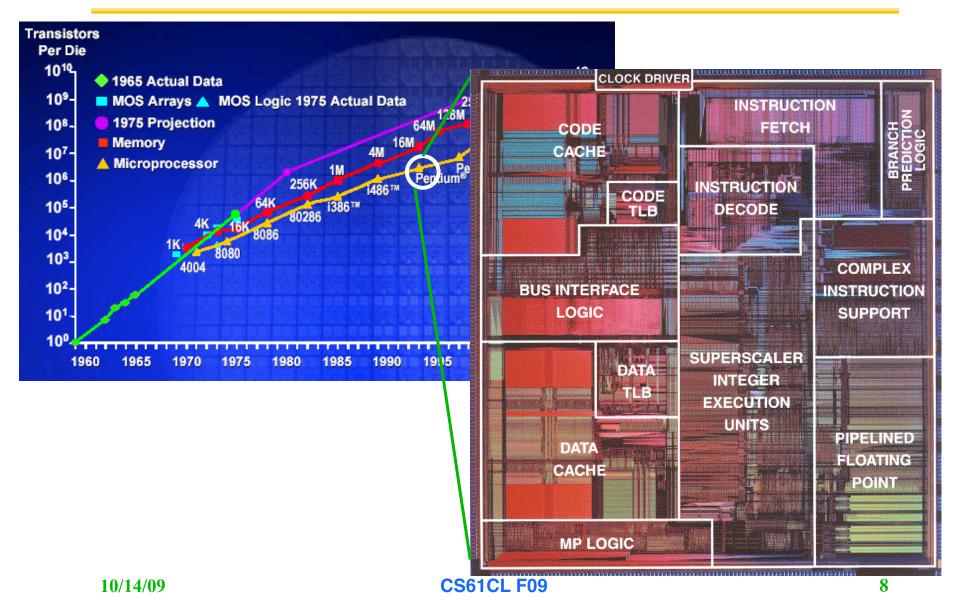

# **Dramatic Technology Advance**

#### Prehistory: Generations

- 1<sup>st</sup> Tubes

- 2<sup>nd</sup> Transistors

- 3<sup>rd</sup> Integrated Circuits

- 4<sup>th</sup> VLSI....

- Discrete advances in each generation

- Faster, smaller, more reliable, easier to utilize

- Modern computing: Moore's Law

- Continuous advance, fairly homogeneous technology

#### **Moore's Law**

- "Cramming More Components onto Integrated Circuits"

- Gordon Moore, Electronics, 1965

- # on transistors on cost-effective integrated circuit double every 18 months

10/14/09

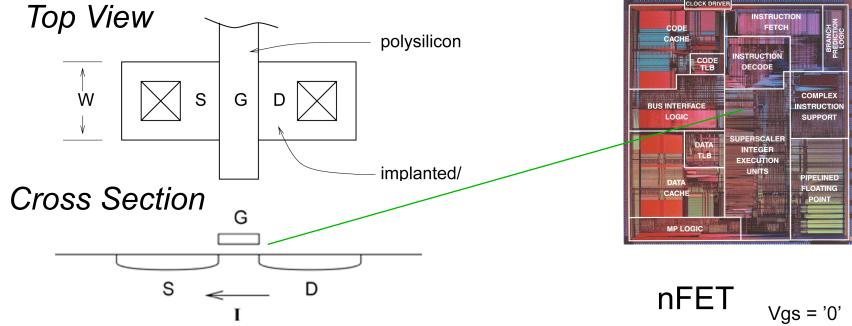

# **Example: Intel Pentium**

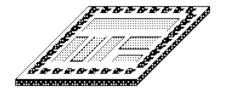

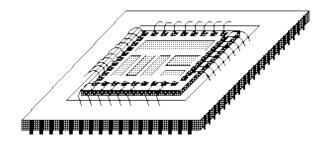

### **Integrated Circuits**

#### Chip in Package

- Primarily Crystalline Silicon

- 1mm 25mm on a side

- 100 200M transistors

- (25 50M "logic gates")

- 3 10 conductive layers

- 2002 feature size ~ 0.13um = 0.13 x 10<sup>-6</sup> m

- "CMOS" most common complementary metal oxide semiconductor

- Package provides:

- spreading of chip-level signal paths to board-level

- heat dissipation.

- Ceramic or plastic with gold wires.

## **Integrated Circuits**

- Uses for digital IC technology today:

- <u>standard microprocessors</u>

- » used in desktop PCs, and embedded applications

- » simple system design (mostly software development)

- memory chips (DRAM, SRAM)

- <u>application specific ICs (ASICs)</u>

- » custom designed to match particular application

- » can be optimized for low-power, low-cost, high-performance

- » high-design cost / relatively low manufacturing cost

- field programmable logic devices (FPGAs, CPLDs)

- » customized to particular application after fabrication

- » short time to market

- » relatively high part cost

- <u>standardized low-density components</u>

- » still manufactured for compatibility with older system designs

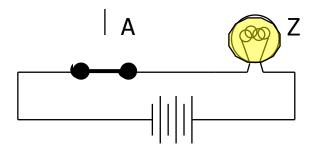

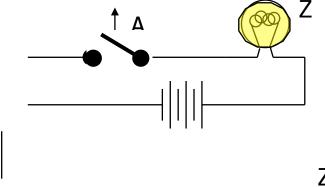

# **Switches: the basic element**

• Implementing a simple circuit:

close switch (if A is "1" or asserted) and turn on light bulb (Z)

open switch (if A is "O" or unasserted) and turn off light bulb (Z)

Z = A

# **Physical world to Digital world**

| Technology                        | State "O"                              | State "1"                   |

|-----------------------------------|----------------------------------------|-----------------------------|

| Relay logic                       | Circuit Open                           | Circuit Closed              |

| CMÓS logic                        | 0.0-1.0 volts                          | 2.0-3.0 volts               |

| Transistor transistor logic (TTL) |                                        | 0.0-0.8 volts 2.0-5.0 volts |

| Fiber Optics                      | Light off                              | Light on                    |

| Dynamic RAM                       | Discharged capacitor Charged capacitor |                             |

| Nonvolatile memory (erasable)     | Trapped electrons                      |                             |

| Programmable ROM                  | Fuse blown                             | Fuse intact                 |

| Bubble memory                     | No magnetic bubble                     | Bubble present              |

| Magnetic disk                     | No flux reversal                       |                             |

| Compact disc                      | No pit                                 | Pit                         |

Sense the logical value, manipulate in a systematic fashion.

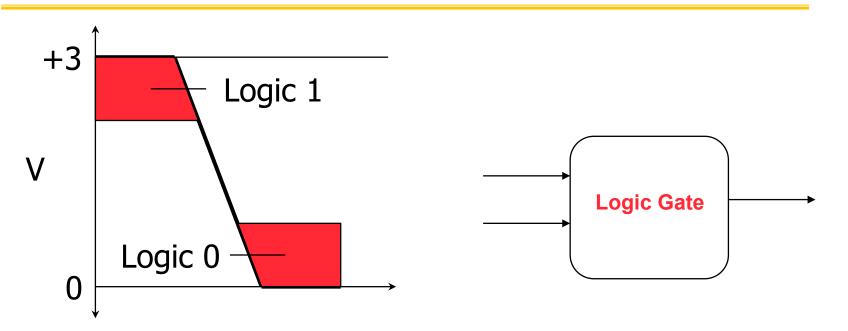

# **The Digital Abstraction**

- Logical 1 (true) : V > Vdd –V th

- Logical 0 (false) : V < Vth</li>

- Logical Gates

- behave like boolean operators on these voltage signals

- Produce signals that can be treated as logical values

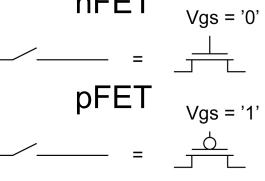

## **CMOS "Devices"**

• **MOSFET** (Metal Oxide Semiconductor Field Effect Transistor)

- Essentially a voltage-controlled switch

- N: closed when gate is Hi

- P: closed when gate is Lo

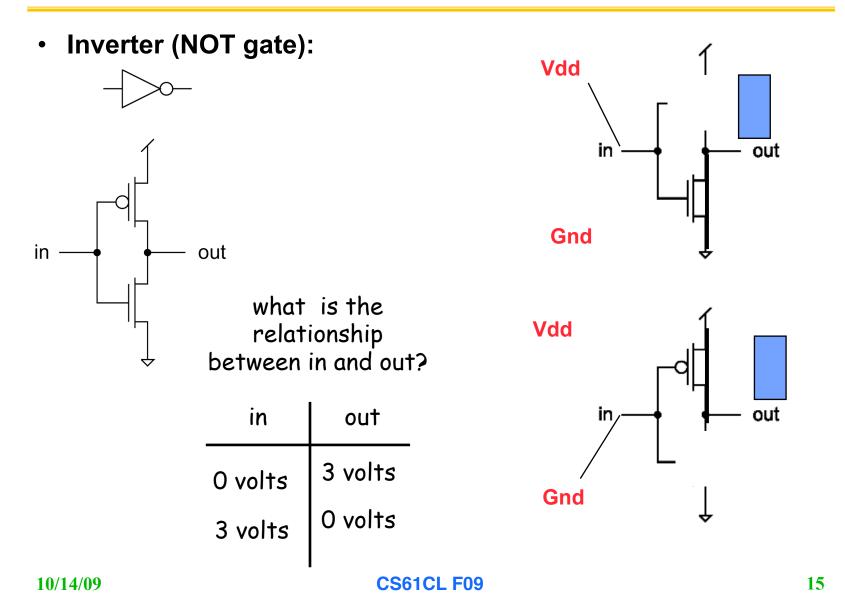

# **Transistor-level Logic Circuits (inv)**

### **Example: NOT**

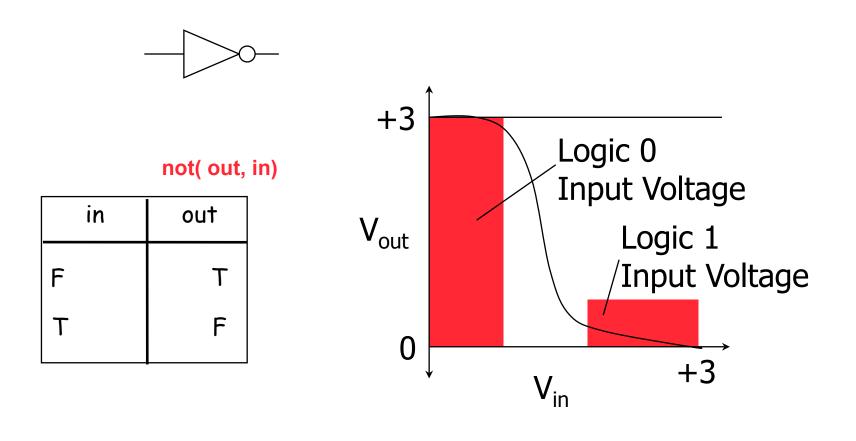

# **Big idea: Self-restoring logic**

- CMOS logic gates are self-restoring

- Even if the inputs are imperfect, switching time is fast and outputs go "rail to rail"

- Doesn't matter how many you cascade

- » Although propagation delay increases

- Limit fan-out to ensure sharp and complete transition

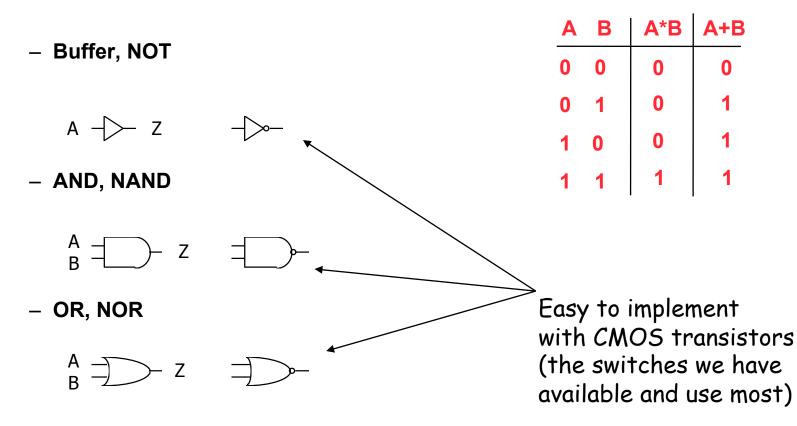

## **Combinational Logic Symbols**

Common combinational logic systems have standard symbols called *logic gates*

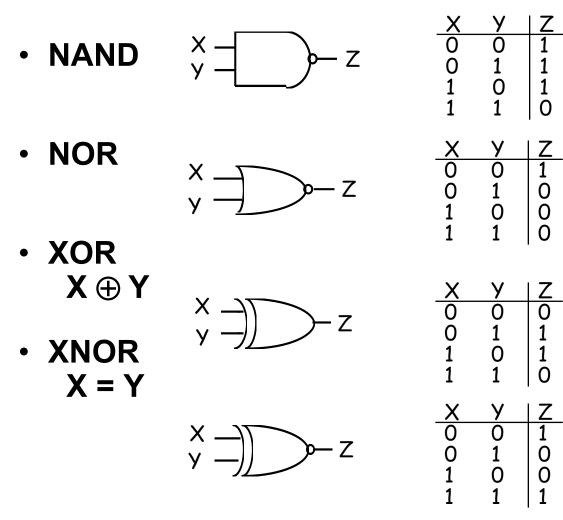

#### more Boolean Expressions to Logic Gates

X <u>xor</u> Y = X Y' + X' Y X or Y but not both ("inequality", "difference")

X <u>xnor</u> Y = X Y + X' Y' X and Y are the same ("equality", "coincidence")

10/14/09

## **Administration**

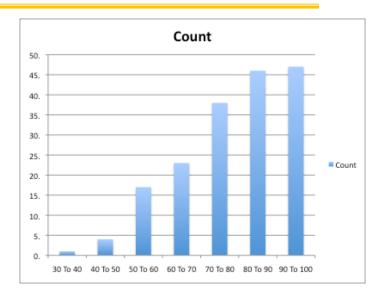

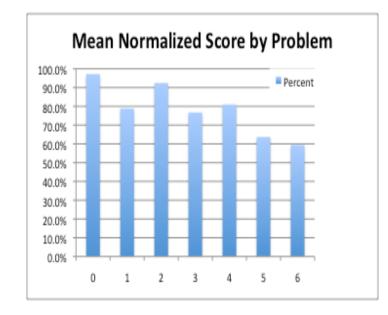

#### Great job on Mid Term

Mean: 79%, Median: 82%, Min: 36, Max: 99 (3)

#### Project 2 is due Monday 10/26

- Work in pieces

- » call snprintf / save / restore / rtn

- » copy format to buffer respecting bufferSize

- » dispatch to one format function

- » add other format functions

- Homework 6 out tonight

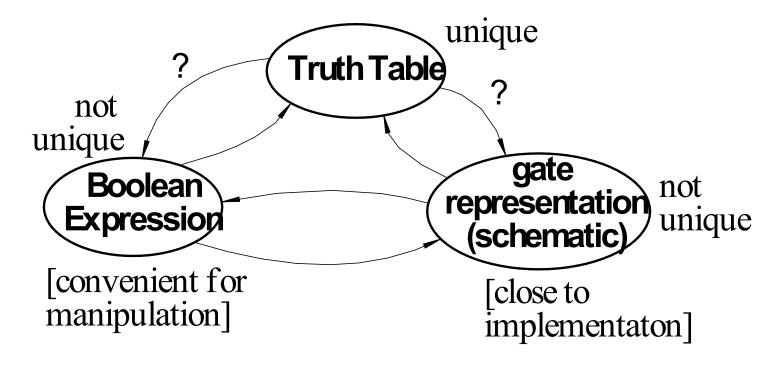

# **Relationship Among Representations**

\* Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

10/14/09

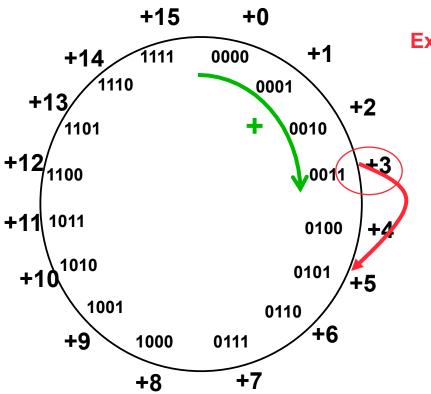

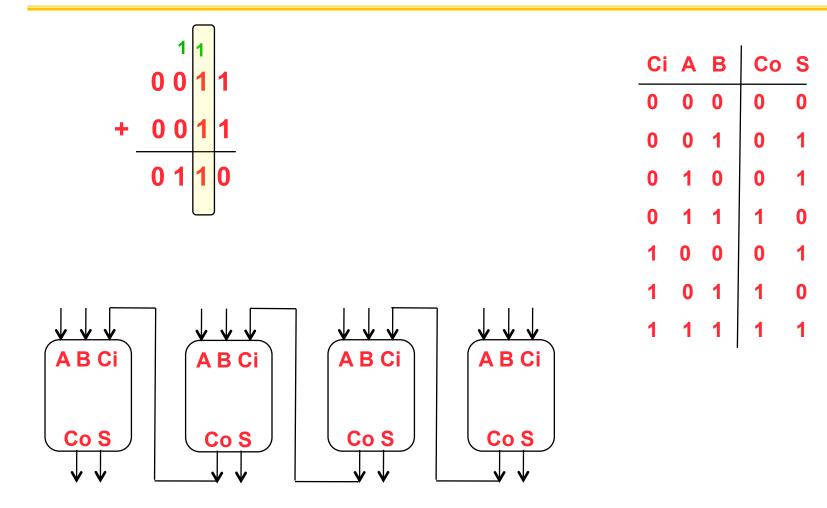

#### **Recall: Addition**

#### Example: 3 + 2 = 5

Unsigned binary addition Is just addition, base 2 Add the bits in each position and carry

#### **Design an Adder**

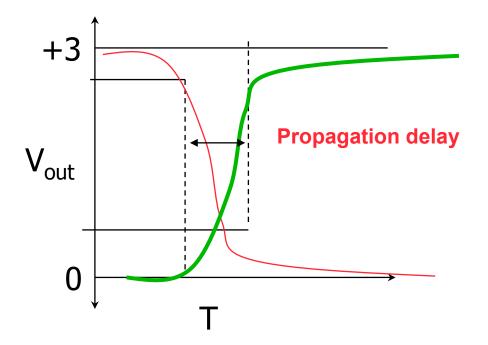

### **Element of Time**

- Logical change is not instantaneous

- Broader digital design methodology has to make it appears as such

- Clocking, delay estimation, glitch avoidance

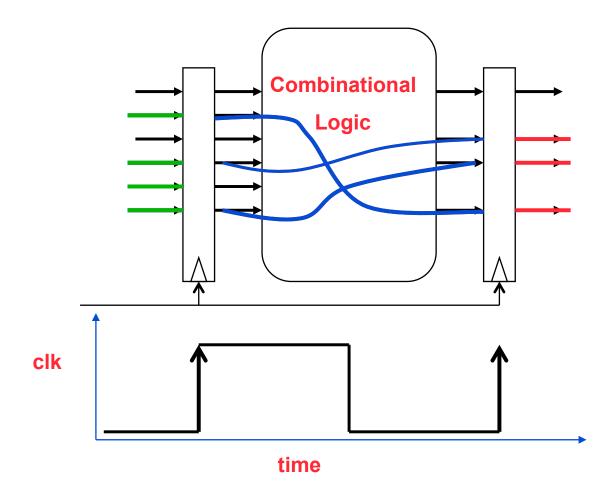

### What makes Digital Systems tick?

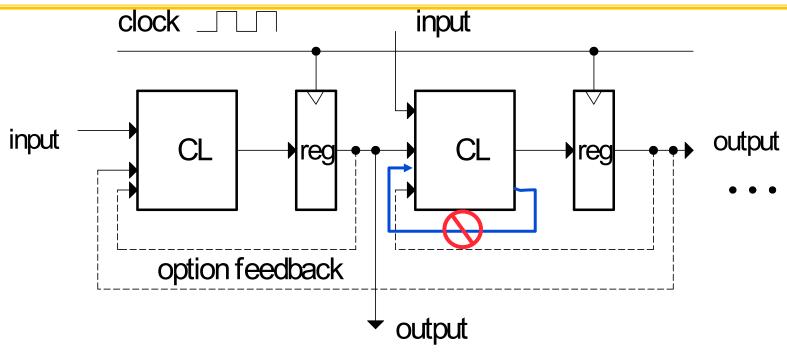

# **Synchronous Circuit Design**

- Combinational Logic Blocks (CL)

- Acyclic

- no internal state (no feedback)

- output only a function of inputs

- Registers (reg)

- collections of flip-flops

- clock

- distributed to all flip-flops

- ALL CYCLES GO THROUGH A REG!

## **Modern Hardware Design**

#### Extremely Software Intensive

- Design tools (schematic capture, hardware description lang.)

- Simulation tools

- Optimization tools

- Verification tools

- Supply chain and project management

- Managing complexity of fundamental

- Modularity

- Methodology

- Clarity

- Technology independence

- Push the edge

- Of the available tools

- Of the technology

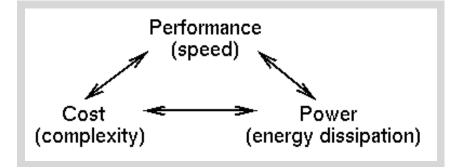

# **Basic Design Tradeoffs**

- You can usually improve on one at the expense of one or both of the others.

- These tradeoffs exist at every level in the system design - every sub-piece and component.

- Design Specification -

- Functional Description.

- Performance, cost, power constraints.

- As a designer you must make the tradeoffs necessary to achieve the function within the constraints.