EECS 151/251A Spring 2018 Digital Design and Integrated Circuits

Instructors: Nick Weaver & John Wawrzynek

Lecture 9

# **Administration**

- First Midterm Thursday

- Decided on closed book (sorry), but will give you extra time. We will make an exam that is expected to take 90 minutes, but will give you 3 hours.

- 5-8PM

- 405 Soda

- Material: Everything up to slide 35 of Thursdays lecture (Lecture 8) – that is, CMOS logic is included.

#### **Previous Lecture**

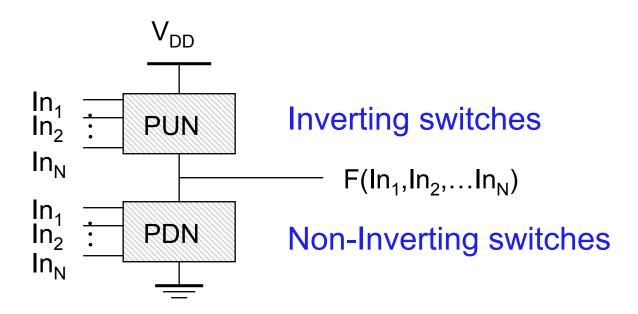

# **Static Complementary CMOS**

PUN and PDN are dual logic networks PUN and PDN functions are complementary

- □ Full rail-to-rail swing

- Symmetrical VTC

- □ No (...) static power dissipation

- Direct path current during switching

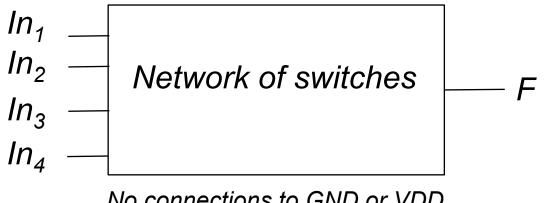

# Switch (Transmission Gate Logic)

Static:

Output always defined by GND or VDD, never both

No connections to GND or VDD

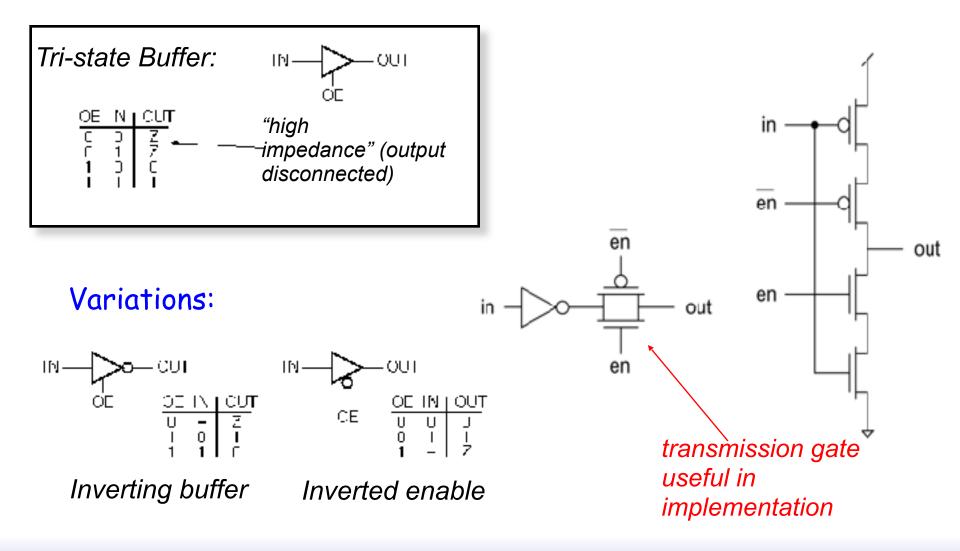

### **Tri-state Buffers**

### **Tri-state Buffers**

Tri-state buffers enable "bidirectional" connections.

Tri-state buffers are used when multiple circuits all connect to a common wire. Only one circuit at a time is allowed to drive the bus. All others "disconnect" their outputs, but can "listen".

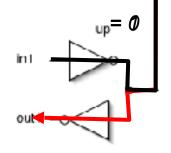

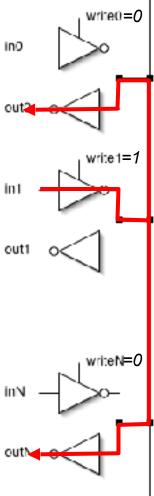

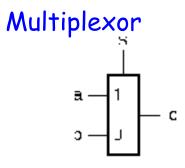

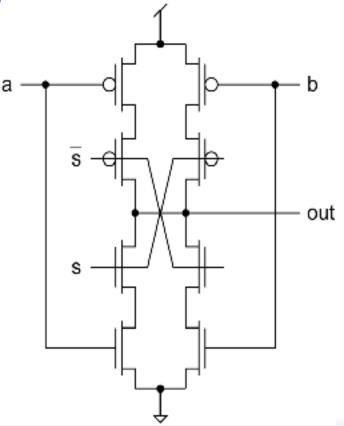

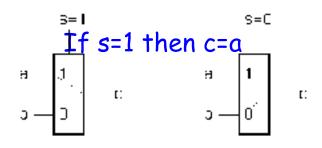

# **Tri-state Based Multiplexor**

Transistor Circuit for inverting multiplexor:

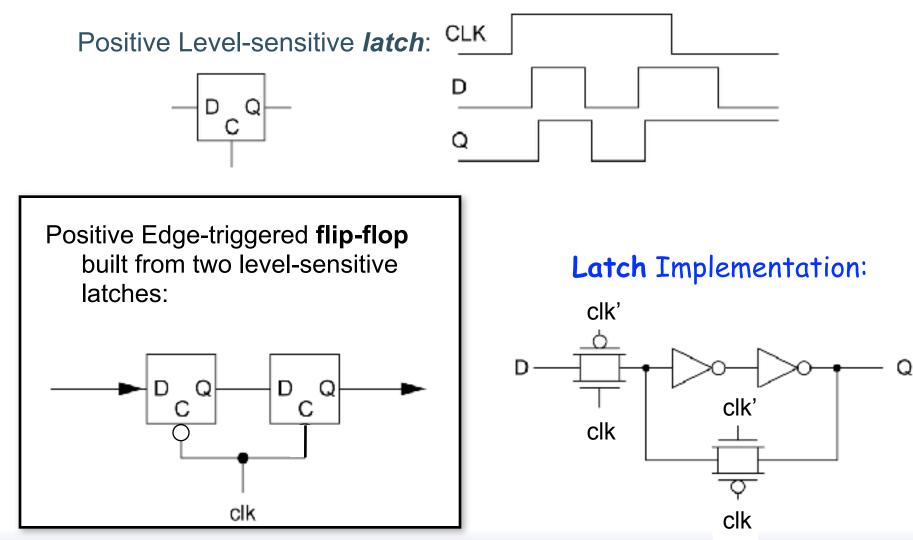

# Latches and Flip-flops

### **Digital abstraction**

## **Noise and Digital Systems**

#### □ Circuit needs to works despite "analog" noise

- Digital gates can and must reject noise

- This is actually how digital systems are defined

#### Digital system is one where:

- Discrete values mapped to analog levels and back

- Elements (gates) can reject noise

- For "small" amounts of noise, output noise is less than input noise

- Thus, for sufficiently "small" noise, the system acts as if it was noiseless

- This is called regeneration

### Bridging the digital and the analog worlds

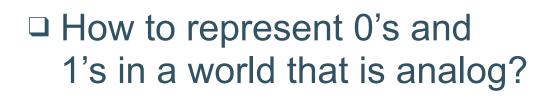

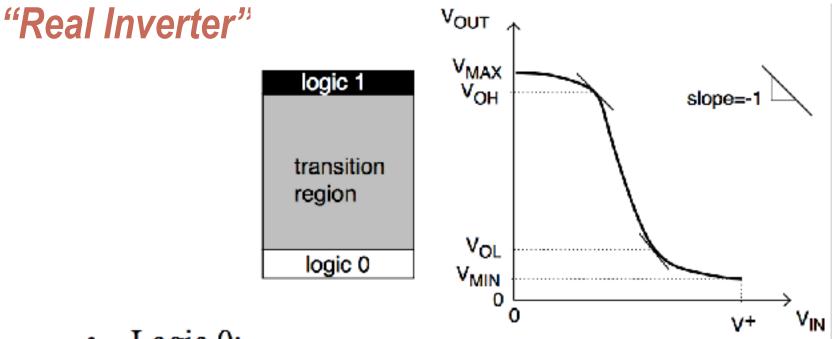

#### The Static Definition

- Logic 0:  $V_{MIN} \le V \le V_{OL}$

- Logic 1:  $V_{OH} \le V \le V_{MAX}$

- Undefined logic value:  $V \leq V_{OL}$

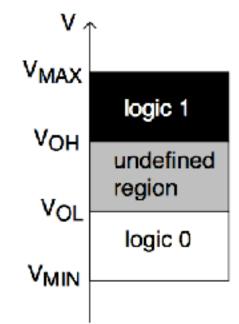

#### Ideal Inverter

Circuit representation and ideal transfer function:

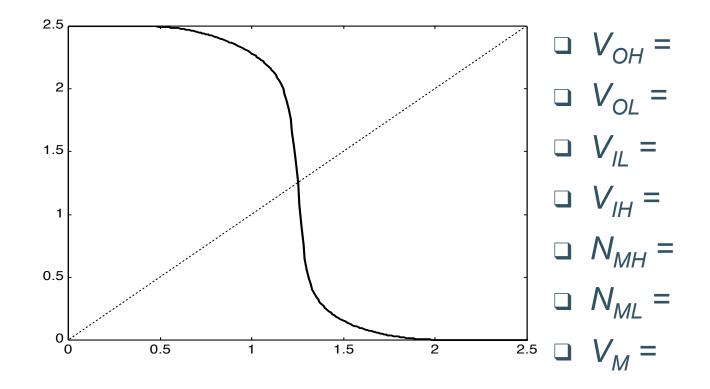

Define switching point or logic threshold :

•  $V_M \equiv \text{input voltage for which } V_{OUT} = V_{IN}$ - For  $0 \le V_{IN} < V_M \implies V_{OUT} = V^+$ - For  $V_M < V_{IN} \le V^+ \implies V_{OUT} = 0$

Ideal inverter returns well defined logical outputs (0 or V<sup>+</sup>) even in the presence of considerable noise in  $V_{IN}$  (from voltage spikes, crosstalk, etc.)  $\Rightarrow$  signal is *regenerated*! 13

- Logic 0:

- $V_{MIN} \equiv$  output voltage for which  $V_{IN} = V^+$

- V<sub>OL</sub> = smallest output voltage where slope = -1

- Logic 1:

- V<sub>OH</sub> = largest output voltage where slope = -1

- $-V_{MAX} \equiv$  output voltage for which  $V_{IN} = 0$

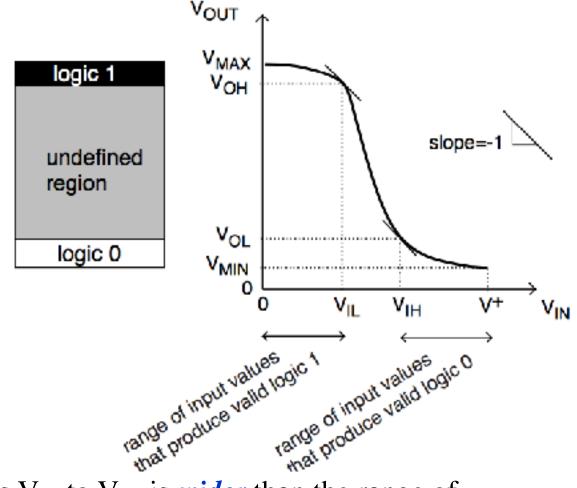

#### Valid Input Ranges

If range of output values  $V_{OL}$  to  $V_{OH}$  is *wider* than the range of input values  $V_{IL}$  to  $V_{IH}$ , then the inverter exhibits some noise immunity. (IVoltage gainl > 1)

Quantify this through *noise margins*.

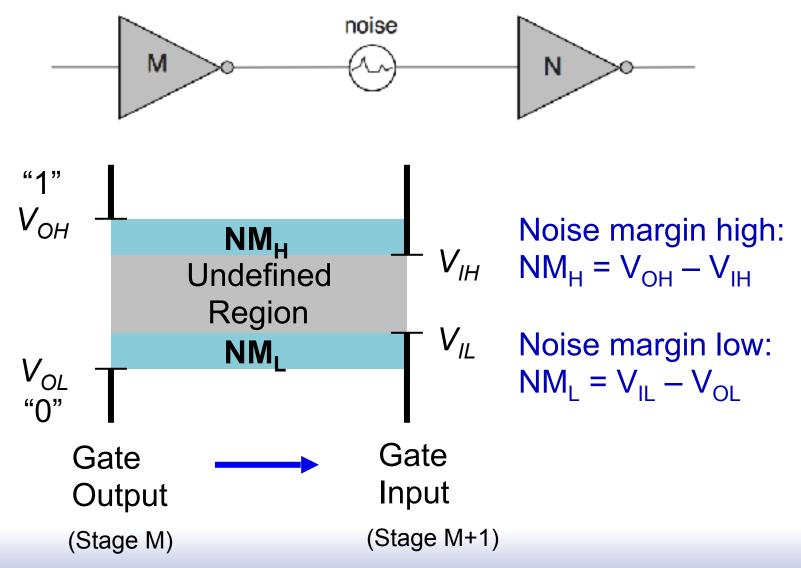

### **Definition of Noise Margins**

### Simulated Inverter VTC (Spice)

### **Transient properties**

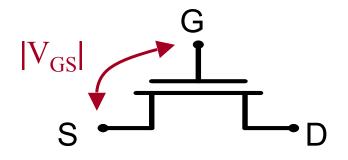

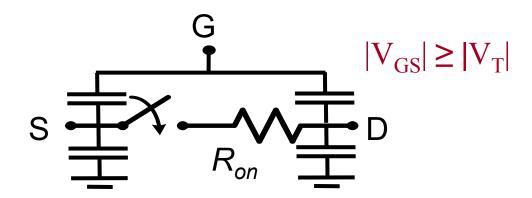

### The Switch – Dynamic Model

### The Switch – Dynamic Model (Simplified)

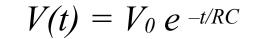

### The Switch Inverter: Transient Response

$t_{1/2} = ln(2) \times RC$

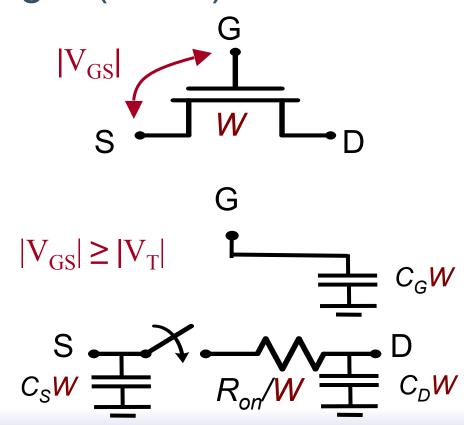

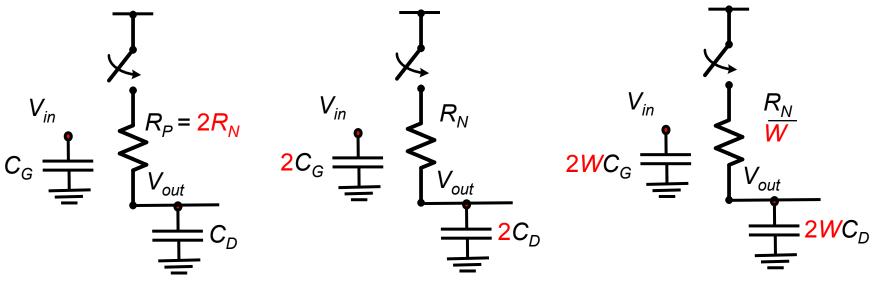

# Switch Sizing

What happens if we make a switch W times larger (wider)

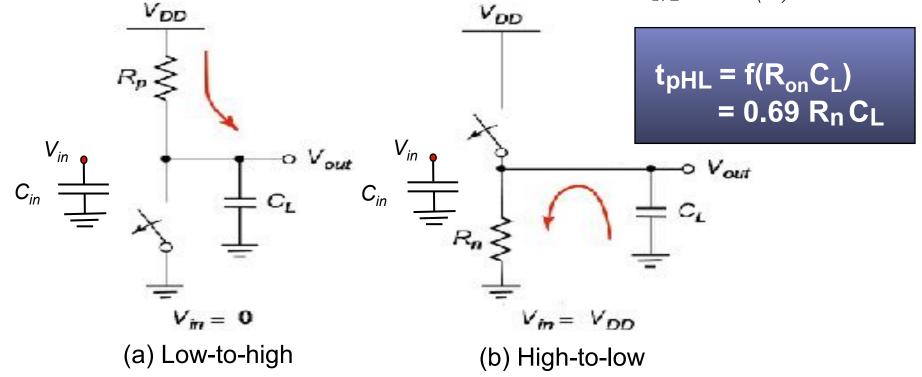

### **Switch Parasitic Model**

The pull-down switch (NMOS)

We assume transistors of minimal length (or at least constant length). R's and C's in units of per unit width.

The PMOS challenge:

For the same voltages, it provides less current (approximately 2 times less)

### **Switch Parasitic Model**

The pull-up switch (PMOS)

Minimum-size switch

Sized for symmetry

General sizing

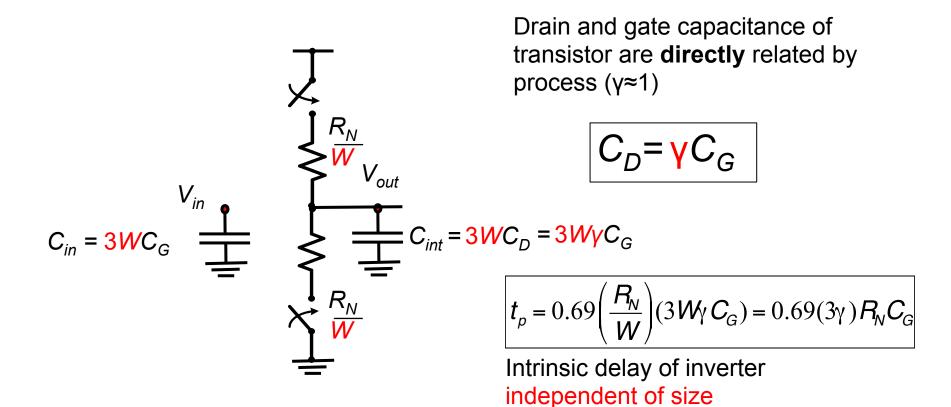

### **Inverter Parasitic Model**

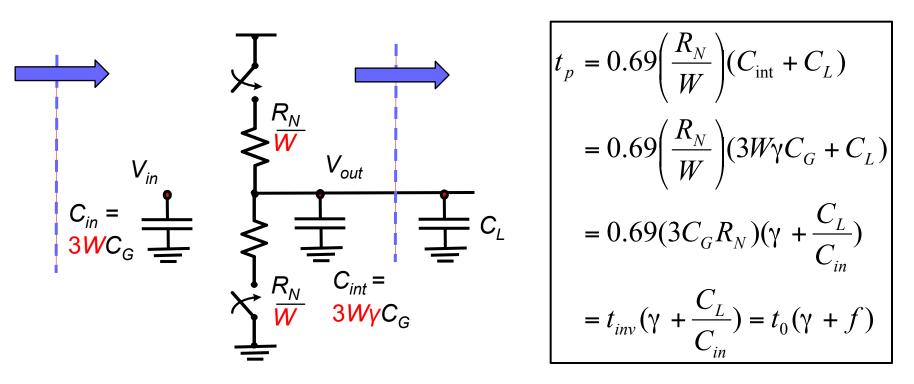

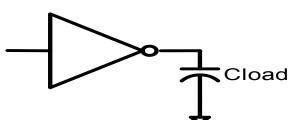

### **Inverter with Load Capacitance**

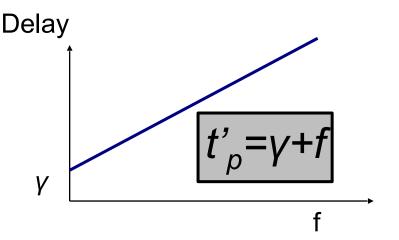

*f* = **fanout** = ratio between load and input capacitance of gate

# **Inverter Delay Model**

$$t_{\rho} = t_{inv}(\gamma + f)$$

- t<sub>inv</sub> technology constant

- Can be dropped from expression

- Delay unit-less variable (expressed in unit delays)

Question: how does transistor sizing (W) impact delay?

#### Inverter Delay Optimization

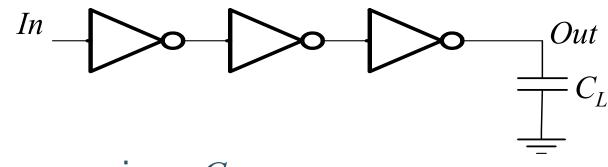

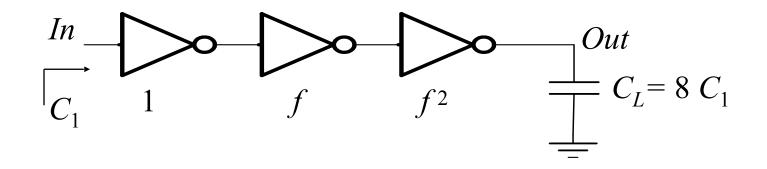

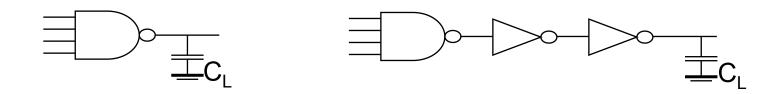

## **Inverter Chain**

#### $\Box$ For some given $C_L$ :

- How many stages are needed to minimize delay?

- How to size the inverters?

- □ Anyone want to guess the solution?

### **Careful about Optimization Problems**

- Get fastest delay if build one very big inverter

- So big that delay is set only by self-loading

- Likely not the problem you're interested in

- Someone has to drive this inverter...

### **Engineering Optimization Problems in General**

- Need to have a set of constraints

Constraints key to:

- Making the result useful

- Making the problem have a 'clean' solution

- □ For sizing problem:

- Need to constrain size of first inverter

# **Delay Optimization Problem #1**

#### □ You are given:

- A fixed number of inverters

- The size of the first inverter

- The size of the load that needs to be driven

#### □ Your goal:

- Minimize the delay of the inverter chain

- □ Need model for inverter delay vs. size

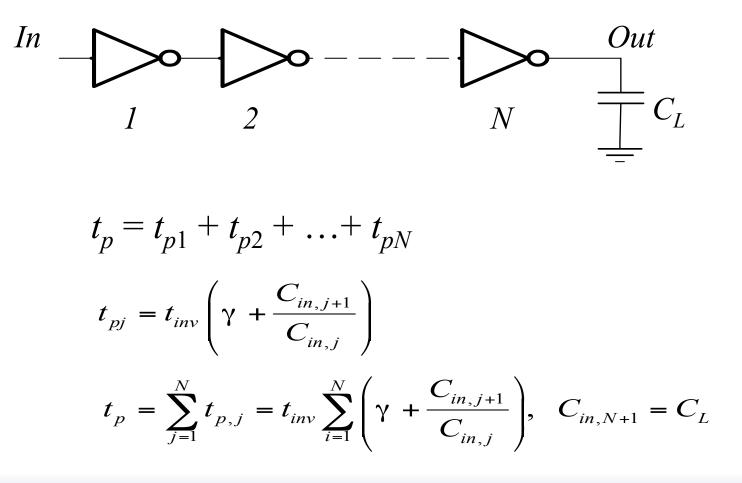

### **Apply to Inverter Chain**

34

# **Optimal Sizing for Given N**

□ Delay equation has N-1 unknowns,  $C_{in,2} \dots C_{in,N}$

□ **To minimize the delay,** find *N*-1 partial derivatives:

$$\begin{split} t_p &= \dots + t_{inv} \frac{C_{in,j}}{C_{in,j-1}} + t_{inv} \frac{C_{in,j+1}}{C_{in,j}} + \dots \\ \frac{dt_p}{dC_{in,j}} &= t_{inv} \frac{1}{C_{in,j-1}} - t_{inv} \frac{C_{in,j+1}}{C_{in,j}^2} = 0 \end{split}$$

# **Optimal Sizing for Given N** (cont'd)

Result: every stage has <u>equal fanout (f)</u>:

$$\frac{C_{in,j}}{C_{in,j-1}} = \frac{C_{in,j+1}}{C_{in,j}}$$

Size of each stage is geometric mean of two neighbors:

$$C_{in,j} = \sqrt{C_{in,j-1}C_{in,j+1}}$$

$\Box$  Equal fanout  $\rightarrow$  every stage will have same delay

### **Optimum Delay and Number of Stages**

$\Box$  When each stage has same fanout f:

$$f^N = F = C_L / C_{in,1}$$

□ Fanout of each stage:

$$f = \sqrt[N]{F}$$

□ Minimum path delay:

$$t_p = N t_{inv} \left( \gamma + \sqrt[N]{F} \right)$$

$C_L/C_1$  has to be evenly distributed across N = 3 stages:

# **Delay Optimization Problem #2**

#### □ You are given:

- The size of the first inverter

- The size of the load that needs to be driven

#### □ Your goal:

- Minimize delay by finding optimal number and sizes of gates

- □ So, need to find N that minimizes:

$$t_p = N t_{inv} \left( \gamma + \sqrt[N]{C_L / C_{in}} \right)$$

### **Untangling the Optimization Problem**

□ Rewrite N in terms of fanout/stage *f*:

$$f^{N} = C_{L}/C_{in} \rightarrow N = \frac{\ln (C_{L}/C_{in})}{\ln f}$$

$$t_{p} = Nt_{inv} \left( \left( C_{L}/C_{in} \right)^{1/N} + \gamma \right) = t_{inv} \ln \left( C_{L}/C_{in} \right) \left( \frac{f + \gamma}{\ln f} \right)$$

$$\frac{\partial t_{p}}{\partial f} = t_{inv} \ln \left( C_{L}/C_{in} \right) \cdot \frac{\ln f - 1 - \gamma / f}{\ln^{2} f} = 0$$

$$f = \exp(1 + \gamma / f) \quad \text{(no explicit solution)}$$

For

$$\gamma = 0, f = e, N = \ln (C_L/C_{in})$$

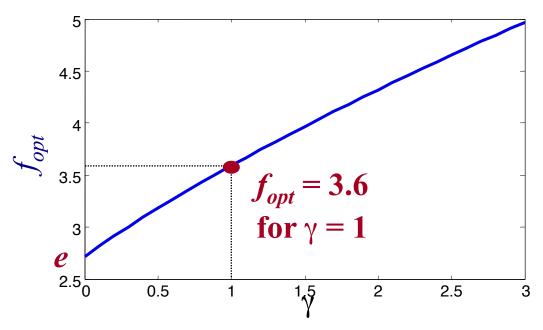

### **Optimum Effective Fanout** *f*

#### • Optimum f for given process defined by $\gamma$ $f = \exp(1 + \gamma / f)$

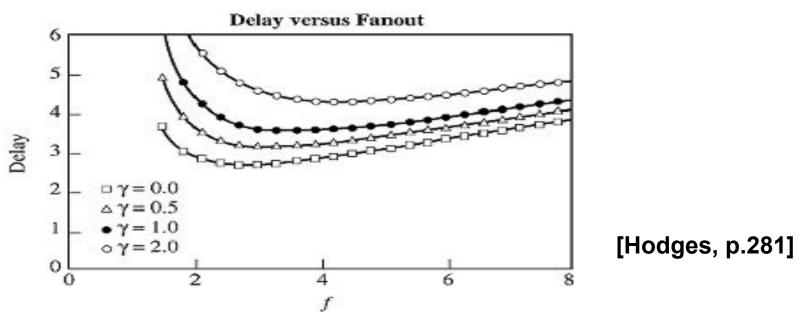

# In Practice: Plot of Total Delay

□ Why the shape?

$\Box$  Curves very flat for f > 2

Simplest/most common choice: f = 4

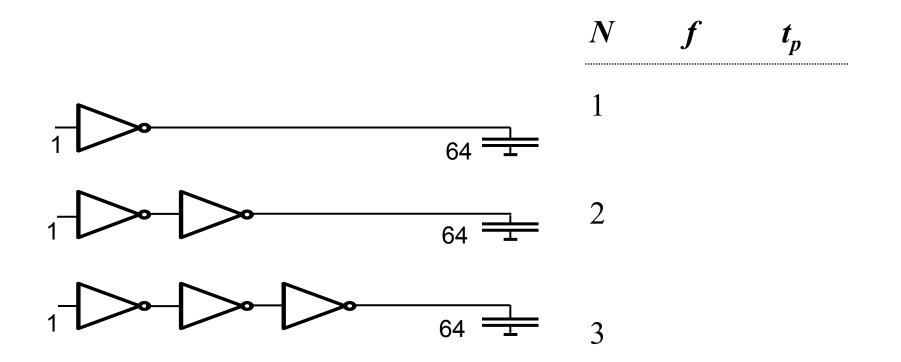

### Normalized Delay As a Function of F

$$t_p = N t_{inv} \left( \gamma + \sqrt[N]{F} \right), F = C_L / C_{in}$$

| F      | Unbuffered | Two Stage | Inverter Chain |

|--------|------------|-----------|----------------|

| 10     | 11         | 8.3       | 8.3            |

| 100    | 101        | 22        | 16.5           |

| 1000   | 1001       | 65        | 24.8           |

| 10,000 | 10,001     | 202       | 33.1           |

**(**γ = **1)**

[Rabaey: page 210]

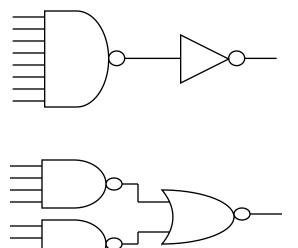

**Buffer Design**

How to best combine logic and drive for a big capacitive load?

### **Question #2**

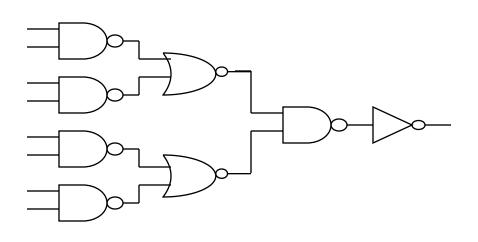

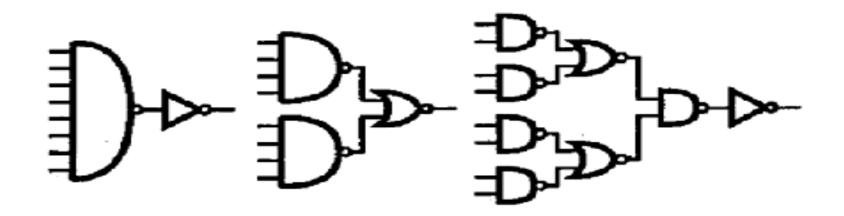

#### □ All of these are "decoders"

Which one is "best"?

#### Method to answer both of these questions

#### Extension of buffer sizing problem

Logical effort

# **Complex Gate Sizing**

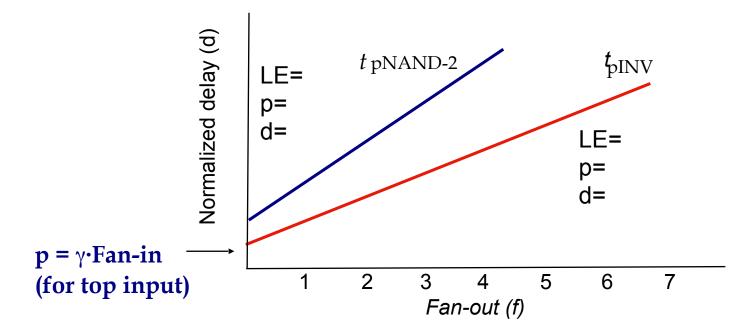

### **Complex Gate Sizing: NAND-2 Example**

$$C_{gnand} = 4C_G = (4/3) C_{ginv}$$

$$C_{dnand} = 6C_D = 6\gamma C_G = 2\gamma C_{ginv}$$

$$f = C_L/C_{gnand} = (3/4) C_L/C_{ginv}$$

$$t_{pNAND} = kR_N(C_{dnand} + C_L)$$

=  $kR_N(2\gamma C_{ginv} + C_L)$

=  $kR_N C_{ginv} (2\gamma + C_L/C_{ginv})$

=  $t_{inv} (2\gamma + (4/3)f)$

# Logical Effort

- Defines ease of gate to drive external capacitance

- Inverter has the smallest logical effort and intrinsic delay of all static CMOS gates

- Logical effort LE is defined as:

- $(R_{eq,gate}C_{in,gate})/(R_{eq,inv}C_{in,inv})$

- Easiest way to calculate (usually):

- Size gate to deliver same current as an inverter, take ratio of gate input capacitance to inverter capacitance

- □ LE increases with gate complexity

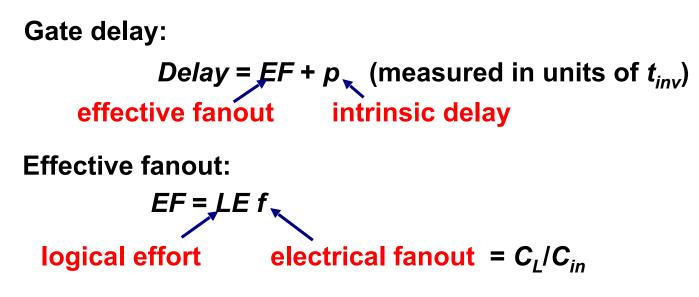

# **Logical Effort**

$$t_{pgate} = t_{inv} \left( p + LEf \right)$$

Measure everything in units of  $t_{inv}$  (divide by  $t_{inv}$ ):

p – intrinsic delay - gate parameter ≠ f(W) LE – logical effort – gate parameter ≠ f(W) f – electrical fanout = C<sub>L</sub>/C<sub>in</sub> = f (W)

Normalize everything to an inverter:  $LE_{inv} = 1$ ,  $p_{inv} = \gamma$

### **Delay of a Logic Gate**

Logical effort is a function of topology, independent of sizing Effective fanout is a function of load/gate size

### **Logical Effort of Gates**

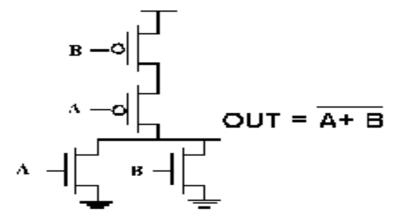

# **Delay Of NOR-2 Gate**

- 1. Size for same resistance as inverter

- 2. LE = ratio of input cap of gate versus inverter

Intrinsic capacitance  $(C_{dnor}) = t_{pint} (NOR) =$

#### Question

Any logic function can be implemented using NOR gates only or NAND gates only!

Which of the two approaches is preferable in CMOS (from a performance perspective)?

# Logical Effort

### Logical Effort Designing Past Cattor Circuits

Ivan Sutherland Bob Sprcull David Harris

| Gate Type   | Number of Inputs |     |     |            |  |

|-------------|------------------|-----|-----|------------|--|

|             | 1                | 2   | 3   | n          |  |

| Inverter    | 1                |     |     |            |  |

| NAND        |                  | 4/3 | 5/3 | (n + 2)/3  |  |

| NOR         |                  | 5/3 | 7/3 | (2n + 1)/3 |  |

| Multiplexer |                  | 2   | 2   | 2          |  |

| XOR         |                  | 4   | 12  |            |  |

#### [From Sutherland, Sproull, Harris]

#### Optimizing Complex Combinational Logic

# Multistage Networks

$$Delay = \sum_{i=1}^{N} (p_i + LE_i \cdot f_i)$$

Effective fanout:  $EF_i = LE_i f_i$

Only for tree networks

Path delay  $D = \Sigma d_i = \Sigma p_i + \Sigma EF_i$

Path electrical fanout:  $F = C_L/C_{in} = \Pi f_i$

Path logical effort:  $\Pi LE = LE_1 LE_2 ... LE_N$

Path effort:  $PE = \prod LE F$

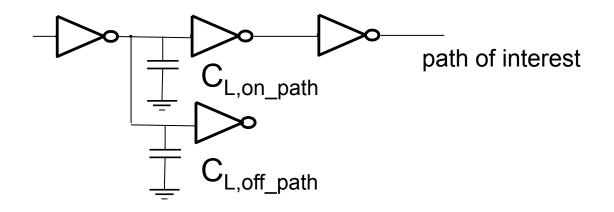

# **Adding branching**

Branching effort:

$$b = \frac{C_{L,on-path} + C_{L,off-path}}{C_{L,on-path}}$$

### Multistage Networks

$$Delay = \sum_{i=1}^{N} (p_i + LE_i \cdot f_i)$$

Effective fanout:  $EF_i = LE_i f_i$ Path delay  $D = \Sigma d_i = \Sigma p_i + \Sigma EF_i$ Path electrical fanout:  $F = C_L / C_{in}$ Branching effort:  $\Pi B = b_1 b_2 ... b_N$   $\Pi f_i = \Pi B F$  (assuming all paths in the tree are important) Path logical effort:  $\Pi LE = LE_1 LE_2 ... LE_N$ Path effort:  $PE = \Pi LE \Pi B F$

# **Optimum Effort per Stage**

When each stage bears the same effort (effective fanout):

$$EF^N = PE$$

$$EF = \sqrt[N]{PE}$$

Effective fanouts:  $LE_1f_1 = LE_2f_2 = \dots = LE_Nf_N$

Minimum path delay

$$\hat{D} = \sum_{i=1}^{N} (LE_i f_i + p_i) = N \cdot PE^{1/N} + \sum_{i=1}^{N} p_i$$

# **Optimal Number of Stages**

For a given load, and given input capacitance of the first gate Find optimal number of stages and optimal sizing

$$D = N \cdot P E^{1/N} + \sum p_i$$

Remember: we can always add inverters to the end of the chain

The 'best effective fanout'  $EF = PE^{1/\hat{N}}$  is still around 4 (3.6 with  $\gamma$ =1)

# Method of Logical Effort: Summary

- □ Compute the path effort:  $PE = (\Pi LE)BF$

- □ Find the best number of stages  $N \sim \log_4 PE$

- Compute the effective fanout/stage EF = PE<sup>1/N</sup>

Sketch the path with this number of stages

- □ Work either from either end, find sizes:  $C_{in} = C_{out}^* LE/EF$

Reference: Sutherland, Sproull, Harris, "Logical Effort", Morgan-Kaufmann 1999.

Optimizing Complex Combinational Logic: Examples

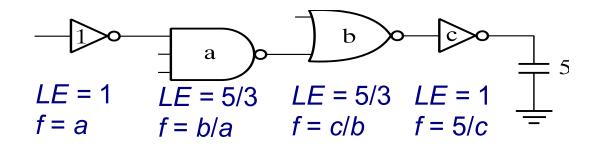

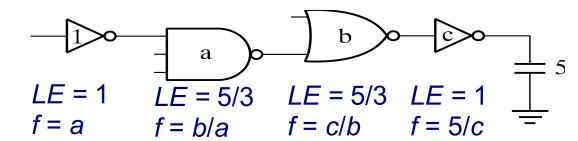

#### **Example 1: No branching**

Electrical fanout, F = II LE = PE = EF/stage = a = b = c =

#### **Example 1: No branching**

a, b, c are input capacitances normalized to the unit inverter

| Electrical fanout, $F = 5$<br>$\Pi LE = 25/9$ |                                    |

|-----------------------------------------------|------------------------------------|

| PE = 125/9                                    | From the back                      |

| <i>EF/stage</i> = 1.93<br><i>a</i> = 1.93     | 5/c = 1.93                         |

| b = 2.23<br>c = 2.59                          | (5/3)c/b = 1.93<br>(5/3)b/a = 1.93 |

### Our old problem: which one is better?

LE=10/31LE=25/3LE=4/35/34/31 $\Pi LE = 10/3$  $\Pi LE = 10/3$  $\Pi LE = 80/27$ P = 8 + 1P = 4 + 2P = 2 + 2 + 2 + 1

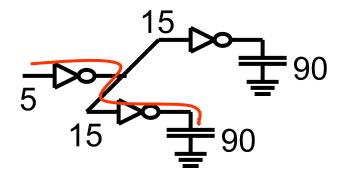

# **Adding Branching**

LE = 1 F = 90/5 = 18PE = 18 (wrong!)

$$EF_1 = (15+15)/5 = 6$$

$FF_2 = 90/15 = 6$

$$F_2 = 90/15 = 6$$

$$PE = 36, not 18!$$

Better:  $PE = F \cdot LE \cdot B = 18 \cdot 1 \cdot 2 = 36$

### Example 2 with Branching

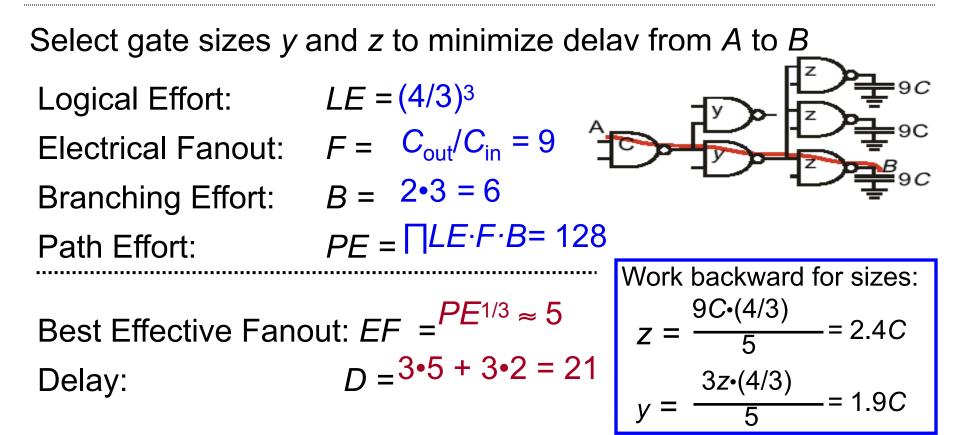

Select gate sizes y and z to minimize delaw from A to B

- Logical Effort: LE =

- Electrical Fanout: F =

- Branching Effort: B =

- Path Effort: PE =

Best Effective Fanout: *EF* = Delay: *D* =

### Example 2 with Branching