## EECS 151/251A Homework 5

Due Monday, March  $5^{\rm th},\,2018$

### Problem 1: Timing

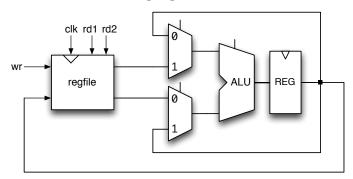

The data-path shown below is used in a simple processor.

The elements used in the design have the following timing characteristics. The worst case clock skew is 1ns. For this problem you can ignore the delay in the controller.

|          | setup-time     | clock-to-q | CL delay |

|----------|----------------|------------|----------|

| regfile  | $2\mathrm{ns}$ | 2ns        | -        |

| register | 1ns            | 1ns        | -        |

| mux      | -              | -          | 1ns      |

| ALU      | -              | -          | 5ns      |

- 1. What is the minimum clock period for this design? Show your work.

- 2. Can you improve the clock frequency by rearranging the elements in the data-path (and adding more hardware if needed), but keeping the same function? If so, what is the new minimum clock period? Show your design.

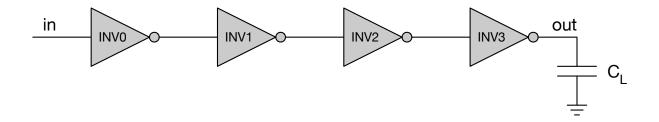

# Problem 2: Inverter Sizing

#### Part a

Size inverters INV1, INV2, and INV3 in the following circuit for minimum delay. Assume  $C_{INV0} = 2fF$  and  $C_L = 162fF$  and that there is no interconnect capacitance.

#### Part b

What is the total delay from in to out in part a? Use the simple MOSFET switch model, and assume each inverter is sized such that  $R_{ON,N}=R_{ON,P}$  and  $V_{th,N}=|V_{th,P}|=\frac{V_{DD}}{2}$ . Assume that gate capacitance  $C_G$  and the explicit load  $C_L$  are the only sources of capacitance.  $R_{ON}$  for INVO is  $2.4k\Omega$

### Problem 3: Wires and Repeaters

You have two circuits on chip, A and B, that are physically located 10 mm (Manhattan distance) apart. With the following process parameters, design a chain of repeaters that minimizes the delay from A to B. Design the repeaters so that the rising and falling transitions are symmetrical. Do not worry about whether or not the signal is inverted; you may assume that the circuit B can invert the signal if needed. For your answer, include the device sizes in each repeater (including the driver inside A) and the dimensions of each wire segment.

Wire parameters:

$$R_{sheet} = 50m\Omega/\Box$$

$$C_{pp} = 1.8 fF/\mu m^2$$

$$C_{fringe} = 0.01 fF/\mu m$$

$$W_{min} = 50nm$$

Device parameters:

$$R_{on,n} = 2k\Omega \cdot \frac{L}{W}$$

$$R_{on,p} = 4k\Omega \cdot \frac{L}{W}$$

$$\gamma = 1$$

$$L_{min} = 50nm$$

$$W_{min} = 100nm$$

$$C_{gate} = 200 fF/\mu m^2$$

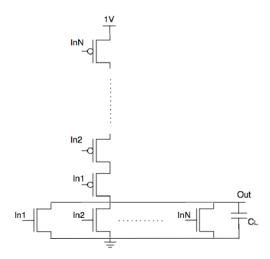

### Problem 4: Power and Leakage

Consider an N-input NOR gate shown below with  $V_{DD} = 1V$ ,  $C_L = 5fF$ ,  $C_D = 2fF/\mu m$ . Assume  $R_{ON,n} = 0.2m\Omega \cdot \mu m$ ,  $R_{ON,p} = 0.3m\Omega \cdot \mu m$ ,  $R_{OFF,n} = 100k\Omega \cdot \mu m$ ,  $R_{OFF,p} = 1.5M\Omega \cdot \mu m$  for the given device length. You may assume N > 2 and you don't have to worry about extreme cases (i.e. an unreasonably large N).

- a) Size the gate, using as a reference a symmetrically sized inverter with  $W_n = 1\mu m$ . Express your answer as a function of N.

- b) Assume that the probability of an input being high is 0.5 (i.e., on any given clock cycle, each input is equally likely to be a 0 or a 1.) and that all inputs are independent. What is the probability that the output is high, P(Out = 1)? What is the probability that the output is low, P(Out = 0)? What is the gate activity factor (i.e. the probability that the output will transition from low to high,  $P_{0\to 1}$ )? (Again, you may express your answer as a function of N.)

- c) What is the dynamic power dissipation of the gate as a function of N, if the clock frequency is 3GHz? You may ignore the parasitic drain capacitance in the internal nodes of the PMOS stack, but not at the output.

- d) **EECS 251A Only.** For the following three cases, calculate the leakage current. Express your answer as a function of N when needed. An approximate expression is perfectly fine as long as you explain and justify your assumptions/simplifications.

- All inputs are zero.

- All inputs are 1.

- One of the inputs is 1, and the rest are zero.

### Problem 5: Gate Delays

#### Part a

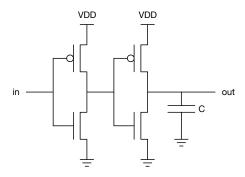

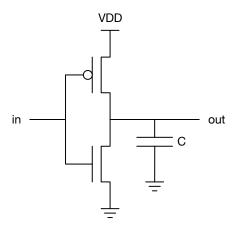

Using the transistor switch model, draw the output of the circuit below for a 0 to VDD input step. Calculate the propagation delay in terms of the given parameters. Assume that  $|V_{th,p}| = V_{th,n} = VDD/2$  and that  $R_{on,p} = R_{on,n}$ . You may ignore  $R_{off}$ .

#### Part b

Using the transistor switch model, draw the step response (0 to VDD) of the circuit below. Calculate the propagation delay in terms of the given parameters. Assume that  $|V_{th,p}| = V_{th,n} = VDD/2$  and that  $R_{on,p} = R_{on,n}$ . Assume that  $C_{gs,p} = 2 * C_{gs,n}$  and that  $C_{gs}$  is the only significant source of capacitance. You may ignore  $R_{off}$ .