# EECS 150 Spring 2003

# Lab Lecture 4 Verilog Design Synthesis 2/13/2003

Greg Gibeling (Original By Sandro Pintz, Adaptions from John Wawryznek)

#### **Today**

- "Think Hardware"

- Tips for making EECS150 an easy class

- Simulation

- Blocking vs Non-Blocking

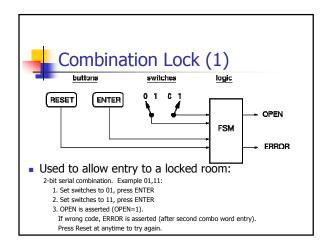

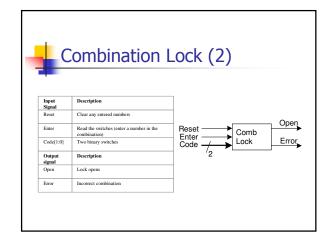

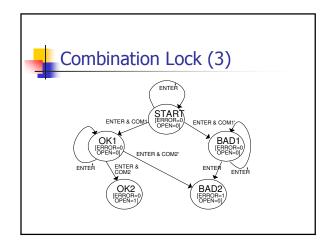

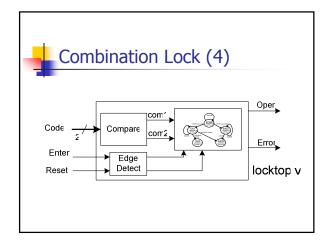

- The Combo Lock

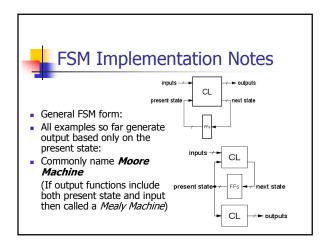

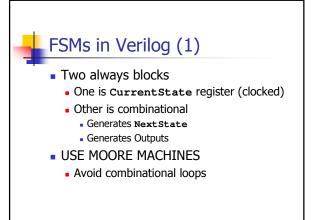

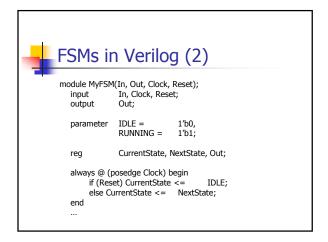

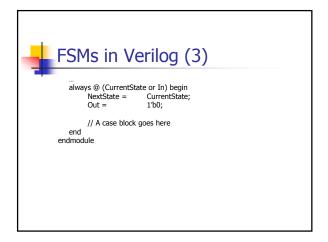

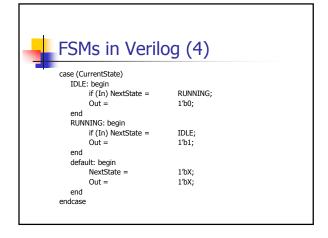

- FSMs in Verilog

- Kramnik!

#### **MOTIVATION**

- Finite State Machine Design

- Design Partitioning

- Design Entry

- Synthesis

- Mapping, Placing and Routing

#### "Think Hardware" (1)

if (a) aux = B; else aux = C; Z = A + aux;

#### "Think Hardware" (2)

assign Z = A + (2 \* A);assign Z = A + (A << 1);

assign  $Z = A + \{A, 1'b0\};$

# assign $Z = \{aux, A[0]\};$ **A[**n-1:1]

"Think Hardware" (3)

assign aux =  $\{1'b0, A[n-1:1]\} + A;$

### Simulation (1)

- Event Driven Simulation

- Order of execution in time tick is not fixed

- Simulator dependent (ouch!)

- Deadlocks can happen in perfectly good design

- Simulation and Synthesis can differ functionally

# Simulation (2)

- When an event happens put in queue

- When bored get next event

- Figure out the consequences

- This means non-blocking assignments really are executed in any old order, but the results are as-if they were executed in parallel

#### Administrativia

- Midterm!

- Thursday 2/19/2004 in class

- ALL LECTURE MATERIAL COVERED

- Emphasis on material 2/12 and before

- TA Review Session

- Monday is a holiday

- Come to any other lab/discussion

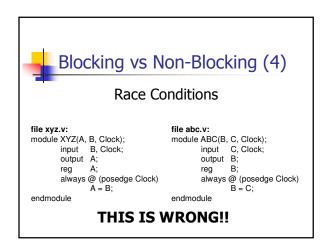

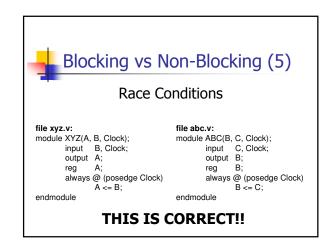

# Blocking vs Non-Blocking (1)

```

always @ (b) begin a = b; c = a; end

Result c = a = b

always @ (posedge Clock) begin a <= b; c <= a; end

Result: a = (old?) b

end c = old a

```

#### Blocking vs Non-Blocking (2)

•Use Non-Blocking for FlipFlop Inference:

- posedge/negedge require nonblocking

- Otherwise synthesis and simulation will not match

- ■Use "#1" to visual causality!

```

always @ (posedge Clock) begin

b <= #1 a; /* b and c will be flip flops */

c <= #1 b;

end

```

# Blocking vs Non-Blocking (3)

If you use Blocking for FlipFlops:

#### You will not get what you want

```

always @ (posedge Clock) begin

b = a; /* Only c will be a flip flop, */

c = b; /* b will go away after synthesis. */

end

/* 'b' is not needed at all */

always @ (posedge Clock) begin

c = b; /* c and b will be flip flops */

b = a;

```

• We're still upgrading software