**EECS 150 -- Digital Design**

Lecture 4 – Synchronous Digital Systems Review (Part II)

> 2010-1-28 John Wawrzynek

Today's lecture by John Lazzaro

#### www-inst.eecs.berkeley.edu/~cs150

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

<u>EECS150 – Digital Design</u> <u>Lecture 4 – Synchronous</u> <u>Digital Systems Review Part 2</u>

January 28, 2010

John Wawrzynek Electrical Engineering and Computer Sciences University of California, Berkeley

http://www-inst.eecs.berkeley.edu/~cs150

Spring 2010

EECS150 lec04-SDS-review2

Page 2

## <u>Outline</u>

- Topics in the review, you have already seen in CS61C, and possibly EE40:

- 1. Digital Signals.

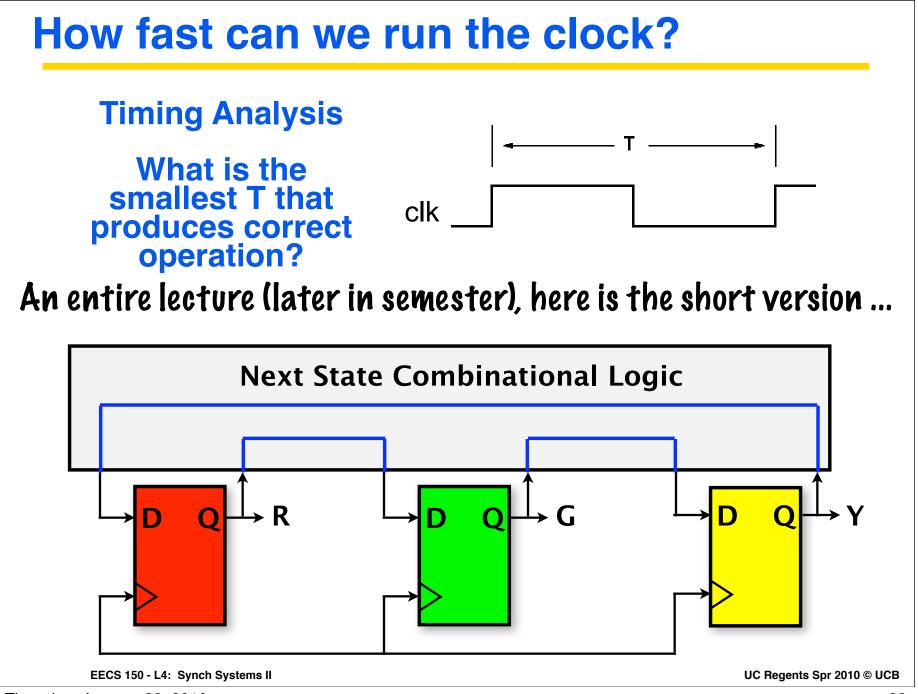

- 2. General model for synchronous systems.

- 3. Combinational logic circuits

- 4. Flip-flops, clocking

Spring 2010

EECS150 lec04-SDS-review2

Page 3

### **Today's Lecture**

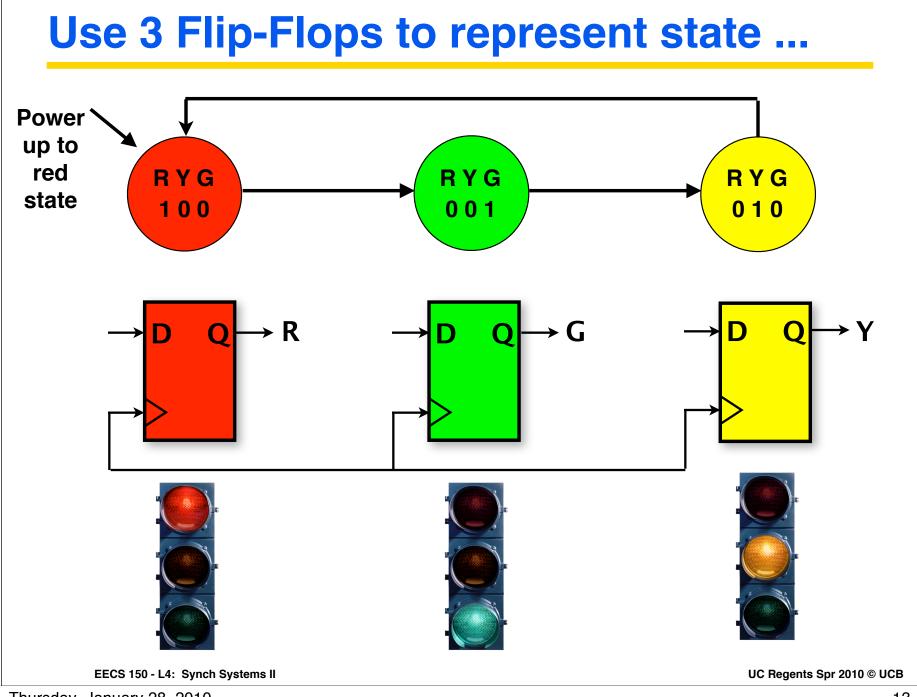

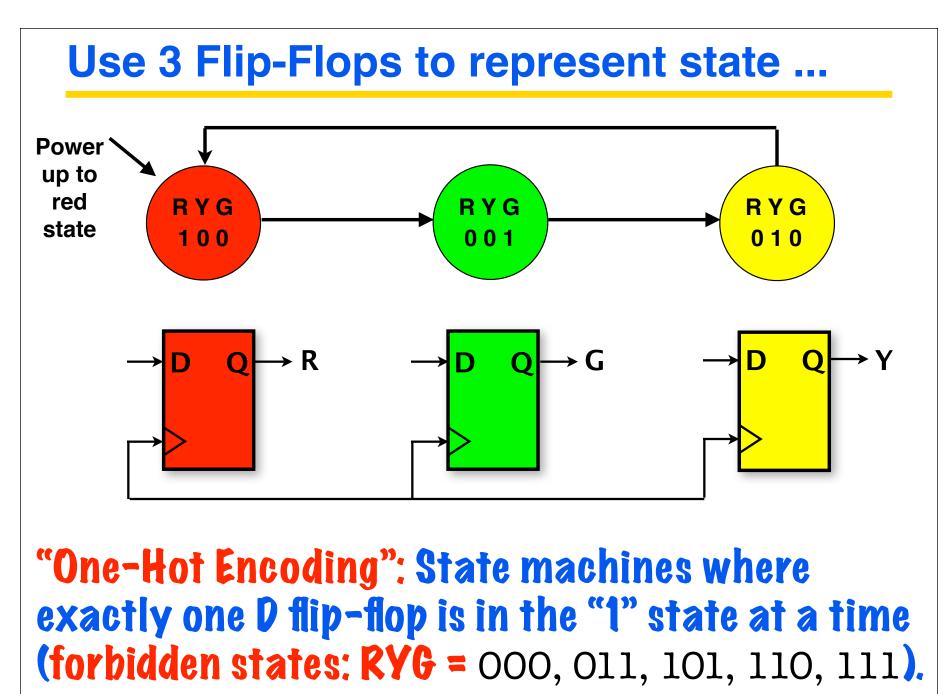

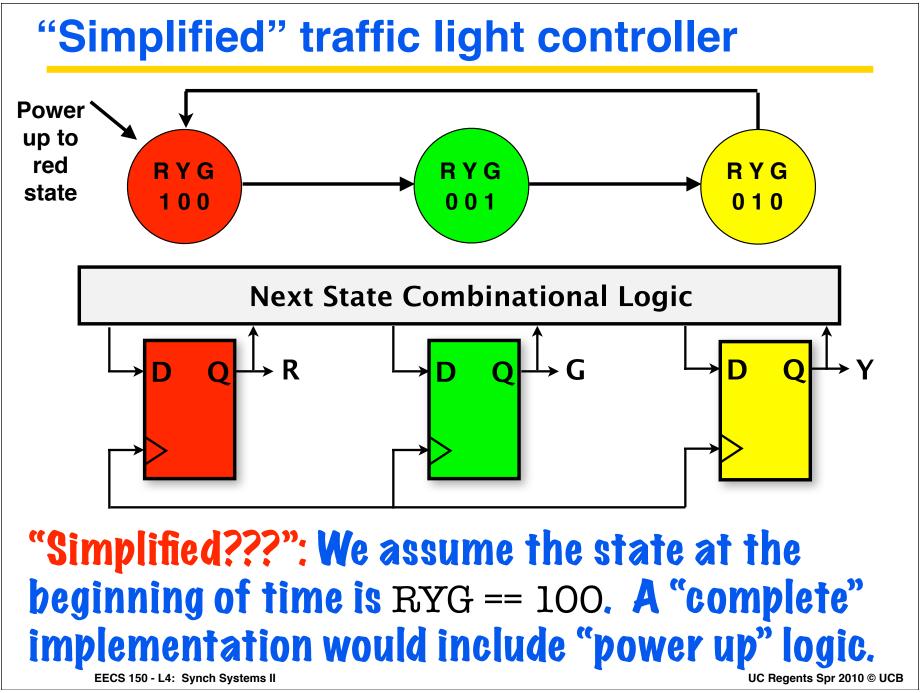

# Flip-flop-based state machines Operates on Boolean (single-bit) values.

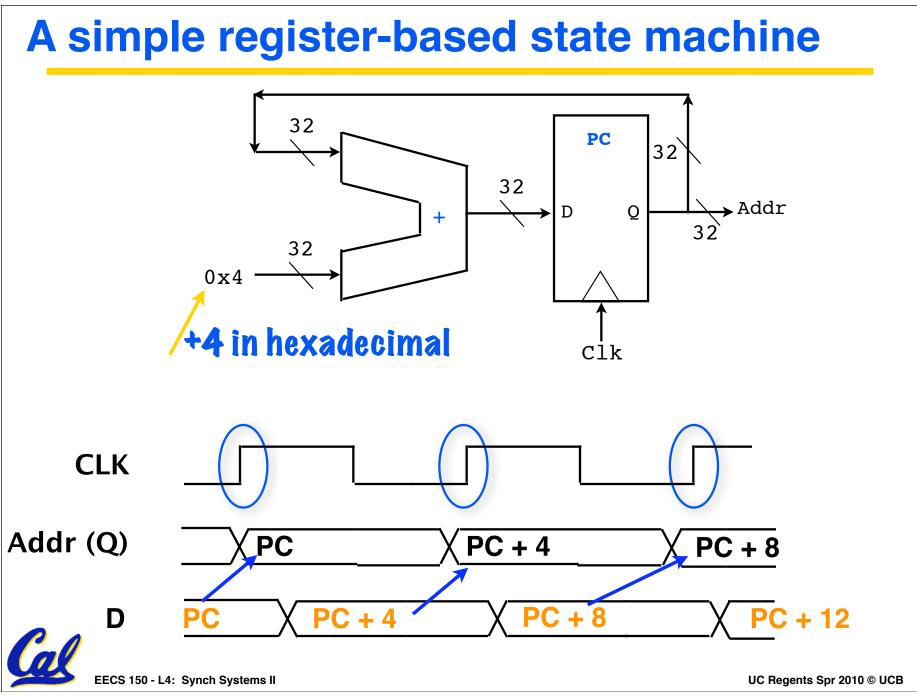

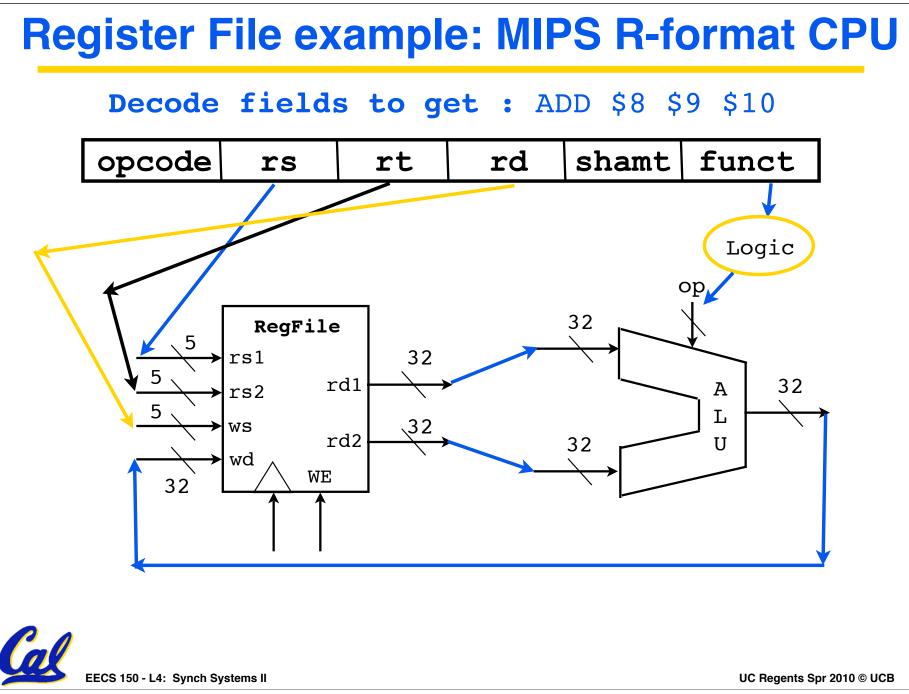

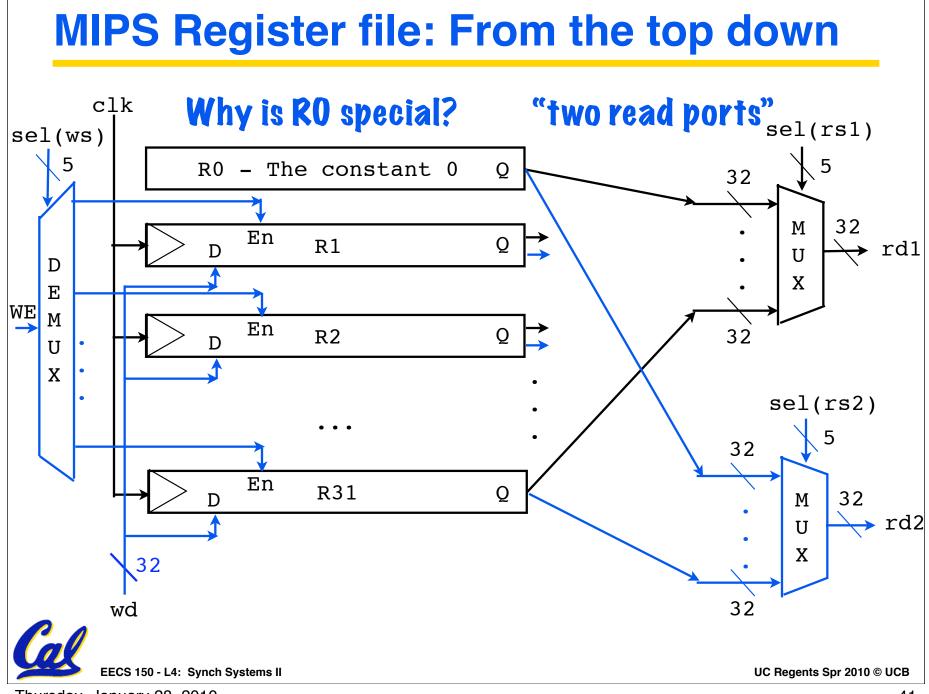

Register-based state machines Operates on multi-bit values (integers, CPU instruction, ...)

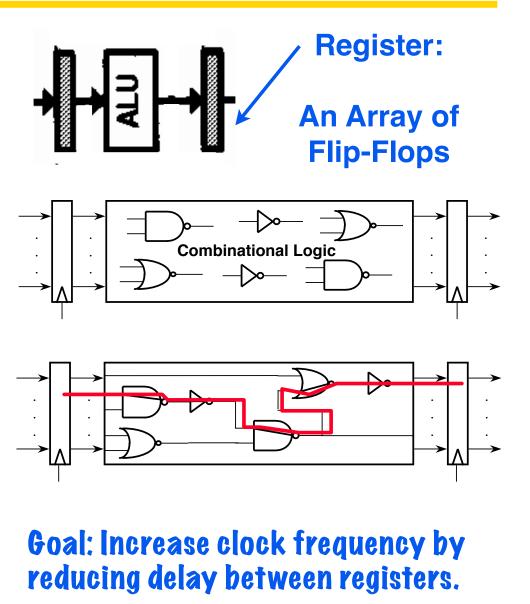

## **Registers and Pipelining**

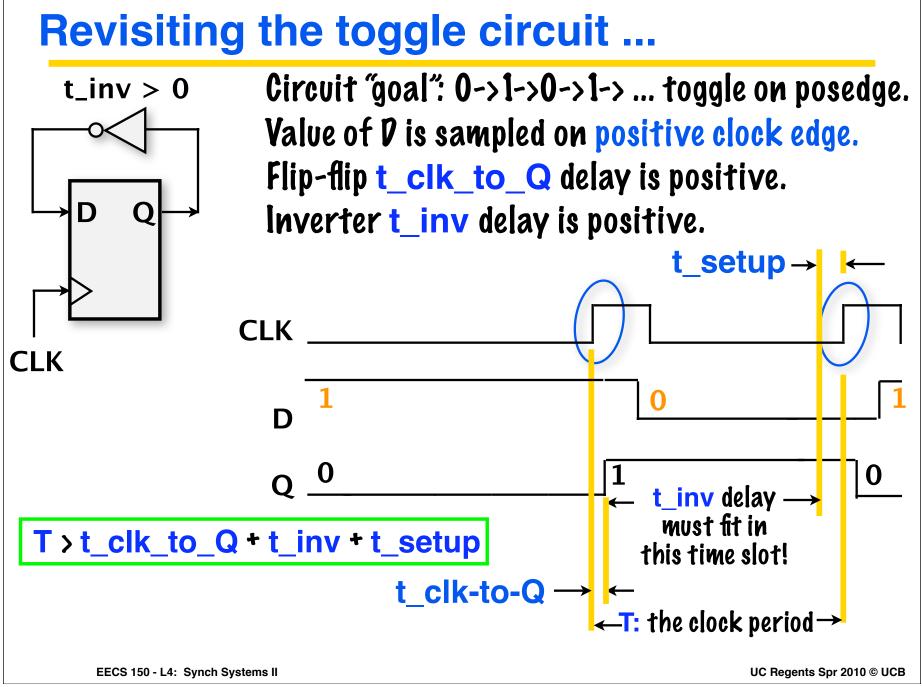

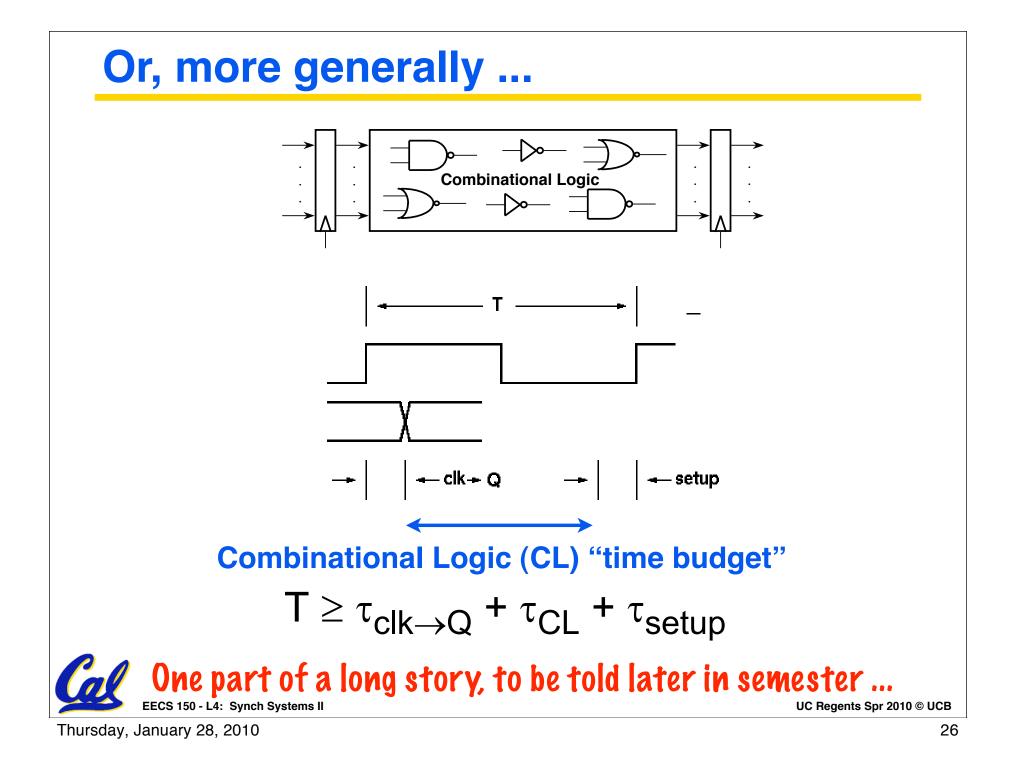

Adding state to speed up the clock.

## Flip-flop details ...

(Reset, set, etc ...)

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

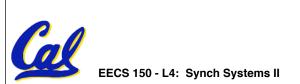

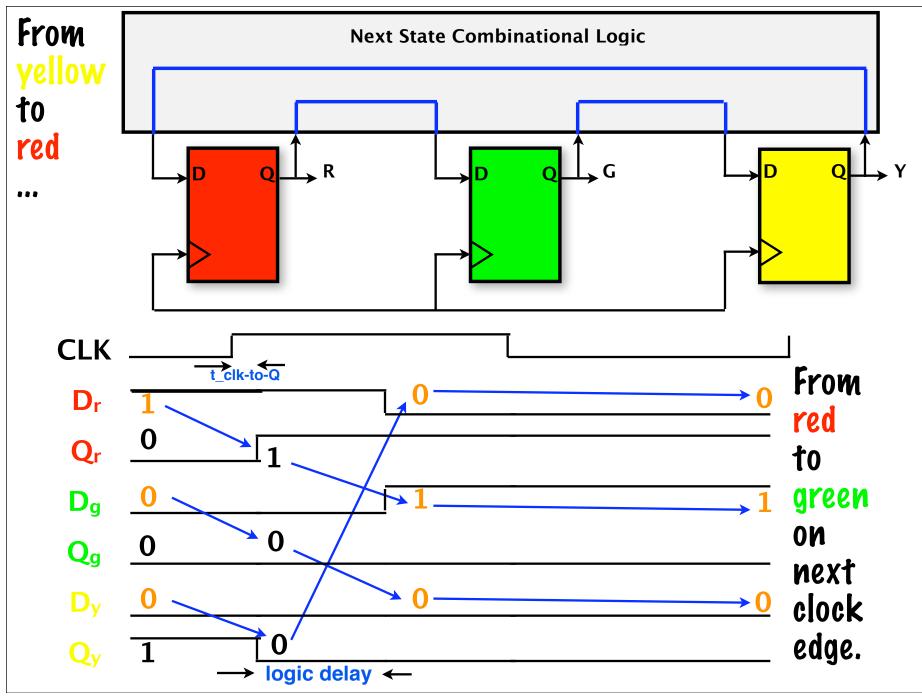

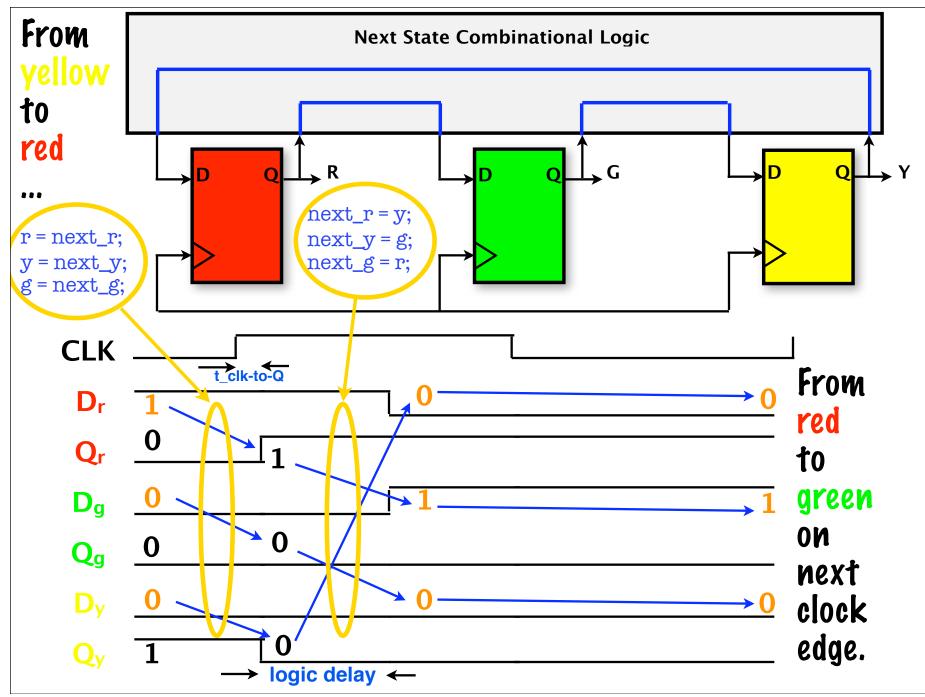

## **Flip-Flop State Machines**

UC Regents Spr 2010 © UCB

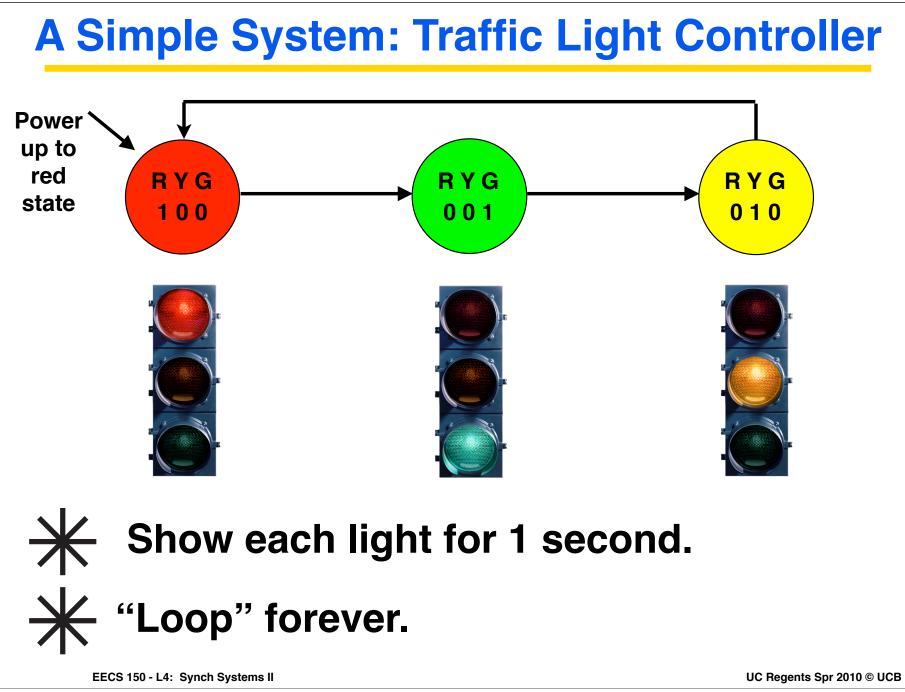

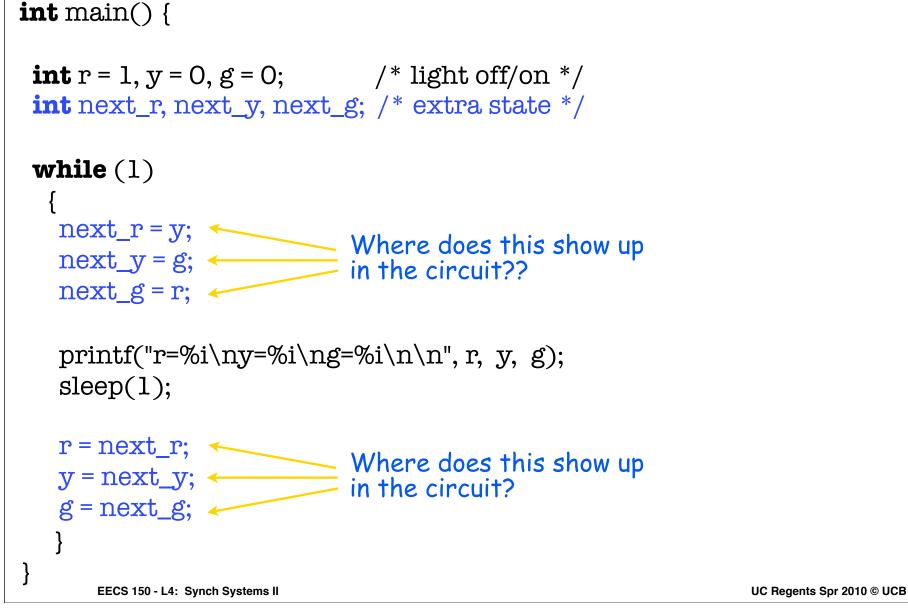

#### **'C' program for traffic light controller**

### **'C' program for traffic light controller**

| <pre>int main() {</pre>                                                           | % ./TRAFFIC<br>R=1               |

|-----------------------------------------------------------------------------------|----------------------------------|

| <pre>int r = 1, y = 0, g = 0;</pre>                                               | Y=0<br>G=0                       |

| <b>while</b> (1)                                                                  | R=0<br>Y=0                       |

| next_r = y; <b>Compute the "next"</b><br>next_y = g; <b>state for the traffic</b> | G=1                              |

| $next_g = r;$ light.                                                              | R=0<br>Y=1                       |

| printf("r=%i\ny=%i\ng=%i\n\n", r, y, g);                                          | G=0                              |

| <pre>sleep(1);</pre>                                                              | R=1<br>Y=0                       |

| r = next_r;<br>y = next_y;                                                        | G=0                              |

| g = next_g; the traffic light.                                                    | R=0                              |

| }                                                                                 | 9=0<br>- 1                       |

| }<br>EECS 150 - L4: Synch Systems II                                              | G=]<br>UC Regents Spr 2010 © UCB |

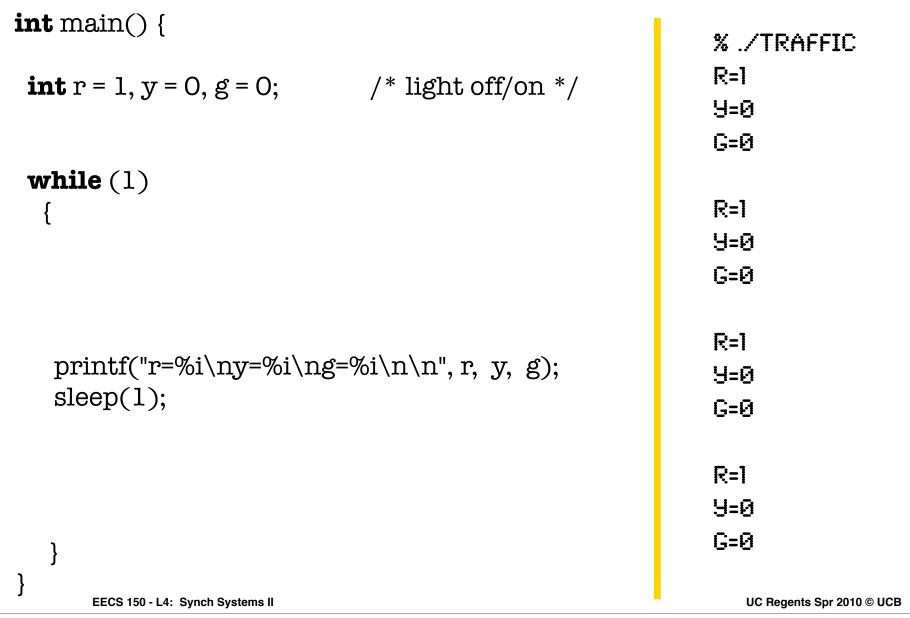

#### A few observations ...

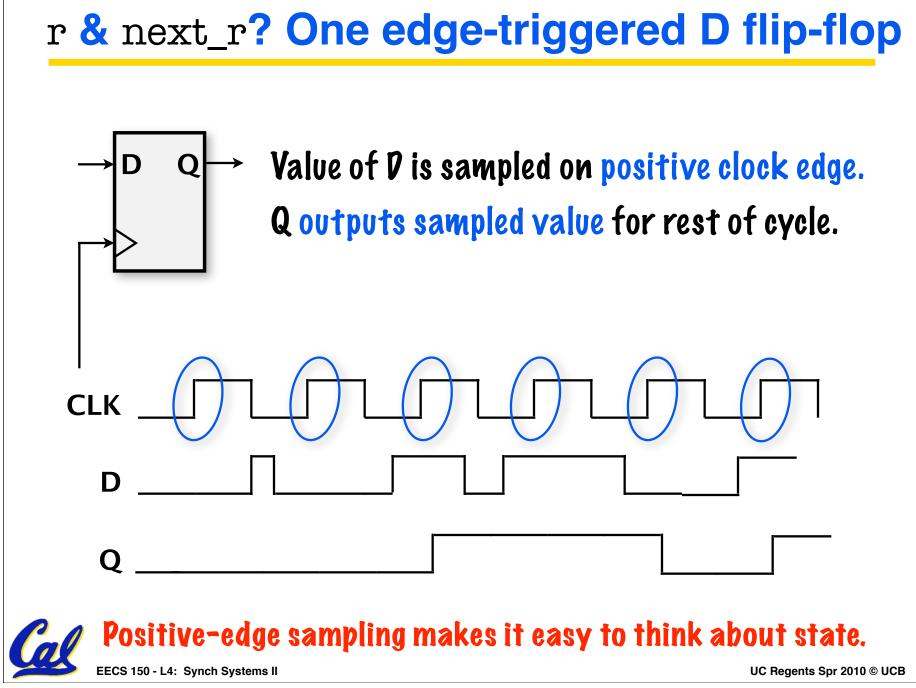

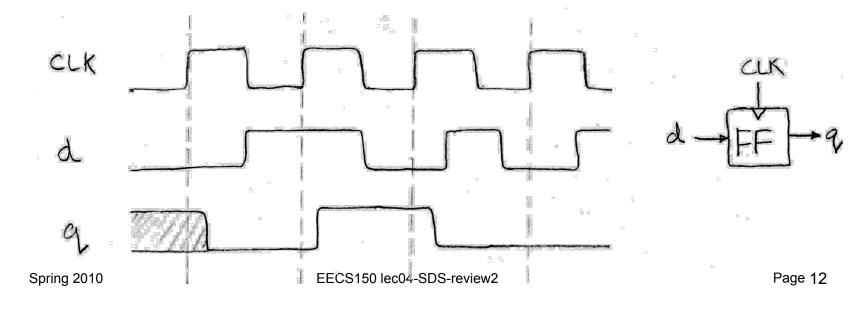

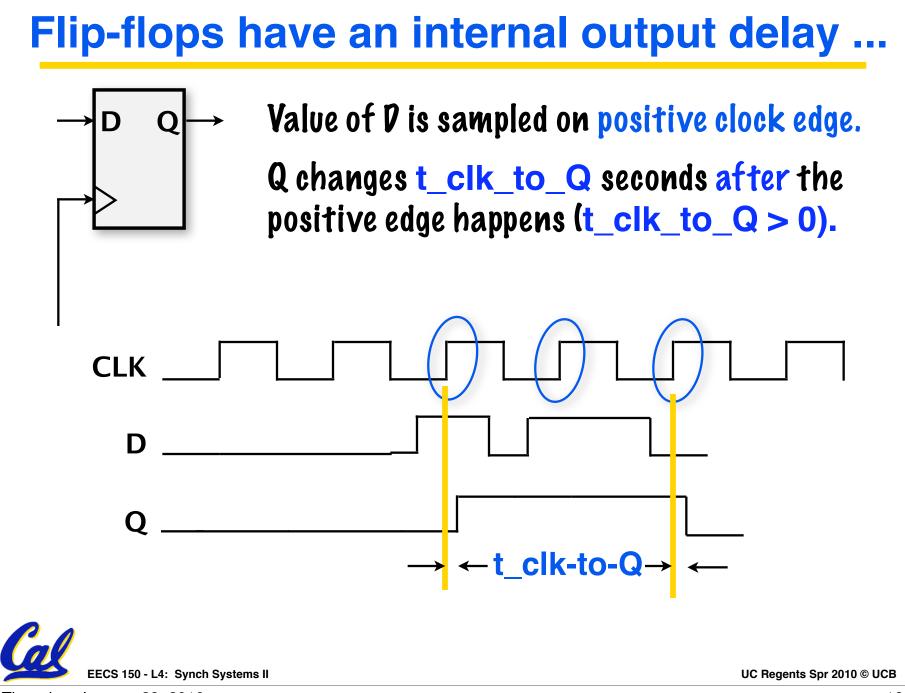

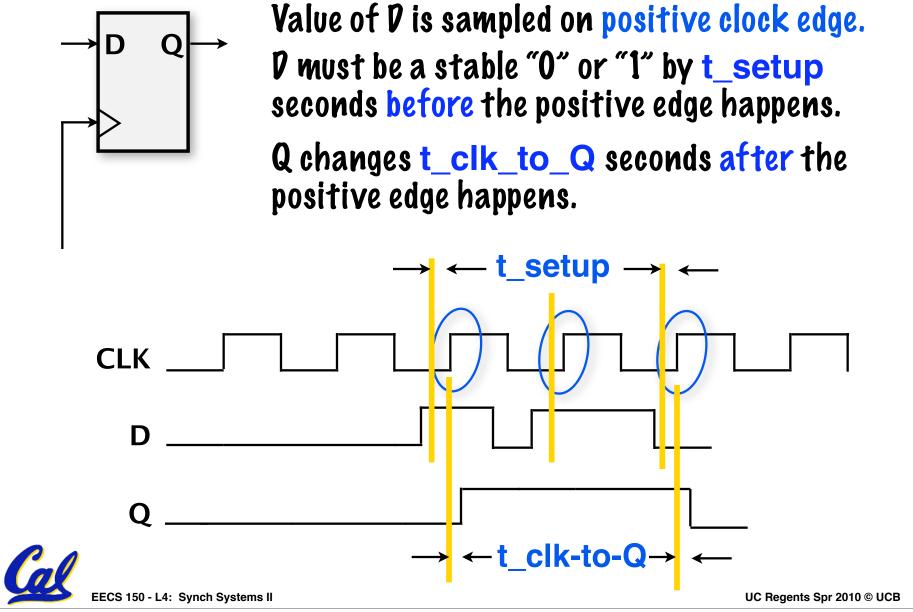

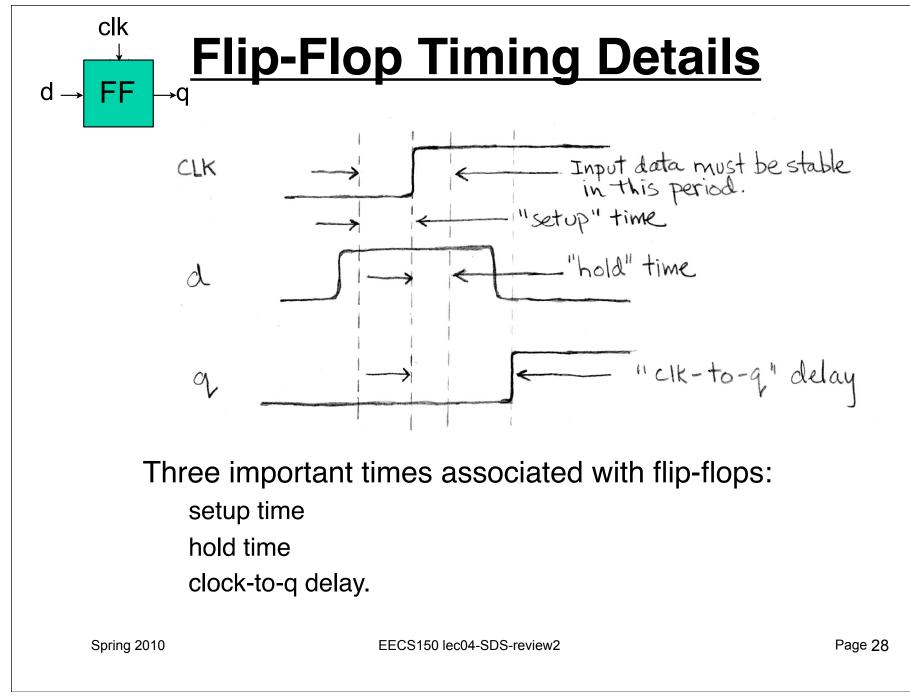

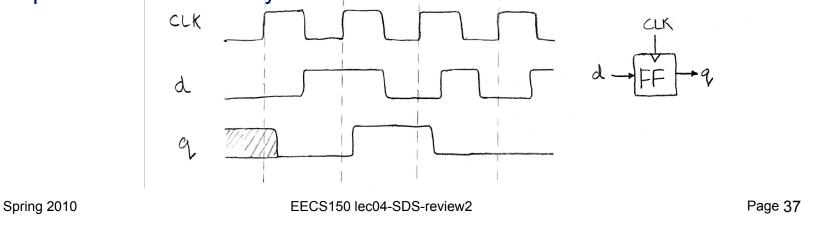

## Flip-flop Timing Waveforms?

- Edge-triggered d-type flip-flop

This one is "positive edge-triggered"

- "On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored."

- Example waveforms:

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

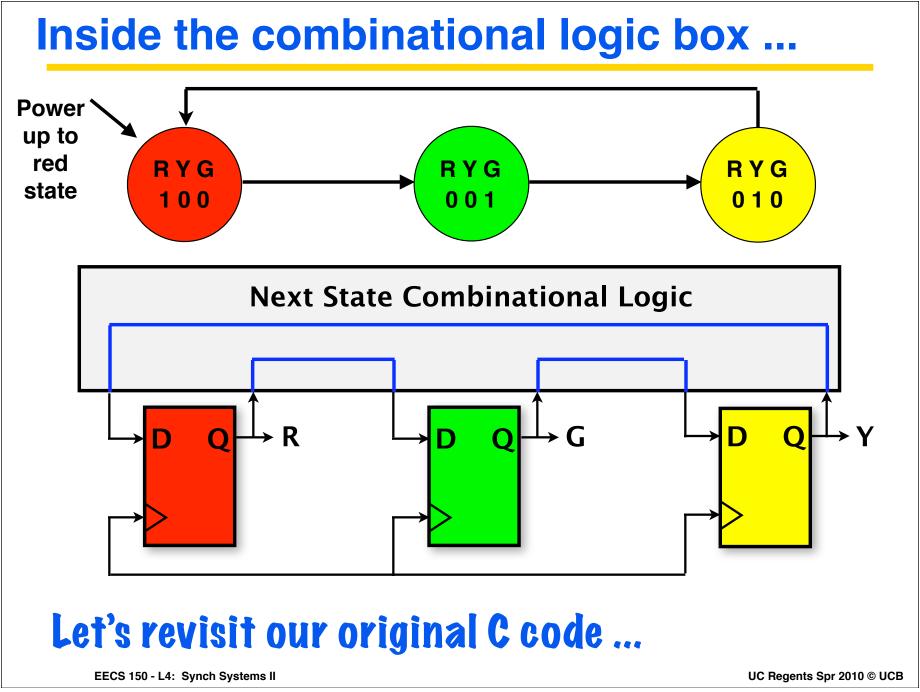

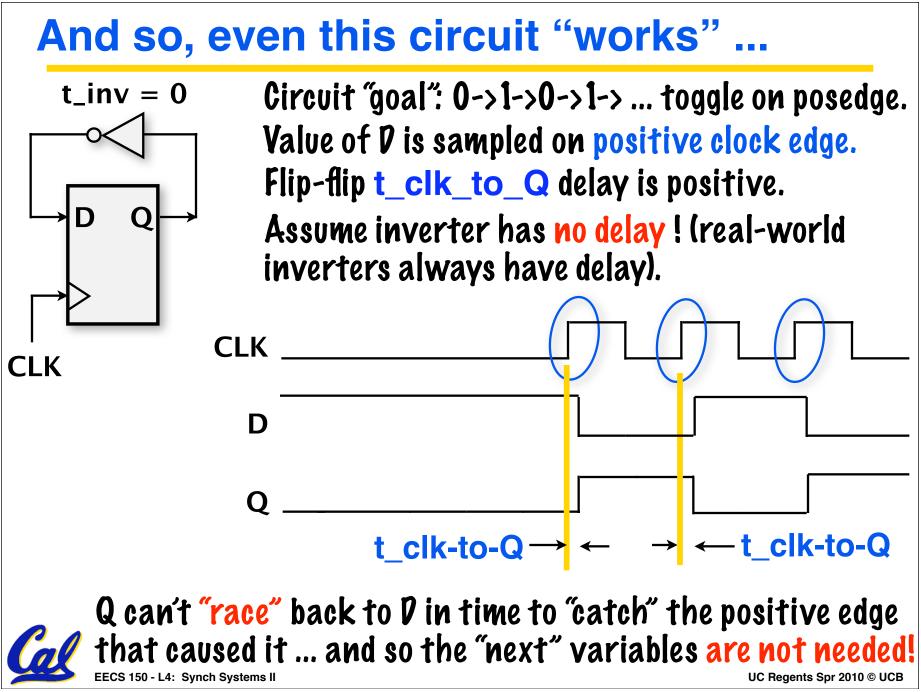

#### **Recall: A few observations ...**

```

int main() {

6 C variables, but

int r = 1, y = 0, g = 0; /* light off/on */

only 3 flip-flops.

How does that

int next_r, next_y, next_g; /* extra state */

work?

while (1)

next_r = y;

next_y = g;

next_g = r;

printf("r=\%i\ny=\%i\ng=\%i\n", r, y, g);

sleep(1);

r = next r;

y = next_y;

g = next_g;

UC Regents Spr 2010 © UCB

EECS 150 - L4: Synch Systems II

```

#### **Recall: A few observations ...**

#### D must stablize ahead of positive edge

## **Register State Machines**

UC Regents Spr 2010 © UCB

## State Elements: circuits that store info

Examples: registers, memories

Register: Under the control of the "load" signal, the register captures the input value and stores it indefinitely.

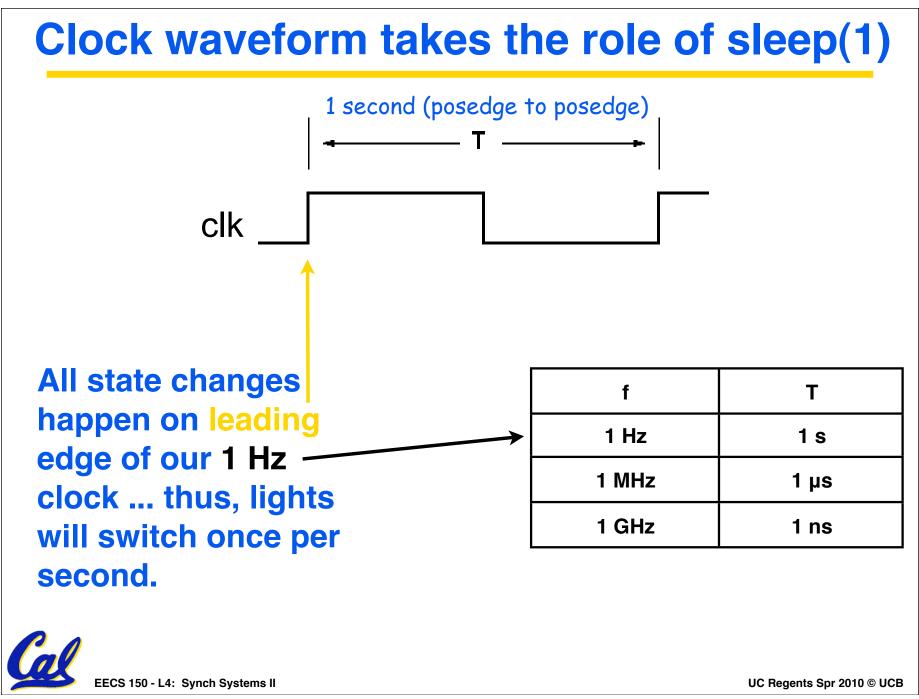

often replace by clock signal (clk)

- The value stored by the register appears on the output (after a small delay).

- Until the next load, changes on the data input are ignored (unlike CL, where input changes change output).

- These get used for short term storage (ex: register file), and to help move data around the processor.

Spring 2010

EECS150 lec04-SDS-review2

Page 31

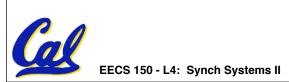

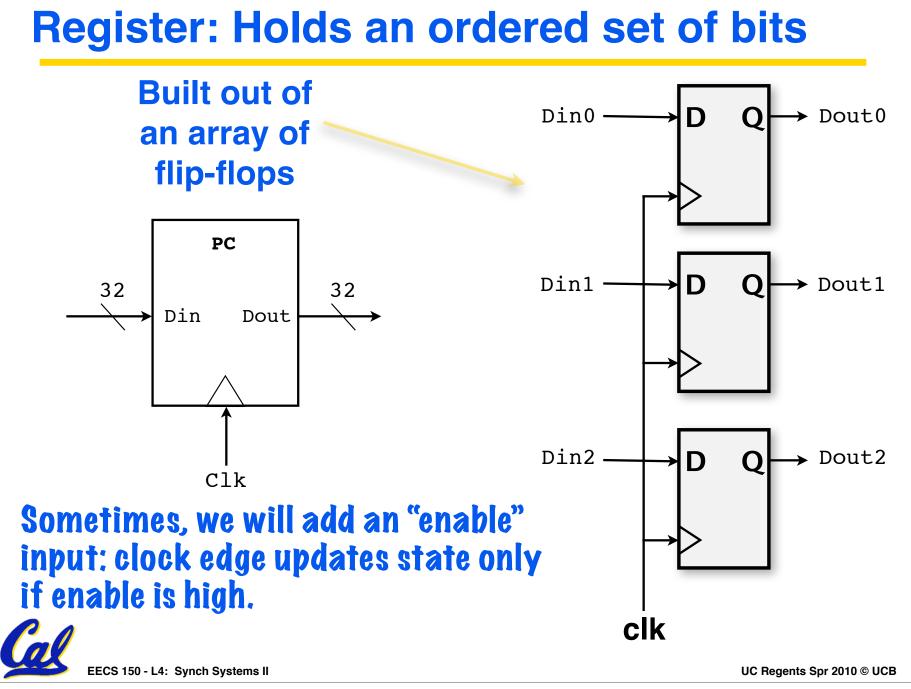

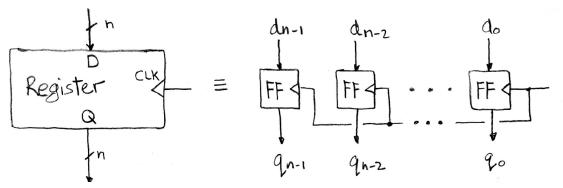

## **Register Details...What's inside?**

- n instances of a "Flip-Flop"

- Flip-flop name because the output flips and flops between and 0,1

- D is "data", Q is "output"

- Also called "d-type Flip-Flop"

Spring 2010

EECS150 lec04-SDS-review2

Page 32

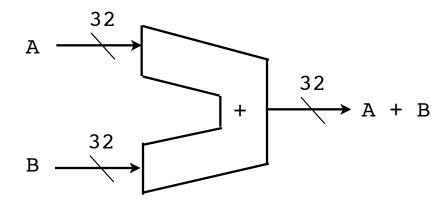

#### Multi-bit adder: Doing logic on an integer

Combinational: Put a A and B values on inputs, → A + B a short time later A + B appears on output.

Just like we use gates to operate on Q output of a flip-flop, we use components like multi-bit adders to operate on all output bits of a register.

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

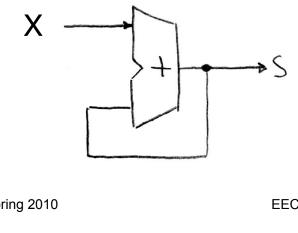

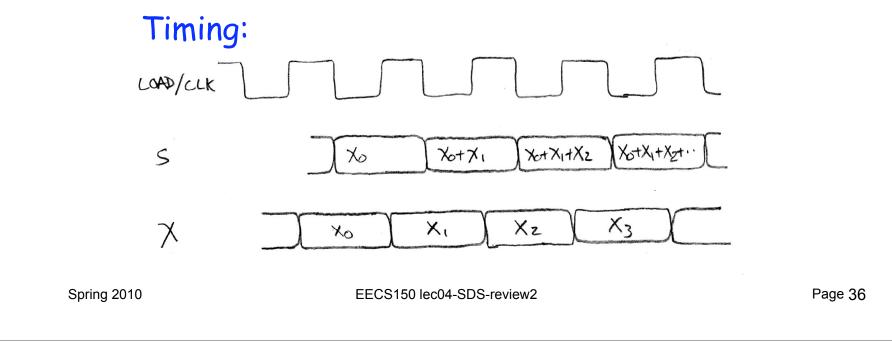

## **Accumulator Circuit Example**

Assume X is a vector of N integers, presented to the input of our accumulator circuit one at a time (one per clock cycle), so that after N clock cycles, S hold the sum of all N numbers.

$$\chi_i \rightarrow Sum \rightarrow S$$

S=0; Repeat N times

S = S + X;

We need something like this: ٠

But not quite.

Need to use the clock signal to hold up the feedback to match up with the input signal.

EECS150 lec04-SDS-review2

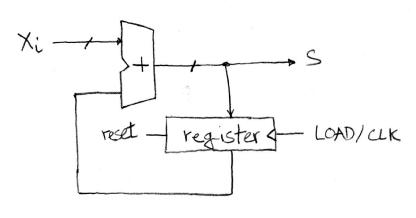

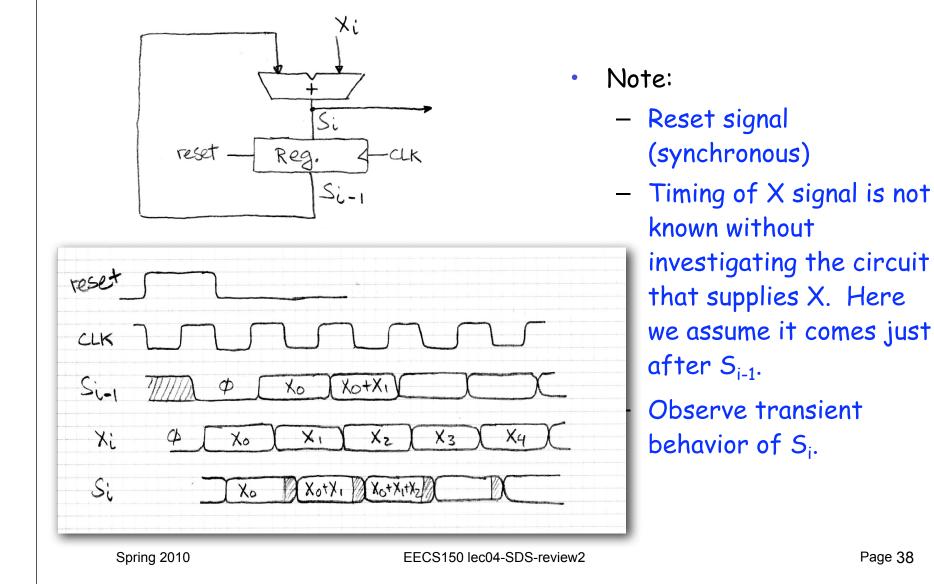

## **Accumulator Circuit**

- Put register, with clock signal controlling its load, in feedback path.

- On each clock cycle the register prevents the new value from reaching the input to the adder prematurely.

(The new value just waits at the input of the register).

## **Register Details (again)**

• A n-bit wide register is nothing but a set of flip-flops (1-bit wide registers) with a common load/clk signal.

• A flip-flop captures its input on the edge of the clock (rising edge in this case - positive edge flip-flop). The new input appears at the output after a short delay.

## **Accumulator Revisited**

we assume it comes just

that supplies X. Here

investigating the circuit

after  $S_{i-1}$ .

(synchronous)

known without

Observe transient behavior of  $S_i$ .

Thursday, January 28, 2010

Page 38

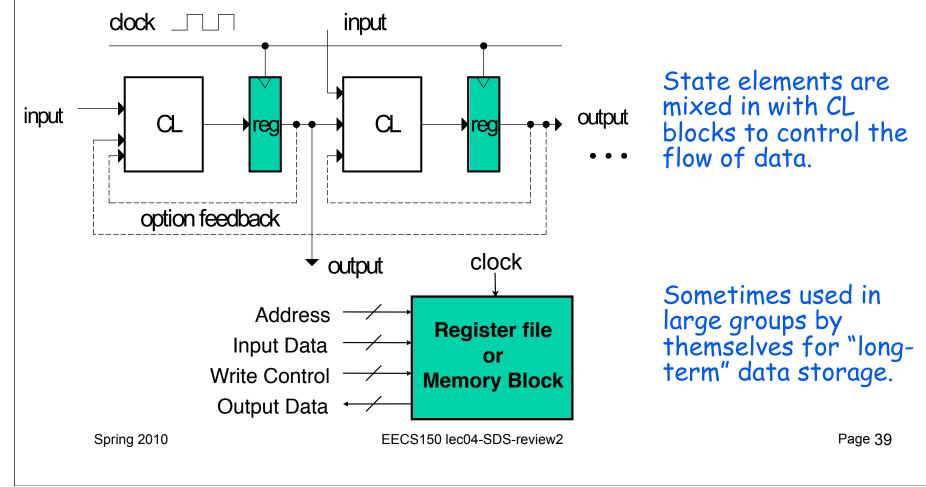

# Only Two Types of Circuits Exist Combinational Logic Blocks (CL) State Elements (registers)

## **Uses for State Elements**

- 1) As a place to store values for some indeterminate amount of time:

- Register files (like \$1-\$31 on the MIPS)

- Memory (caches, and main memory)

- 2) Help control the flow of information between combinational logic blocks.

- State elements are used to hold up the movement of information at the inputs to combinational logic blocks and allow for orderly passage.

Spring 2010

EECS150 lec04-SDS-review2

Page 42

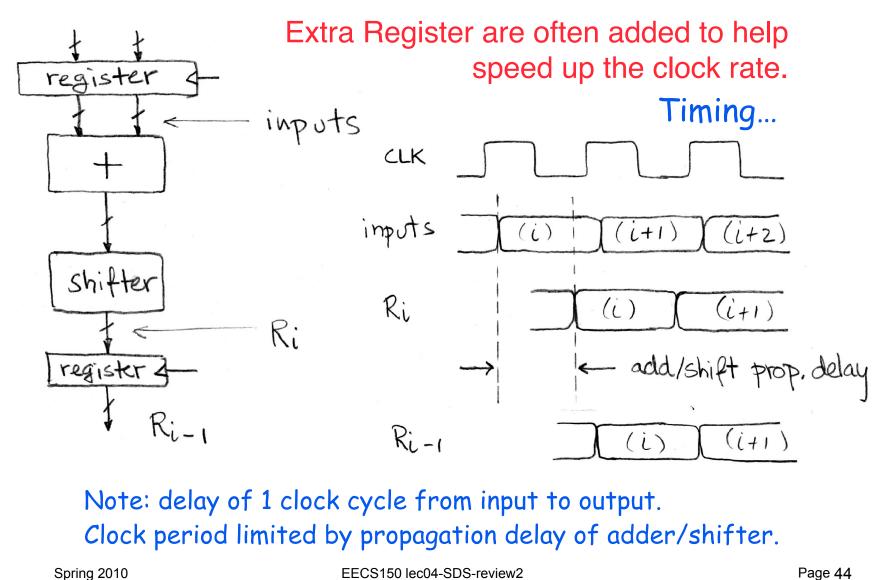

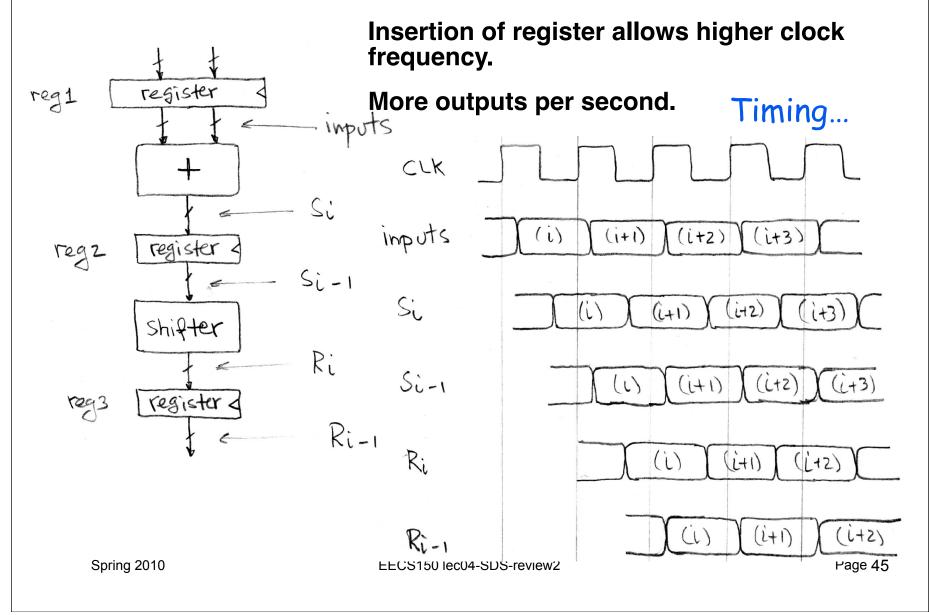

# **Pipelining and Registers**

UC Regents Spr 2010 © UCB

## Pipelining to improve performance (1/2)

## Pipelining to improve performance (2/2)

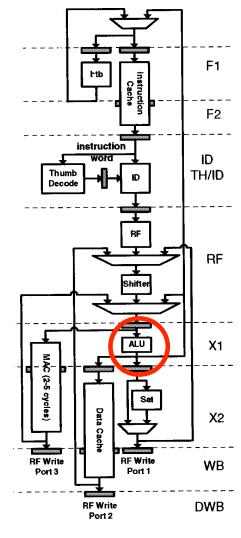

#### **Pipelining in a real CPU design ...**

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

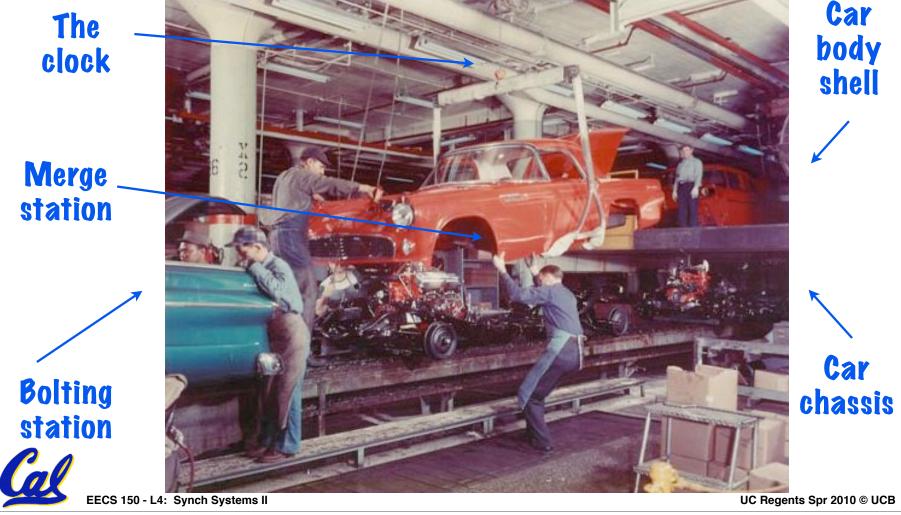

#### Assembly line moves on a steady clock. Each station does the same task on each car.

#### Simpler station tasks $\rightarrow$ more cars per hour. Simple tasks take less time, clock is faster.

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

#### Line speed limited by slowest task. Most efficient if all tasks take same time to do

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

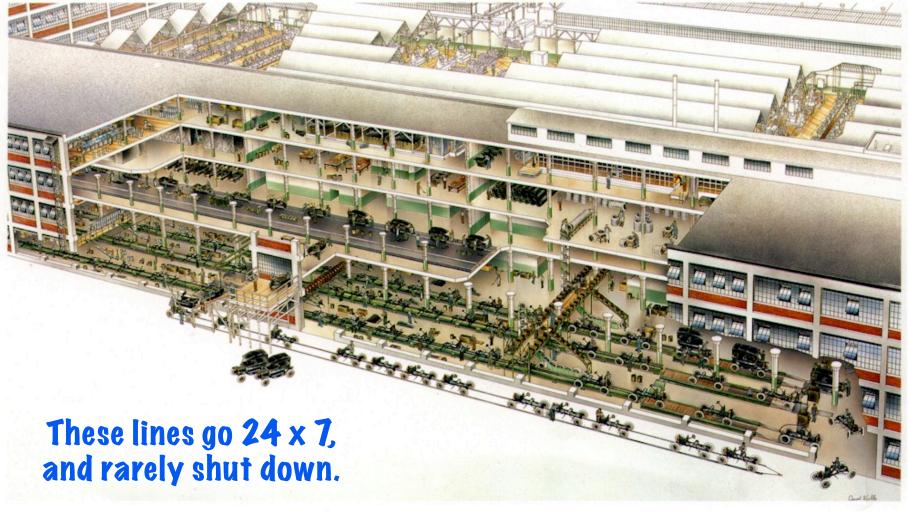

#### Simpler tasks, complex car $\rightarrow$ long line!

EECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

#### Lessons from car assembly lines

- **Faster** line movement yields more cars per hour off the line.

- **Faster line movement requires more** stages, each doing simpler tasks.

To maximize efficiency, all stages should take same amount of time (if not, workers in fast stages are idle)

"Filling", "flushing", and "stalling" assembly line are all bad news.

ECS 150 - L4: Synch Systems II

UC Regents Spr 2010 © UCB

## **Flip-Flop Details**

UC Regents Spr 2010 © UCB

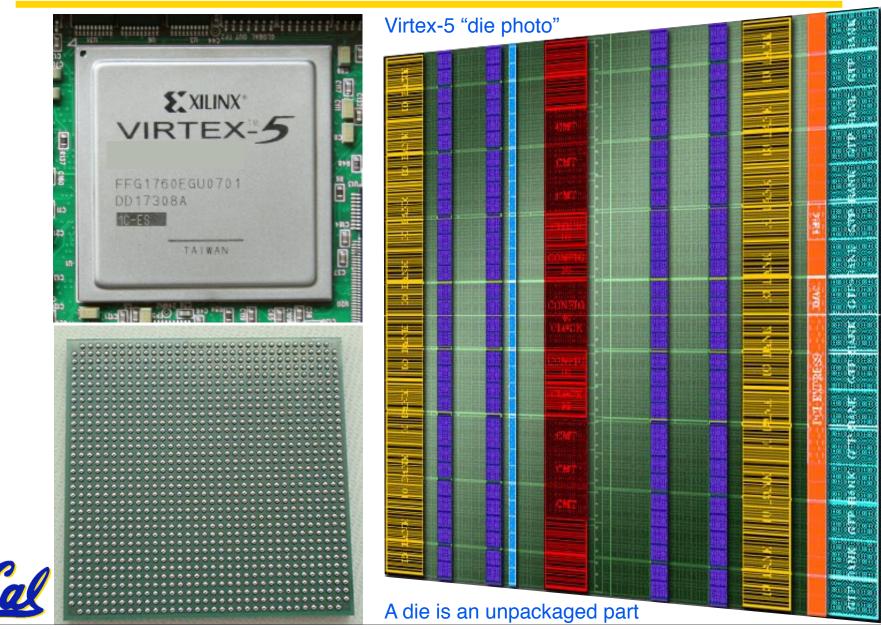

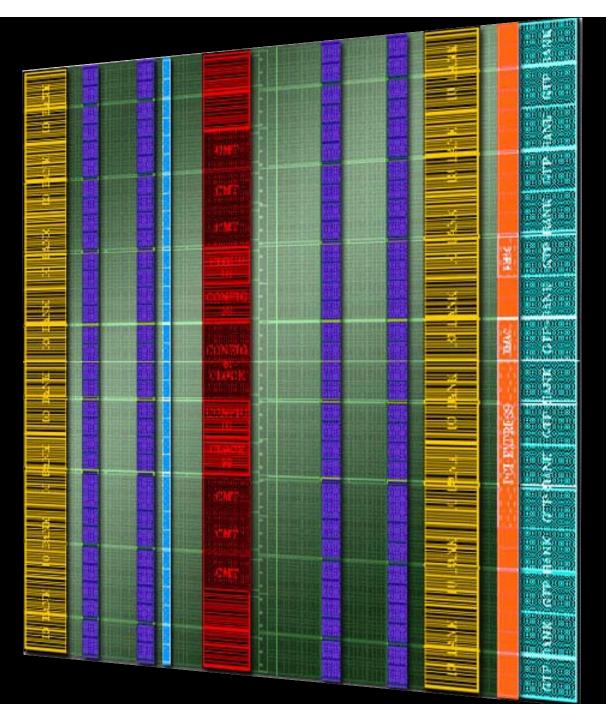

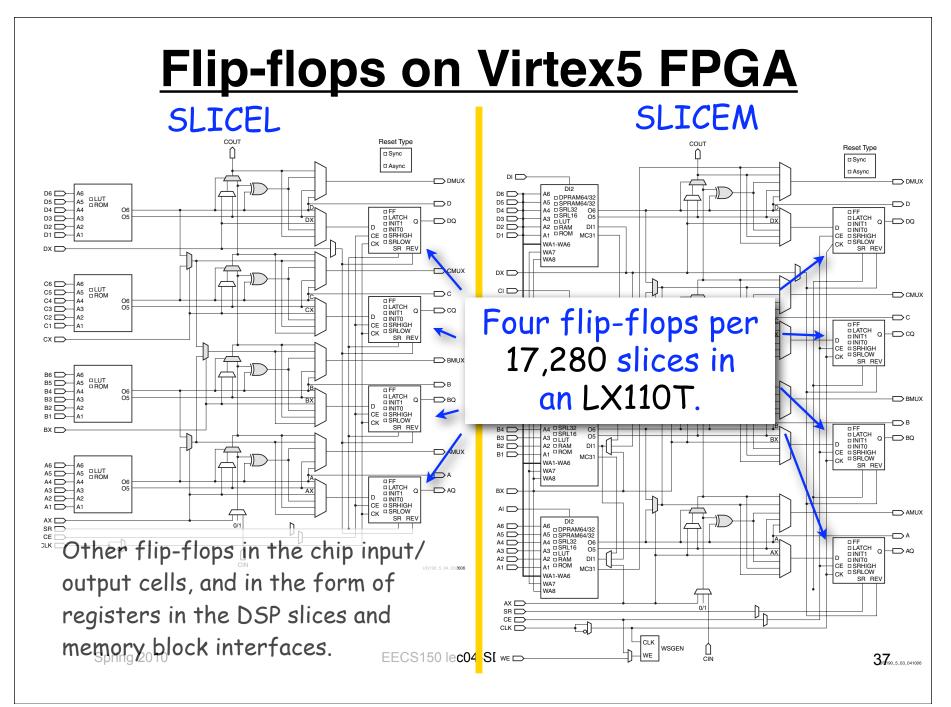

#### FPGA: Xilinx Virtex-5 XC5VLX110T

Colors represent different types of resources: Logic Block RAM DSP (ALUs) Clocking I/O Serial I/O + PCI

A routing fabric runs throughout the chip to wire everything together.

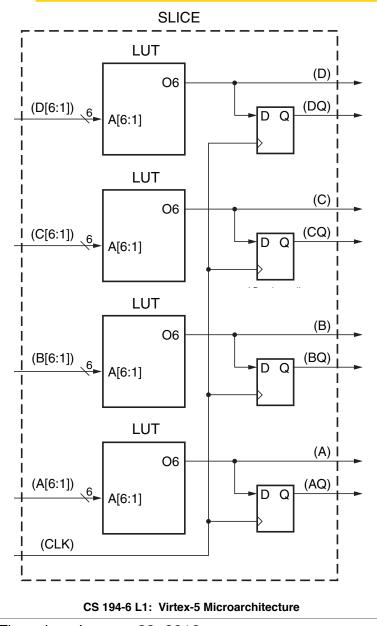

#### The simplest view of a slice

Four 6-LUTs

**Four Flip-Flops**

Switching fabric may see combinational and registered outputs.

UC Regents Fall 2008 © UCB

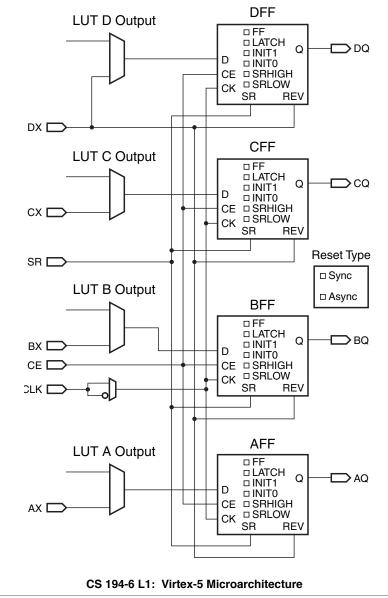

## **Slice flip-flop properties ...**

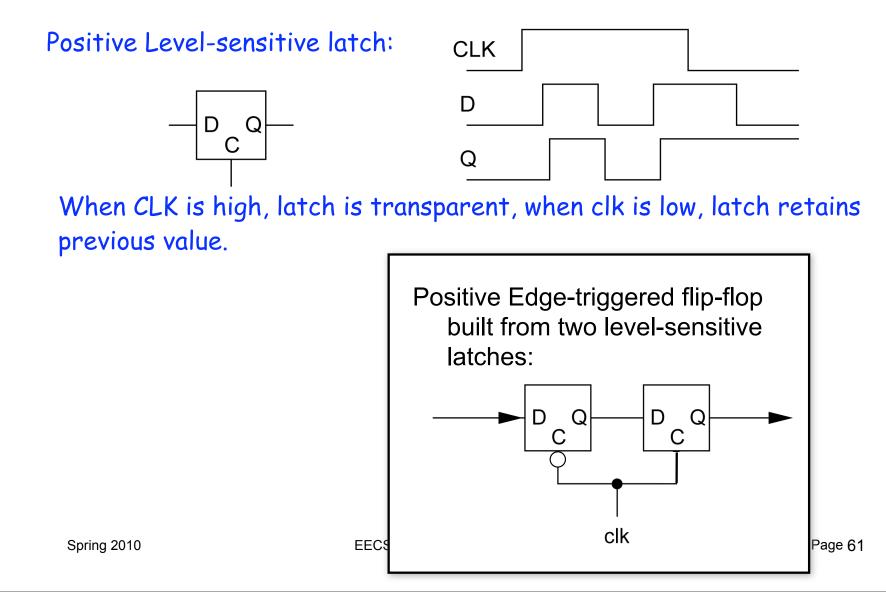

Each state element may be edge-triggered or latching.

Clock enable, clock polarity, and set/reset lines in a slice are shared.

> Each state element may respond differently to set/ reset signal.

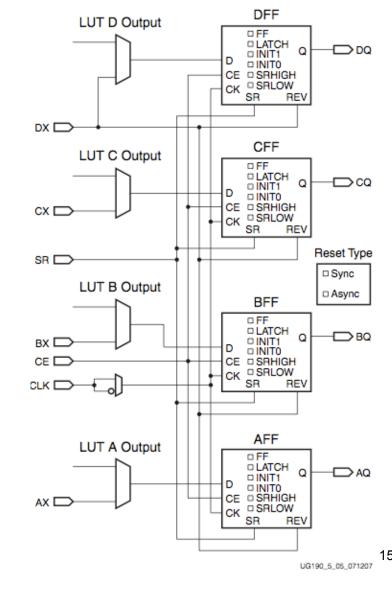

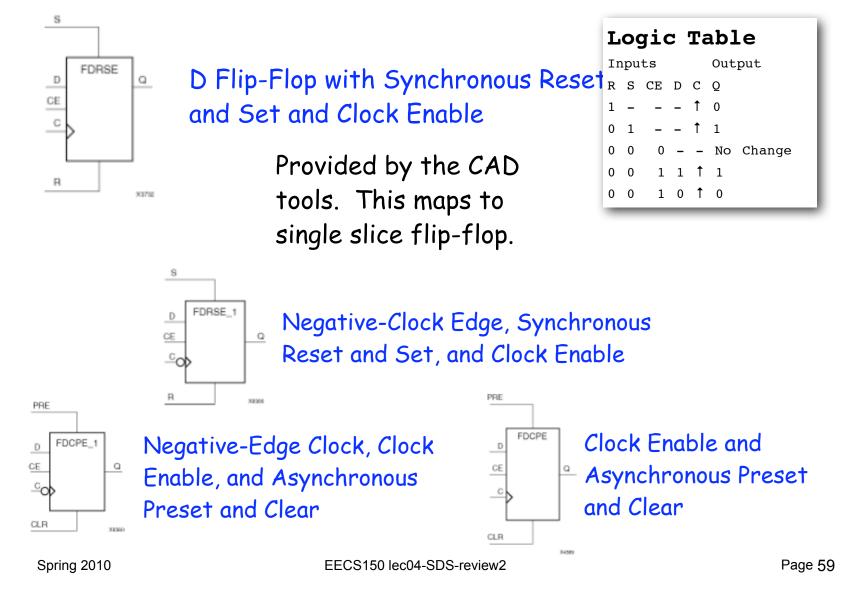

## **Virtex5 Slice Flip-flops**

4 flip-flops / slice (corresponding to the 4 6-LUTs)

Each takes input from LUT output or primary slice input.

Edge-triggered FF vs. level-sensitive latch. Clock-enable input (can be set to 1 to disable) (shared).

Positive versus negative clock-edge. Synchronous vs. asynchronous reset. SRHIGH/SRLOW select reset (SR) set. REV forces opposite state. INITO/INIT1 used for global reset (not shown - usually just after power-on and configuration).

150 lec04-SDS-review2

Page 58

## Virtex5 Flip-flops "Primitives"

## **Inside a Flip-Flop**

UC Regents Spr 2010 © UCB

# Upcoming events:

| Tue 1/26 | Lec #3: FPGA Architecture Introduction: [PDF]<br>Reading: Chapter 5 of the <u>Virtex-5 User's Guide</u> (PreLab reading) | HW #1: [ <u>PDF]</u><br>(Due Fri, Jan 29 @ 14:10) | Lab #1: FPGA Physical Layou<br>[ZIP] [PDF] |

|----------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|

|          | Lec #4: Synchronous Digital Systems Review (2):                                                                          | Solution:                                         | Lab Lec #2:                                |

|          | Lec #5: Verilog Primer:<br>Reading: DDCA: Chapter 4                                                                      | HW #2:<br>(Due Fri, Feb 5 @ 14:10)                | Lab #2: Structure Verilog FPG              |

| Thr 2/4  | Lec #6: CAD Tools (Synthesis):                                                                                           | Solution: Quiz:                                   | Lab Lec #3:                                |

# Have a good weekend!

UC Regents Spr 2010 © UCB