## EECS150 - Digital Design

## <u>Lecture 7 - Computer Aided Design</u> (CAD) - Part II (Logic Simulation)

Feb 9, 2010 John Wawrzynek

Spring 2010

EECS150 - Lec7-CAD2

Page 1

## **Finite State Machine Review**

State Transition Diagram Implementation Circuit Diagram in=0 rst in IDLE clk state register in=0 out=0 in=0 combinational in=1 in=1 logic **S**0 **S**1 out=0 out=1 out 🌡 in=1 Holds a symbol to CL functions to determine output keep track of which value and next state based on input bubble the FSM is in. and current state. What does this one do? out = f(in, current state) Every Synchronous Digital System is a FSM. next state = f(in, current state)

#### **Procedural Assignments**

The sequential semantics of the blocking assignment allows variables to be multiply assigned within a single always block. Unexpected behavior can result from mixing these assignments in a single block. Standard rules:

- Use blocking assignments to model combinational logic within an always block ( "=").

- Use non-blocking assignments to implement sequential logic ("<=").</li>

- iii. Do not mix blocking and non-blocking assignments in the same always block.

- iv. Do not make assignments to the same variable from more than one always block.

Spring 2010

EECS150 - Lec7-CAD2

Page 3

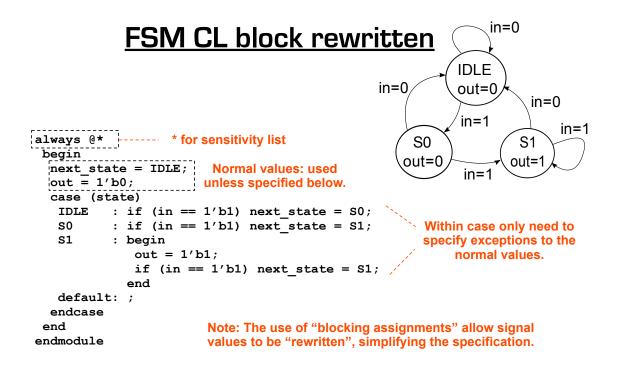

#### **Finite State Machines** in=0 module FSM1(clk, rst, in, out); IDLE input clk, rst; Must use reset to force input in; in=0 out=0 to initial state. in=0 output out; reset not always shown in STD in=1 in=1 // Defined state encoding: S0 S1 parameter IDLE = 2'b00; out=0 out=1 **Constants local** in=1 parameter S0 = 2'b01;parameter S1 = 2'b10; to this module. reg out; ..... out not a register, but assigned in always block reg [1:0] state, next\_state; **Combinational logic** signals for transition. THE register to hold the "state" of the FSM. // always block for state register always @(posedge clk) if (rst) state <= IDLE;</pre> else state <= next state;</pre> A separate always block should be used for combination logic part of FSM. Next state and output generation. (Always blocks in a design work in parallel.) Spring 2010 EECS150 - Lec7-CAD2 Page 4

```

Page 5

```

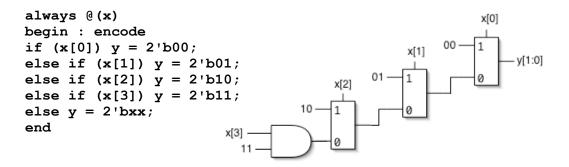

#### **Encoder Example**

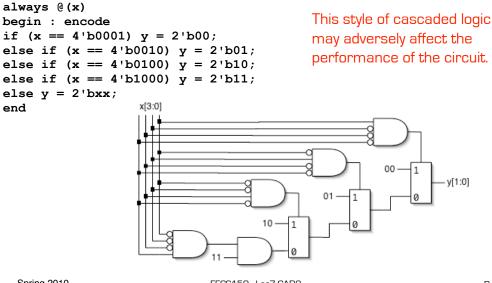

Nested IF-ELSE might lead to "priority logic" Example: 4-to-2 encoder

#### Encoder Example (cont.)

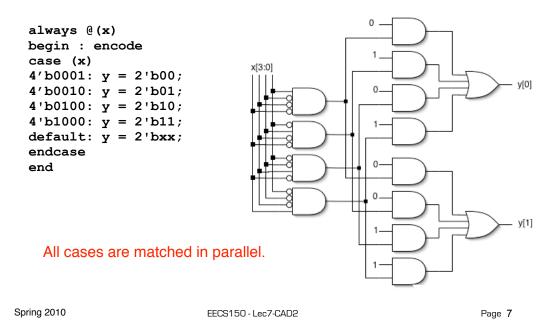

#### To avoid "priority logic" use the case construct:

### Encoder Example (cont.)

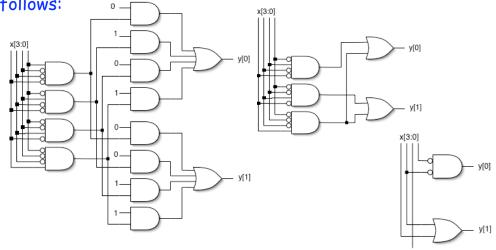

This circuit would be simplified during synthesis to take advantage of constant values and other Boolean equalities as follows:

A similar simplification would be applied to the if-else version also.

### Encoder Example (cont.)

If you can guarantee that only one 1 appears in the input, then simpler logic can be generated:

If the input applied has more than one 1, then this version functions as a "priority encoder". The least significant 1 gets priority (the more significant 1's are ignored). Again the circuit will be simplified when possible.

Spring 2010

EECS150 - Lec7-CAD2

Page 9

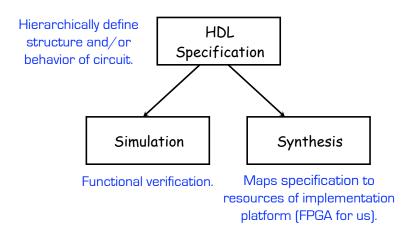

# Verilog in EECS150

- Primarily use **behavior modeling**. With **instantiation** to build hierarchy and map to FPGA resources not supported by synthesis.

- Primary Style Guidelines:

- Favor continuous assign and avoid always blocks unless:

- no other alternative: ex: state elements, case

- they help readability and clarity of code: ex: large nested if-else-if

- Use named ports.

- Separate CL logic specification from state elements.

- Follow our rules for procedural assignments.

- Verilog is a big language. This is only an introduction.

- Our text book is a good source. Read and use chapter 4.

- When needed look at online IEEE Std 1364-2001 document.

- Be careful of what you read on the web! Many bad examples out there.

- We will be introducing more useful constructs throughout the semester. Stay tuned!

Spring 2010 EECS150 Lec7-CAD2

### Final thoughts on Verilog Examples

Verilog may look like C, but it describes hardware! (Except in simulation test-benches - which actually behave like programs.)

Multiple physical elements with parallel activities and temporal relationships.

A large part of digital design is knowing how to write Verilog that gets you the desired circuit. <u>First understand the circuit</u> <u>you want, then figure out how to code it in Verilog</u>. If you do one of these activities without the other, you will struggle. These two activities will merge at some point for you.

Be suspicious of the synthesis tools! Check the output of the tools to make sure you get what you want.

Spring 2010

EECS150 - Lec7-CAD2

Page 11

# EECS150 Design Methodology

Let's look at the other branch.

### **Design Verification**

- Industrial design teams spend a large percentage of the design time on design verification:

- Removing functional bugs, messaging the design to meet performance, cost, and power constraints.

- Particularly important for IC design, less so for FPGAs.

- A variety of tools and strategies are employed.

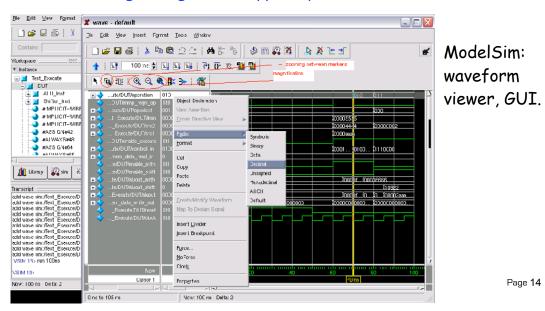

- Simulation: software that interprets the design description and mimics signal behavior and timing (and power consumption).

- Simulation provides better controllability and observability over real hardware. Saves on wasted development time and money.

- Emulation: hardware platform (usually FPGAs) are used to mimic behavior of another system. Fast simulation.

- Static Analysis: tools examines circuit structure and reports on expected performance, power, or compares alternative design representations looking for differences.

Spring 2010 EECS150 - Lec7-CAD2

Page 13

## **Simulation**

Verilog/VHDL simulators use 4 signals values:

#### 0, 1, X (unknown), Z (undriven)

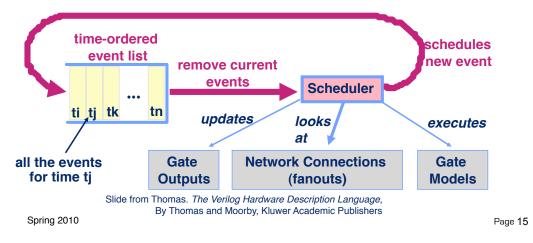

#### Simulation engine algorithm typically "discrete event simulation"

## **Discrete Event Simulation Engine**

- A time-ordered list of events is maintained

Event: a value-change scheduled to occur at a given time

All events for a given time are kept together

- The scheduler removes events for a given time ...

- ... propagates values, executes models, and creates new events ...

# **Simulation Testing Strategies**

- Unit Testing: Large systems are often too complex to test all at once, so an bottom-up hierarchical approach. Sub-modules are tested in isolation.

- **Combinational Logic blocks**: when practical, exhaustive testing. Otherwise a combination of random and directed tests.

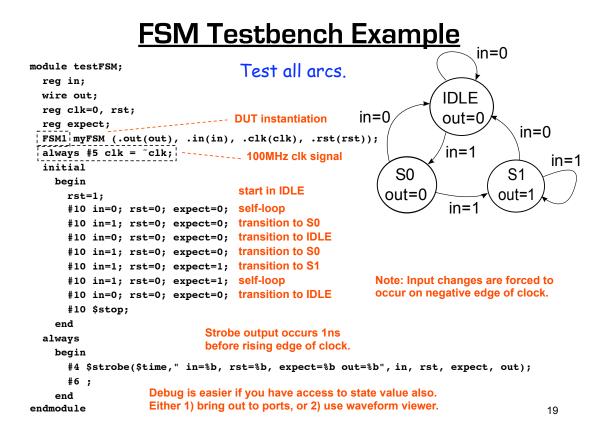

- Finite state machines: test every possible transition and output.

- **Processors**: use software to expose bugs.

- In all cases, the simulated output values are checked against the expected values. Expected values are derived through a variety of means:

- behavior model running along side the design under test

- precomputed inputs and outputs (vectors)

- co-simulation. Ex: C-language model runs along side ModelSim

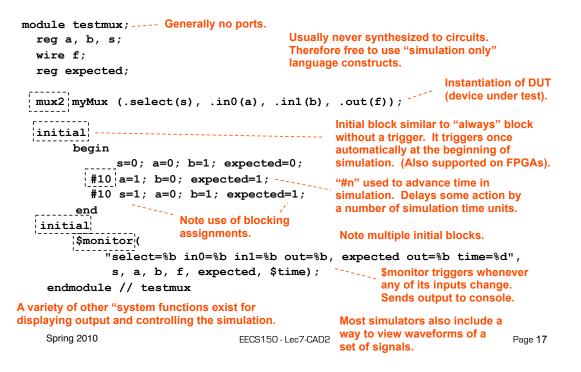

#### **Testbench**

Top-level modules written specifically to test other modules.

#### Mux4 Testbench

| module testmux4                                                                                | ; Dec                        | aration and initialization all at once.                                     |         |

|------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------|---------|

| reg [5:0] count = 6'b000000; Generally not available in synthesis.                             |                              |                                                                             |         |

| reg a, b, c, d, expected;                                                                      |                              |                                                                             |         |

| reg [1:0] S;                                                                                   |                              |                                                                             |         |

| wire f;                                                                                        |                              |                                                                             |         |

| <pre>imux4 myMux (.select(S), .in0(a), .in1(b), .in2(c), .in3(d), .out(f)); initial</pre>      |                              |                                                                             |         |

| begin Enumerate all possible input patterns.                                                   |                              |                                                                             |         |

| repeat(64)                                                                                     |                              |                                                                             |         |

| begin                                                                                          |                              | Apply pattern to DUT                                                        |         |

| begin Apply pattern to DUT<br>{S, d, c, b, a} = count[5:0];                                    |                              |                                                                             |         |

| case (S)Behavioral model of mux4                                                               |                              |                                                                             |         |

| 2 boo: expected = a;                                                                           |                              |                                                                             |         |

|                                                                                                | 01: expected = b;            | \$strobe displays data at a selected time. 1                                | hat     |

| 2 'b10: expected = c; time is just before simulation time is                                   |                              |                                                                             |         |

| 2'bl1: expected = d; / advanced (after all other events).                                      |                              |                                                                             |         |

| endcase // case(S)                                                                             |                              |                                                                             |         |

| #8 \$strobe( "select=%b in0=%b in1=%b in2=%b in3=%b out=%b,                                    |                              |                                                                             |         |

| <pre>expected=%b time=%d", S, a, b, c, d, f, expected, \$time); #2 count = count + 1'b1;</pre> |                              |                                                                             |         |

| #2 CO<br>end<br>\$stop;                                                                        | Wait a bit, then bump count. | Delay to allow mux outputs to stabilize.<br>Here we assume mux delay < 8ns. | I.      |

| end<br>endmodule                                                                               |                              | Alternative to \$strobe in this case,                                       |         |

| enallouure                                                                                     |                              | #8 if (f != expected) \$display("Misma                                      | tch:);  |

| Spring 2010                                                                                    | EECS150                      | - Lec7-CAD2                                                                 | Page 18 |

## Final Words (for now) on Simulation

Testing is not always fun, but you should view it as part of the design process. Untested potentially buggy designs are a dime-a-dozen. Verified designs have real value.

Devising a test strategy is an integral part of the the design process. It shows that you have your head around the design. It should not be an afterthought.