# CS 152 Computer Architecture and Engineering CS 252 Graduate Computer Architecture

# Midterm #1 SOLUTIONS

# March 1, 2021 Professor Krste Asanović

| <b>Name:</b> |  |

|--------------|--|

| SID:         |  |

# 80 Minutes, 5 Questions

#### Notes:

- Not all questions are of equal difficulty, so look over the entire exam!

- Please carefully state any assumptions you make.

- Please write your name on every page in the exam.

- Do not discuss the exam with other students who haven't taken the exam.

- If you have inadvertently been exposed to an exam prior to taking it, you must tell the instructor or TA.

- You will receive no credit for selecting multiple-choice answers without giving explanations if the instructions ask you to explain your choice.

| Question | CS152 Point Value | CS252 Point Value |

|----------|-------------------|-------------------|

| 1        | 12                | 12                |

| 2        | 21                | 12                |

| 3        | 26                | 26                |

| 4        | 14                | 14                |

| 5        | 12                | 12                |

| TOTAL    | 85                | 76                |

# Problem 1: (12 Points) Iron Law of Processor Performance

Mark whether the following modifications will cause each term in the Iron Law to **increase** or **decrease**, or whether the modification will have a **negligible** effect. Assume all other parameters of the system are unchanged whenever possible. Explain your reasoning. Be explicit if you are relying on any specific assumptions.

|                                                                                   | Instructions / Program                                                                                                                                                                                                                                       | Cycles / Instruction                                                                                                                                                                                                                                                      | Time / Cycle                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adding a second data bus to a single-bus microcoded machine                       | Negligible  The second data bus is a microarchitectural feature not visible at the ISA level.                                                                                                                                                                | Decrease  The second data bus avoids some structural hazards compared to a single shared bus, reducing the number of microinstructions by enabling more parallel operations.                                                                                              | Increase  The second data bus increases fanout and wire congestion. Additional muxes are needed to select between busses for each consumer. Driving the second bus requires more control signals, increasing the microcode ROM width. |

| Adding instructions with register-operand indexing: R[rd] = R[R[rs1]] + R[R[rs2]] | Decrease – Code that performs dynamic array indexing may sometimes be replaced with fewer instructions.  OR  Negligible – A compiler is unlikely to use this addressing mode, since arrays are usually allocated in memory, not in the scalar register file. | Each operand involves two register file reads, which may require occupying the decode stage for two cycles or introducing an additional pipeline stage. Structural hazards can arise from the limited number of register file read ports. More data hazards are possible. | Increase  More read ports may have to be added to the register file. The control logic becomes more complex to sequence the second round of register file reads.                                                                      |

|                                                               | Instructions / Program                                                                                                                | Cycles / Instruction                                                                                                                                                                                                                                                                                                                                                                                                                       | Time / Cycle                                                                                                                                                                                                                      |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Using a software page table walker, instead of a hardware PTW | Increase  For each TLB miss, additional instructions are executed by an exception handler to walk the page tables and refill the TLB. | Decrease  A TLB miss does not incur a long-latency stall for a hardware page table walk. Bubbles are replaced with additional instructions.                                                                                                                                                                                                                                                                                                | Decrease – The hardware complexity is reduced.  OR  Negligible – A hardware PTW is a relatively simple state machine and is unlikely to be a critical path in typical implementations.                                            |

| Removing support for precise exceptions                       | Increase  Resuming from an imprecise exception may require more instructions to repair/restore microarchitectural state.              | Negligible – Precise exceptions have minimal impact on the latencies of operations: Exception information is propagated in parallel to the pipeline, and bypassing allows results to be used before architectural state is updated at the commit point.  OR  Decrease – Exception handling latency is marginally reduced, as control can be redirected to the handler as soon as an exception is detected, rather than waiting for commit. | Decrease – The hardware complexity is reduced.  OR  Negligible – The simplification of commit logic is balanced by the introduction of hardware mechanisms to save microarchitectural state to memory for restartable exceptions. |

|                                                        | Instructions / Program                                                                                                                                                                                                                                                                          | Cycles / Instruction                                                                                                                    | Time / Cycle                                                                                                                                                                                              |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changing the base page size from 4 KiB to 8 KiB        | Decrease  There are fewer page faults to handle and fewer pages for the OS to manage. (It is possible that larger pages exacerbate waste from internal fragmentation, increase memory pressure, and trigger more frequent swapping, but the difference is modest enough that this is unlikely). | Decrease  Doubling the TLB reach reduces the number of TLB misses.                                                                      | Negligible  The page table walk is unchanged since the base page size affects only the leaf page table entries.                                                                                           |

| Removing byte load and store instructions from the ISA | Increase  Additional bitwise instructions are required to emulate byte accesses with wider load and store instructions.                                                                                                                                                                         | Decrease  The shift and mask operations to pack/unpack a byte within a word increases the proportion of simple arithmetic instructions. | Decrease  A smaller shifter is needed to align the load/store data in a cache line. (Simplified ECC circuitry in the cache subsystem was another justification cited by the architects of the Alpha ISA.) |

# **Problem 2: (21 Points) Microprogramming (CS152)**

Consider the REVLL complex instruction. This instruction reverses a linked list in memory, where the rs1 operand to this instruction is the memory address of the first node in the linked list. This instruction has no destination register, but the instruction zeroes the register specified by rs1 upon completion (it does not preserve rs1).

Alternate: This instruction reverses a linked list in memory, where the rs1 operand to this instruction is the memory address of a pointer to the first node in the linked list (a pointer to a pointer).

```

REVLL rs1

```

Every node in the linked list has the following structure. Assume that pointers are 32 bits wide in this architecture. The *next* pointer is either the memory address of the next node in the list or is equal to 0 (NULL) to indicate the end of the linked list.

```

struct node

{

void *value;

struct node *next;

}

struct node *next;

void *value;

}

```

For reference, the equivalent C and assembly code for this instruction are provided below.

```

void REVLL(struct node *head) {

# head is passed in a0

struct node *prev = NULL;

# t0 holds prev

struct node *curr = head;

# t1 holds next

while (curr != NULL) {

beqz a0, done

struct node *next = curr->next;

addi t0, t0, 0

curr->next = prev;

loop:

lw t1, 4(a0)

prev = curr;

sw t0, 4(a0)

curr = next;

addi t0, a0, 0

}

}

addi a0, t1, 0

bnez t1, loop

done:

```

```

void REVLL(struct node **head) {

# head is passed in a0

# t0 holds prev

struct node *prev = NULL;

struct node *curr = *head;

# t1 holds next

while (curr != NULL) {

lw a0, 0(a0)

struct node *next = curr->next;

begz a0, done

addi t0, t0, 0

curr->next = prev;

prev = curr;

loop:

curr = next;

lw t1, 0(a0)

sw t0, 0(a0)

}

}

addi t0, a0, 0

addi a0, t1, 0

bnez t1, loop

done:

```

# 2.A (2 points) Unpipelined CPI

Consider the execution of the assembly linked-list reversal code on an unpipelined RISC-V core with a CPI of 1 for every instruction, except for loads and stores, which take 2 cycles each. How many cycles does this program take to reverse a linked list with length 4 on this core?

Prologue: 0 loads/stores, 2 other instructions Loop: 1 load, 1 store, 3 other instructions 2 + (2 + 2 + 3) \* 4 = 30 cycles

Prologue: 1 load, 2 other instructions Loop: 1 load, 1 store, 3 other instructions 2+2+(2+2+3)\*4=32 cycles

#### 2.B (16 points) Microprogramming

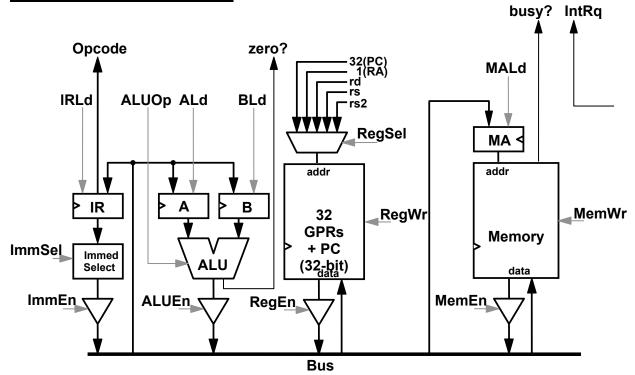

In the attached microcode table, write microcode to implement the REVLL instruction for a bus-based RISC-V machine. This microarchitecture is identical to the one described in Handout #1 and Problem Set 1.

The final solution should be efficient with respect to the number of microinstructions used. Make sure to use logical descriptions of data movement in the "pseudocode" column for clarity. Credit will be awarded for optimizing signals using "don't care" or \* values as appropriate, but this is less important than producing a correct implementation. Please comment your code clearly. If the pseudocode for a line does not fit in the space provided, or if you have additional comments, you may write neatly in the margins.

Reference material on the microcoded datapath is provided on the following page.

Three temporaries are needed to maintain the curr, prev, and next pointers during the linked list traversal, but as only two operand registers (A and B) are provided by the datapath, it is necessary for the microcode to clobber rs1. The solution uses R[rs1] to hold curr, B to hold prev (initialized to 0 before entering the microcode loop), and A to hold next.

The solution for the alternate version optimizes for fewer microinstructions in the loop body. There is also a simpler implementation that is nearly identical to the solution for first version, except for an extra microinstruction with a memory operation to deference R[rs1] prior to the loop.

#### 2.C (2 points) Microcoded performance

How many cycles does your implementation take to reverse a linked list with length 4? Assume that the memory access time is 4 cycles.

```

Fetch: 3

Prologue: 2

Loop: 1 + 4 + 4 + 2 (4 iterations)

Epilogue: 1

3 + 2 + 4*11 + 1 = 50 cycles

Fetch: 3

Prologue: 1 + 4 + 1 + 1

Loop: 4 + 4 + 2 (4 iterations)

Epilogue: 1

3 + 7 + 4*10 + 1 = 51 cycles

```

# 2.D (1 point) Implementation Comparison

Compare the performance of your implementation with that of the unpipelined RISC-V core from 2.A. Assume that both processors are using the same memory system, such that the unpipelined core has 4x the cycle time of the microcoded machine to accommodate the memory latency.

1 cycle of the unpipelined core is equivalent to 4 cycles of the microcoded machine.

Reversing a linked list with length 4 takes the unpipelined core 30\*4 = 120 equivalent cycles, which is 120/50 = 2.4 times longer than the microcoded REVLL instruction. (This demonstrates how a microcoded machine with CPI > 1 can achieve better performance compared to an unpipelined implementation clocked at a lower frequency.)

Reversing a linked list with length 4 takes the unpipelined core 32\*4 = 128 equivalent cycles, which is  $128/51 \approx 2.51$  times longer than the microcoded REVLL instruction.

| State   | Pseudocode         | IR<br>Ld | Reg<br>Sel | Reg<br>Wr | Reg<br>En | A<br>Ld | B<br>Ld | ALUOp   | ALU<br>En | MA<br>Ld | Mem<br>Wr | Mem<br>En | Imm<br>Sel | lmm<br>En | μBr | Next State |

|---------|--------------------|----------|------------|-----------|-----------|---------|---------|---------|-----------|----------|-----------|-----------|------------|-----------|-----|------------|

| FETCH0: | MA ← PC;<br>A ← PC | *        | PC         | 0         | 1         | 1       | *       | *       | 0         | 1        | 0         | 0         | *          | 0         | N   | *          |

|         | IR ← Mem           | 1        | *          | *         | 0         | 0       | *       | *       | 0         | 0        | 0         | 1         | *          | 0         | S   | *          |

|         | PC ← A+4           | 0        | PC         | 1         | 1         | 0       | *       | INC_A_4 | 1         | *        | 0         | 0         | *          | 0         | D   | *          |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

| REVLL0: | A, B ← R[rs1]      | 0        | rs1        | 0         | 1         | 1       | 1       | *       | 0         | *        | 0         | 0         | *          | 0         | N   | *          |

|         | if (A == 0)        | 0        | *          | 0         | 0         | 0       | 0       | COPY_A  | 0         | *        | 0         | 0         | *          | 0         | EZ  | FETCH0     |

|         | μBr to FETCH0      |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         | B ← A - B (== 0)   | 0        | *          | 0         | 0         | 0       | 1       | SUB     | 1         | *        | 0         | 0         | *          | 0         | N   | *          |

| REVLL1: | MA ← A + 4         | 0        | *          | 0         | 0         | *       | 0       | INC_A_4 | 1         | 1        | 0         | 0         | *          | 0         | N   | *          |

|         | A ← Mem            | 0        | *          | 0         | 0         | 1       | 0       | *       | 0         | 0        | 0         | 1         | *          | 0         | S   | *          |

|         | Mem ← B            | 0        | *          | 0         | 0         | 0       | 0       | COPY_B  | 1         | 0        | 1         | 0         | *          | 0         | S   | *          |

|         | B ← R[rs1]         | 0        | rs1        | 0         | 1         | 0       | 1       | *       | 0         | *        | 0         | 0         | *          | 0         | N   | *          |

|         | R[rs1] ← A;        | 0        | rs1        | 1         | 0         | 0       | 0       | COPY_A  | 1         | *        | 0         | 0         | *          | 0         | NZ  | REVLL1     |

|         | if (A != 0)        |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         | μBr to REVLL1      |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         | μBr to FETCH0      | *        | *          | 0         | 0         | *       | *       | *       | 0         | *        | 0         | 0         | *          | 0         | J   | FETCH0     |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

|         |                    |          |            |           |           |         |         |         |           |          |           |           |            |           |     |            |

| Pseudocode                | IR<br>Ld                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reg<br>Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reg<br>Wr                                             | Reg<br>En                                             | A<br>Ld                                               | B<br>Ld                                               | ALUOp                                                 | ALU<br>En                                             | MA<br>Ld                                              | Mem<br>Wr                                             | Mem<br>En                                             | Imm<br>Sel                                            | lmm<br>En                                             | μBr                                                   | Next State                                                           |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|

| A ← PC                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                     | 1                                                     | *                                                     | *                                                     | 0                                                     | 1                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | N                                                     | *                                                     |                                                                      |

| IR ← Mem                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | *                                                     | 0                                                     | 0                                                     | *                                                     | *                                                     | 0                                                     | 0                                                     | 0                                                     | 1                                                     | *                                                     | 0                                                     | S                                                     | *                                                                    |

| PC ← A+4                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                     | 1                                                     | 0                                                     | *                                                     | INC_A_4                                               | 1                                                     | *                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | D                                                     | *                                                                    |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| MA ← R[rs1]               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rs1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                     | 1                                                     | *                                                     | *                                                     | *                                                     | 0                                                     | 1                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | N                                                     | *                                                                    |

| A ← Mem                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | 0                                                     | 1                                                     | *                                                     | *                                                     | 0                                                     | 0                                                     | 0                                                     | 1                                                     | *                                                     | 0                                                     | S                                                     | *                                                                    |

| MA, B ← A;                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rs1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                     | 0                                                     | 0                                                     | 1                                                     | COPY_A                                                | 1                                                     | 1                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | EZ                                                    | FETCH0                                                               |

| $R[rs1] \leftarrow A;$    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| if (A == 0)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| μBr to FETCH0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| B ← A - B (== 0)          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | 0                                                     | *                                                     | 1                                                     | SUB                                                   | 1                                                     | 0                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | N                                                     | *                                                                    |

| A ← Mem                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | 0                                                     | 1                                                     | 0                                                     | *                                                     | 0                                                     | 0                                                     | 0                                                     | 1                                                     | *                                                     | 0                                                     | S                                                     | *                                                                    |

| Mem ← B                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | 0                                                     | 0                                                     | 0                                                     | COPY_B                                                | 1                                                     | 0                                                     | 1                                                     | 0                                                     | *                                                     | 0                                                     | S                                                     | *                                                                    |

| B ← R[rs1]                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rs1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                     | 1                                                     | 0                                                     | 1                                                     | *                                                     | 0                                                     | *                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | N                                                     | *                                                                    |

| R[rs1], MA $\leftarrow$ A | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rs1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                     | 0                                                     | 1                                                     | 0                                                     | COPY_A                                                | 1                                                     | 1                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | NZ                                                    | REVLL1                                                               |

| if (A != 0)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| μBr to REVLL1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

| μBr to FETCH0             | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | 0                                                     | *                                                     | *                                                     | *                                                     | 0                                                     | *                                                     | 0                                                     | 0                                                     | *                                                     | 0                                                     | J                                                     | FETCH0                                                               |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                                      |

|                           | $\begin{array}{l} \text{MA} \leftarrow \text{PC}; \\ \text{A} \leftarrow \text{PC} \\ \text{IR} \leftarrow \text{Mem} \\ \text{PC} \leftarrow \text{A+4} \\ \\ \text{MA} \leftarrow \text{R[rs1]} \\ \text{A} \leftarrow \text{Mem} \\ \\ \text{MA, B} \leftarrow \text{A}; \\ \text{R[rs1]} \leftarrow \text{A}; \\ \text{if (A == 0)} \\ \text{µBr to FETCH0} \\ \text{B} \leftarrow \text{A} - \text{B (== 0)} \\ \text{A} \leftarrow \text{Mem} \\ \\ \text{Mem} \leftarrow \text{B} \\ \text{B} \leftarrow \text{R[rs1]} \\ \text{R[rs1], MA} \leftarrow \text{A} \\ \text{if (A != 0)} \\ \text{µBr to REVLL1} \\ \end{array}$ | $\begin{array}{c} Ld \\ MA \leftarrow PC; \\ A \leftarrow PC \\ IR \leftarrow Mem \\ 1 \\ PC \leftarrow A+4 \\ 0 \\ \hline \\ MA \leftarrow R[rs1] \\ 0 \\ A \leftarrow Mem \\ 0 \\ MA, B \leftarrow A; \\ R[rs1] \leftarrow A; \\ if (A == 0) \\ \mu Br \ to \ FETCH0 \\ \hline \\ B \leftarrow A - B \ (== 0) \\ 0 \\ A \leftarrow Mem \\ 0 \\ \hline \\ Mem \leftarrow B \\ 0 \\ \hline \\ R[rs1], MA \leftarrow A \\ if (A != 0) \\ \mu Br \ to \ REVLL1 \\ \hline \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Ld   Sei   Wr   En   Ld   Ld   Wr   En   Ld   Wr   En   Sei   En   N |

#### **Microcoding Reference Material**

# **Arithmetic Logic Unit:**

| ALUOp   | ALU Result Output     |

|---------|-----------------------|

| COPY_A  | A                     |

| COPY_B  | В                     |

| INC_A_1 | A+1                   |

| DEC_A_1 | A-1                   |

| INC_A_4 | A+4                   |

| DEC_A_4 | A-4                   |

| ADD     | A+B                   |

| SUB     | A-B                   |

| SLT     | Signed(A) < Signed(B) |

| SLTU    | A < B                 |

#### **Immediate Selector:**

Five immediate types are supported by ImmSel: ImmI, ImmU, ImmS, ImmJ, and ImmB.

#### **Microbranches:**

The  $\mu Br$  column represents a 3-bit field with six possible values: N, J, EZ, NZ, D, and S.

- N (next): The next state is simply (*current state* + 1).

- J (jump): The next state is *unconditionally* the state specified in the Next State column (i.e., it's an unconditional microbranch).

- EZ (branch-if-equal-zero): The next state depends on the value of the ALU's *zero* output signal (i.e., a conditional microbranch). If *zero* is asserted (*zero* = 1), then the next state is that specified in the Next State column, otherwise, it is (*current state* + 1).

- NZ (branch-if-not-zero): This behaves exactly like EZ but instead performs a microbranch if *zero* is not asserted (*zero* ≠ 0).

- D (dispatch): The FSM looks at the opcode and function fields in the IR and goes to the corresponding state.

- S (spin): The μPC stalls if busy? is asserted; otherwise, it goes to (current state +1)

# Problem 2: (14 points) Skewed-Associative Caches (CS252)

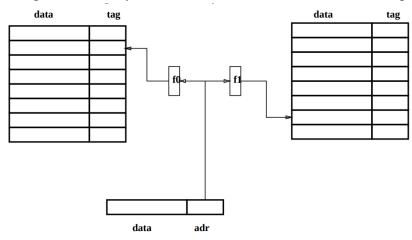

A skewed-associative cache uses a hash function on the index bits of the address to determine the cache set that it belongs to. Each way of a skewed associative cache uses a unique hash function.

A line of data is mapped at distinct addresses in the distinct banks of the cache

#### **2.A (3 points)**

Describe a code sequence that demonstrates higher performance on a skewed-associative cache than on an equivalent set-associative cache.

A sequence of constant-stride accesses that have the same index bits conflicts in a regular set-associative cache, whereas the hash function of a skewed-associative cache uniformly distributes the lines among all sets.

# **2.B.** (3 points)

Describe a code sequence that demonstrates reduced performance on a skewed-associative cache than on an equivalent set-associative cache.

An access pattern which causes only compulsory misses in a set-associative cache or consists of all different indices (such as lines in close spatial proximity) may conflict in a skewed-associative cache due to hash collisions.

#### **2.C** (4 points)

Explain why a skewed-associative cache is typically implemented with unique hashing functions for each way of the cache. In other words, what is the advantage of using a unique hashing function for each way of the cache, compared to a single hashing function for all ways?

This is the concept of inter-way dispersion, or "inter-bank dispersion" as discussed in the original Seznec paper. Two cache lines which conflict in one way of the cache would not conflict in the other ways. This avoids cache thrashing behavior.

# **2.D (4 points)**

Explain how virtual memory aliasing can be prevented in a skewed-associative cache when part of the virtual page number is used for the index bits.

The usual anti-aliasing mechanisms for a VIPT cache also apply here:

- On a miss, probe all sets in which aliases can potentially be located. If n bits of the VPN overlap with the index, there are  $2^n$  indices through which an alias may exist. Hash each possibility and evict the corresponding line if present.

- Use a physically-indexed inclusive L2 cache to store the VPN bits that are part of the L1 index or the hash itself. On an L1 miss that hits in the L2, evict the line from the L1 that the L2 entry identifies.

- Rely on the OS to ensure that all virtual pages which map to the same physical page match in the VPN bits that overlap with the cache index (page coloring).

# **Problem 3: (26 Points) Pipelining**

Note: The solutions for the alternate version of this question are at the end.

*Note: The questions in 3.B, 3.C, and 3.D can be answered independently of each other.*

Consider the standard fully-bypassed 5-stage RISC pipeline.

- A simple static branch predictor which always predicts PC+4 (branch not taken) in the Fetch stage (not-taken branches do not induce bubbles)

- Unconditional direct jumps (JAL) redirect from the **Decode** stage

- Conditional branches and unconditional indirect jumps (JALR) redirect from the **Execute** stage

- Bypass paths bypass into the operand registers before the **Execute** stage (the bypass select muxes are in the **Decode** stage)

The subsections of this question will consider the execution of the following loop on this pipeline.

| 1 | loop: | beq a1, x0, end  |

|---|-------|------------------|

| 2 |       | lw t0, 0(a0)     |

| 3 |       | sw t0, 0(a1)     |

| 4 |       | addi a0, a0, 0x8 |

| 5 |       | lw a1, 4(a1)     |

| 6 |       | j loop           |

| 7 | end:  |                  |

# 3.A Basic Pipelining

#### 3.A.i (4 points) Pipeline diagram

Complete the pipeline diagram for the first iteration of this loop (all instructions in the table).

| beq  | F | D | X | M | W |   |   |   |   |   |   |   |   |  |  |  |

|------|---|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| lw   |   | F | D | X | M | W |   |   |   |   |   |   |   |  |  |  |

| sw   |   |   | F | D | D | X | M | W |   |   |   |   |   |  |  |  |

| addi |   |   |   | F | F | D | X | M | W |   |   |   |   |  |  |  |

| lw   |   |   |   |   |   | F | D | X | M | W |   |   |   |  |  |  |

| j    |   |   |   |   |   |   | F | D | X | M | W |   |   |  |  |  |

| beq  |   |   |   |   |   |   |   |   | F | D | X | M | W |  |  |  |

#### 3.A.ii: (2 points) CPI

Compute the CPI of the loop as the number of iterations approaches infinity.

Count number of cycles between two branches in different iterations 8 / 6

# 3.B: Improving Performance

#### 3.B.i: (3 points) Bypass paths

Is there a bypass path you can add to improve the CPI of this code? If so, describe the bypass, and the new CPI as the number of iterations approaches infinity? Otherwise, explain why not.

Bypass load data at the end of the M stage into the store data wire at the end of the X stage. This avoids the load-use-delay between the LW and the SW which writes that data into memory. New CPI is 7 / 6

#### 3.B.ii: (3 points) Load-delay slots

Instead of adding a bypass path, you decide to introduce a load-delay slot to this architecture. Describe how to modify the code to take maximum advantage of the load-delay slot, and calculate the new CPI.

Reorder the addi instruction after the load. This avoids the load-use-delay as well. New CPI is 7 / 6

#### 3.C CISC Instructions

Instead of adding any of the features in Q3.B, you instead decide to add support for a new instruction to improve the performance of this code sequence. The new instruction you add is MMOV: memory-memory move.

MMOV: memory-memory move

M[R[rs2]] = M[R[rs1]]

To support this new instruction, you redesign the pipeline to be IF,ID,EX,LD,ST/WB. Now stores are performed in parallel with writeback, while loads are still performed in the 4th stage.

#### 3.C.i (3 points) Structural Hazards

Does the pipeline modification introduce new structural hazards into the machine? If so, describe the hazard, provide a code example that demonstrates the hazard, and suggest a modification that resolves this hazard with minimal performance penalty. If not, explain why.

Structural hazard on access to memory, as a two instruction sequence

SW LW

will have both instructions trying to access the data memory through the ST, LD stages respectively.

Interlocking only when there is back-to-back SW/LW will resolve this. Alternatively, making the data memory dual ported will remove the structural hazard.

#### 3.C.ii (3 points) Data Hazards

After resolving the structural hazard, if any, does the pipeline modification still introduce new data hazards into the machine? If so, describe the hazard, provide a code example that demonstrates the hazard, and suggest a modification that resolves this hazard with minimal performance penalty. If not, explain why.

If interlock was suggested for resolving the structural hazard, then no data hazard is possible. If dual-porting was suggested, then there is potential for RAW through memory. Need to bypass store data in ST stage to load data output in LD stage when store address and load address match.

#### 3.C.iii (3 points) Control Hazards

After resolving the structural and data hazards, if any, does the pipeline modification still introduce new control hazards into the machine? If so, describe the hazard, provide a code example that demonstrates the hazard, and suggest a modification that resolves this hazard with minimal performance penalty. If not, explain why.

No control hazard, since handling of branch/jump instructions are not affected, and they are all done in the F/D/X stages.

#### 3.C.iv (3 points) Precise exceptions

Does the pipeline still support precise exceptions after this modification? If not, provide a code example demonstrating a case where precise exceptions are not possible, and suggest an interlock to preserve precise exceptions with minimal performance penalty. If yes, explain why.