# CS162 Operating Systems and Systems Programming Lecture 9

#### **Address Translation**

February 25, 2013

Anthony D. Joseph

http://inst.eecs.berkeley.edu/~cs162

# **Virtualizing Resources**

- Physical Reality: Processes/Threads share the same hardware

- Need to multiplex CPU (CPU Scheduling)

- Need to multiplex use of Memory (Today)

- Why worry about memory multiplexing?

- The complete working state of a process and/or kernel is defined by its data in memory (and registers)

- Consequently, cannot just let different processes use the same memory

- Probably don't want different processes to even have access to each other's memory (protection)

2/25/2013 Anthony D. Joseph CS162 ©UCB Spring 2013

## **Goals for Today**

- · Address Translation Schemes

- Segmentation

- Paging

- Multi-level translation

- Paged page tables

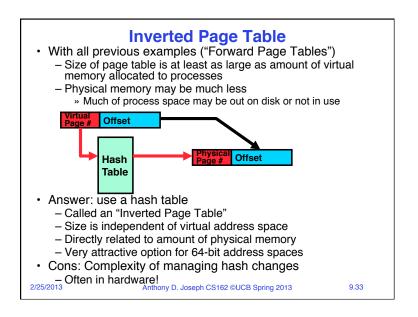

- Inverted page tables

Note: Some slides and/or pictures in the following are adapted from slides ©2005 Silberschatz, Galvin, and Gagne. Slides courtesy of Anthony D. Joseph, John Kubiatowicz, AJ Shankar, George Necula, Alex Aiken, Eric Brewer, Ras Bodik, Ion Stoica. Doug Tvoar. and David Wagner.

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

0.0

# **Important Aspects of Memory Multiplexing**

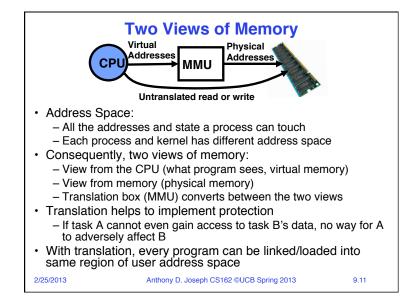

- Controlled overlap:

- Processes should not collide in physical memory

- Conversely, would like the ability to share memory when desired (for communication)

- Protection:

- Prevent access to private memory of other processes

- » Different pages of memory can be given special behavior (Read Only, Invisible to user programs, etc)

- » Kernel data protected from User programs

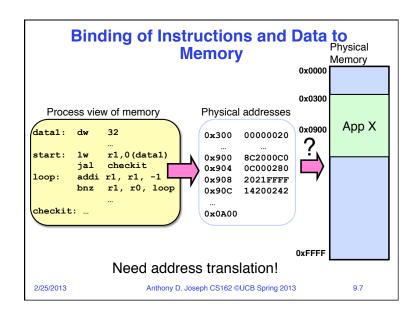

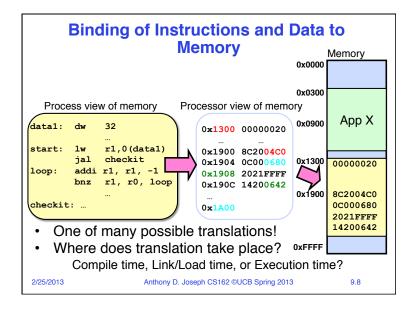

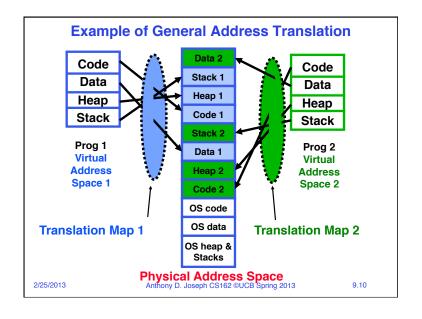

- · Translation:

- Ability to translate accesses from one address space (virtual) to a different one (physical)

- When translation exists, process uses virtual addresses, physical memory uses physical addresses

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

9.4

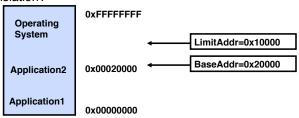

# **Multiprogramming (First Version)**

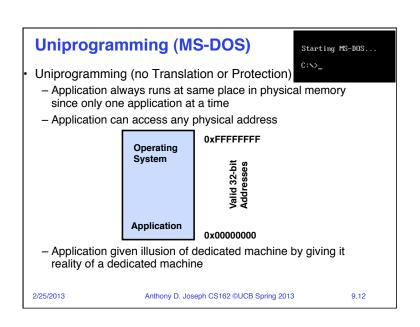

- · Multiprogramming without Translation or Protection

- Must somehow prevent address overlap between threads

Operating System 0xFFFFFFF

Application2 0x00020000

Application1 0x00000000

- Trick: Use Loader/Linker: Adjust addresses while program loaded into memory (loads, stores, jumps)

- » Everything adjusted to memory location of program

- » Translation done by a linker-loader

- » Was pretty common in early days

- With this solution, no protection: bugs in any program can cause other programs to crash or even the OS

2/25/2013 Anthony D. Joseph CS162 ©UCB Spring 2013

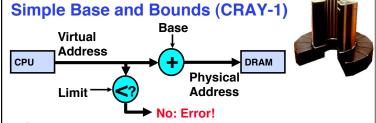

# **Multiprogramming (Version with Protection)**

Can we protect programs from each other without translation?

- Yes: use two special registers BaseAddr and LimitAddr to prevent user from straying outside designated area

- » If user tries to access an illegal address, cause an error

- During switch, kernel loads new base/limit from TCB (Thread Control Block)

- » User not allowed to change base/limit registers

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

9.14

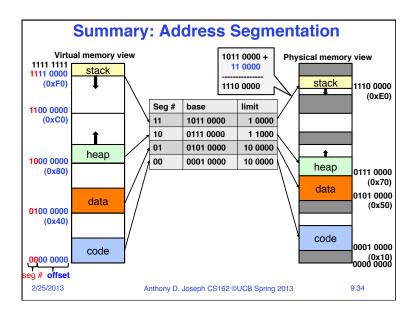

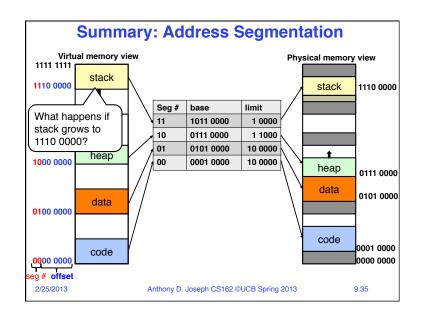

- Could use base/limit for dynamic address translation (often called "segmentation") – translation happens at execution:

- Alter address of every load/store by adding "base"

- Generate error if address bigger than limit

- This gives program the illusion that it is running on its own dedicated machine, with memory starting at 0

- Program gets continuous region of memory

- Addresses within program do not have to be relocated when program placed in different region of DRAM

2/25/2013 Anthony D. Joseph CS162 ©UCB Spring 2013

9.15

9.13

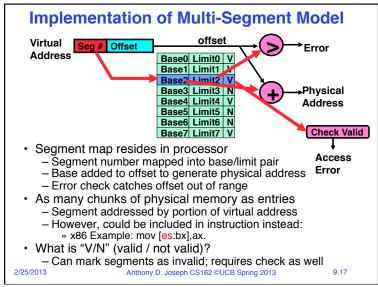

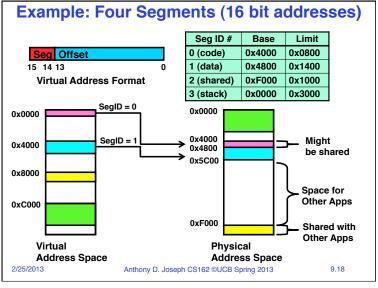

#### **More Flexible Segmentation** subroutine stack symbol Sqrt main 3 program user view of physical memory space memory space Logical View: multiple separate segments - Typical: Code, Data, Stack - Others: memory sharing, etc Each segment is given region of contiguous memory - Has a base and limit - Can reside anywhere in physical memory 9.16

**Issues with Simple Segmentation Method**

process 6

process 5

process 9

os

process 6

process 9

process 10

os

process 11

9.19

process 6

process 5

os

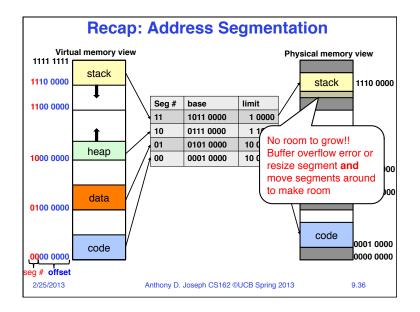

- Over time, memory space becomes fragmented

- Helped by providing multiple segments per process

Anthony D. Joseph CS162 ©UCB Spring 2013

- Want to share code segments when possible

- Want to share memory between processes

- Not every process is the same size

Hard to do inter-process sharing

process 6

process 5

process 2

Fragmentation problem

os

2/25/2013

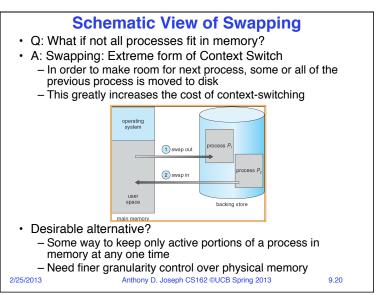

# **Problems with Segmentation**

- Must fit variable-sized chunks into physical memory

- May move processes multiple times to fit everything

- Limited options for swapping to disk

- Fragmentation: wasted space

- External: free gaps between allocated chunks

- Internal: don't need all memory within allocated chunks

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

9.21

#### **Administrivia**

- Midterm date is still pending until campus provides a time and room

- Requested Monday 3/11 or Wednesday 3/13

- Midterm review session TBA

- Project 1 due tomorrow Tue 2/26 (submit proj1code) at 11:59PM

- Design doc (submit proj1-final-design) and group evals (Google Docs form) due Wed 2/27 at 11:59PM

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

9.22

# 5min Break

2/25/2013 Anthony D. Joseph CS162 ©UCB Spring 2013

9.23

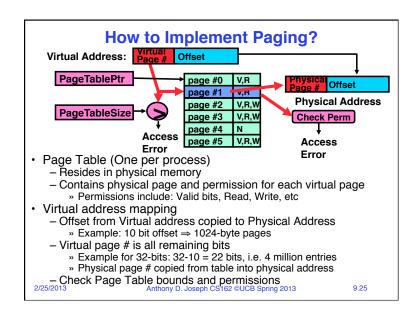

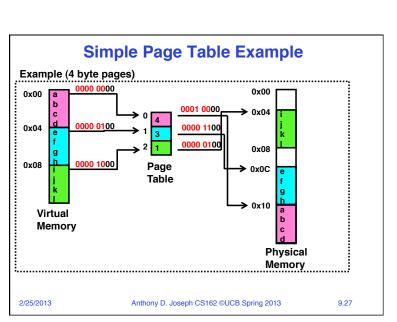

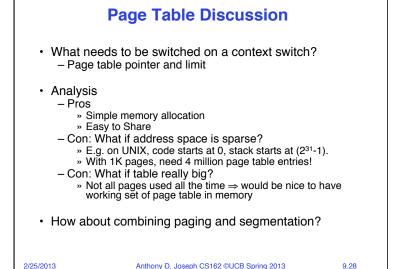

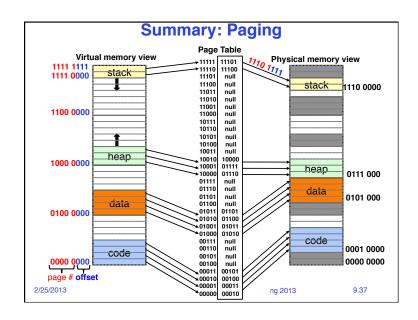

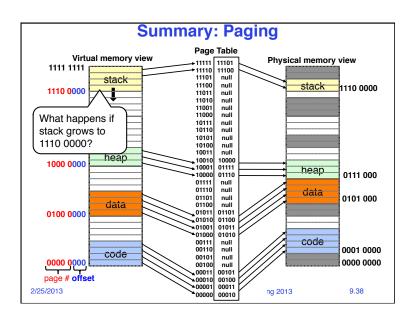

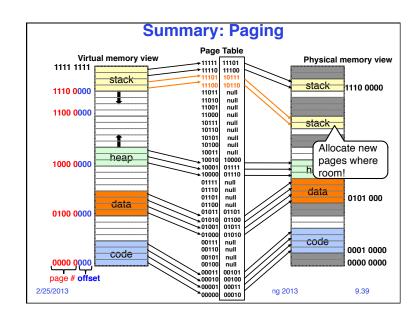

## **Paging: Physical Memory in Fixed Size Chunks**

- Solution to fragmentation from segments?

- Allocate physical memory in fixed size chunks ("pages")

- Every chunk of physical memory is equivalent

- » Can use simple vector of bits to handle allocation: 00110001110001101 ... 110010

- » Each bit represents page of physical memory 1⇒allocated, 0⇒free

- Should pages be as big as our previous segments?

- No: Can lead to lots of internal fragmentation

- » Typically have small pages (1K-16K)

- Consequently: need multiple pages/segment

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

Anthony D. Joseph CS162 ©UCB Spring 2013

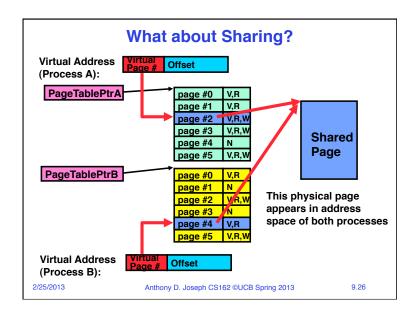

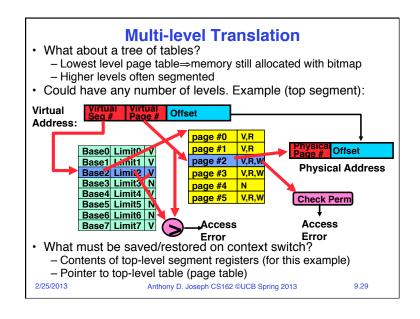

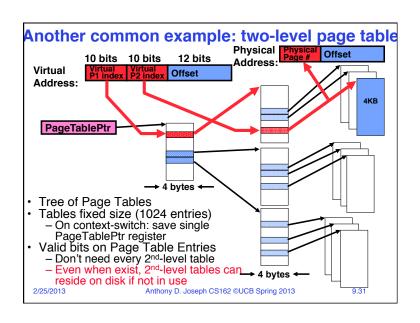

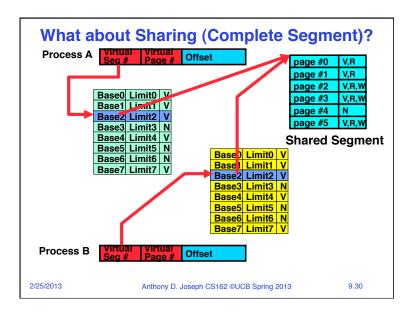

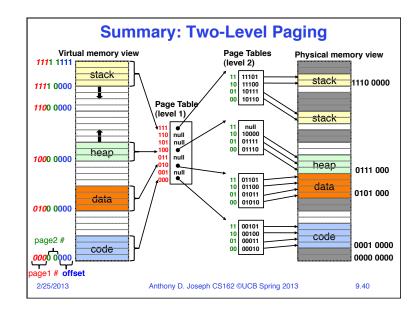

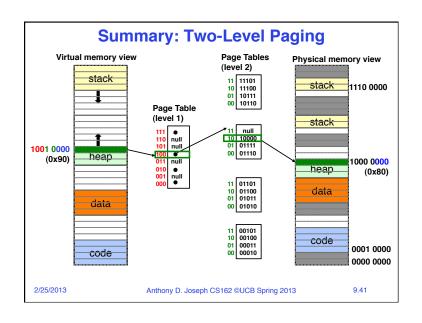

# **Multi-level Translation Analysis**

- · Pros:

- Only need to allocate as many page table entries as we need for application – size is proportional to usage

- » In other words, sparse address spaces are easy

- Easy memory allocation

- Easy Sharing

- » Share at segment or page level (need additional reference counting)

- Cons:

- One pointer per page (typically 4K 16K pages today)

- Page tables need to be contiguous

- » However, previous example keeps tables to exactly one page in size

- Two (or more, if >2 levels) lookups per reference

- » Seems very expensive!

2/25/2013

Anthony D. Joseph CS162 ©UCB Spring 2013

| Address Translation Comparison   |                                                                    |                                     |

|----------------------------------|--------------------------------------------------------------------|-------------------------------------|

|                                  | Advantages                                                         | Disadvantages                       |

| Segmentation                     | Fast context<br>switching: Segment<br>mapping<br>maintained by CPU | External fragmentation              |

| Paging<br>(single-level<br>page) | No external fragmentation, fast easy allocation                    | Large table size ~ virtual memory   |

| Paged segmentation               | Table size ~ # of pages in virtual                                 | Multiple memory references per page |

| Two-level pages                  | memory, fast easy allocation                                       | access                              |

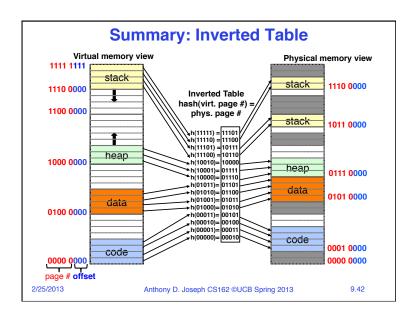

| Inverted Table                   | Table size ~ # of pages in physical memory                         | Hash function more complex          |

# **Summary** · Memory is a resource that must be multiplexed - Controlled Overlap: only shared when appropriate - Translation: Change virtual addresses into physical addresses - Protection: Prevent unauthorized sharing of resources Simple Protection through segmentation - Base+limit registers restrict memory accessible to user - Can be used to translate as well Page Tables Memory divided into fixed-sized chunks of memory - Offset of virtual address same as physical address · Multi-Level Tables Virtual address mapped to series of tables Permit sparse population of address space • Inverted page table: size of page table related to physical mem. size 2/25/2013 Anthony D. Joseph CS162 ©UCB Spring 2013 9.44