## CS162 Operating Systems and Systems Programming Lecture 11

**Page Allocation and Replacement**

March 4, 2013 Anthony D. Joseph http://inst.eecs.berkeley.edu/~cs162

## Quiz 11.1: Address Translation Q1: True \_ False \_ Paging does not suffer from external fragmentation Q2: True \_ False \_ The segment offset can be larger than

- the segment size

- Q3: True \_ False \_ Paging: to compute the physical address, add physical page # and offset

- Q4: True \_ False \_ Uni-programming doesn't provide address protection

- Q5: True \_ False \_ Virtual address space is always larger than physical address space

- Q6: True \_ False \_ Inverted page tables keeps fewer entries than two-page tables

Anthony D. Joseph CS162 ©UCB Spring 2013

3/4/2013

11.3

## **Quiz 11.1: Address Translation** • Q1: True **x** False Paging does not suffer from external fragmentation • Q2: True False X The segment offset can be larger than the segment size • Q3: True False X Paging: to compute the physical address, add physical page # and offset • Q4: True **x** False Uni-programming doesn't provide address protection • Q5: True \_ False x Virtual address space is always larger than physical address space • Q6: True X False \_ Inverted page tables keeps fewer entries than two-page tables 3/4/2013 Anthony D. Joseph CS162 ©UCB Spring 2013 11.4

| Address Translation Comparison   |                                                                    |                                     |  |  |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|--|

|                                  | Advantages                                                         | Disadvantages                       |  |  |  |  |  |  |

| Segmentation                     | Fast context<br>switching: Segment<br>mapping<br>maintained by CPU | External fragmentation              |  |  |  |  |  |  |

| Paging<br>(single-level<br>page) | No external<br>fragmentation                                       | Large table size ~ virtual memory   |  |  |  |  |  |  |

| Paged segmentation               | Table size ~ # of<br>virtual memory                                | Multiple memory references per page |  |  |  |  |  |  |

| Two-level<br>pages               | pages allocated to the process                                     | access                              |  |  |  |  |  |  |

| Inverted Table                   | Table size ~ # of<br>pages in physical<br>memory                   | Hash function more complex          |  |  |  |  |  |  |

| Quiz 11.2: Caches & TLBs                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| <ul> <li>Q1: True _ False _ Associative caches have fewer compulsory misses than direct mapped caches</li> <li>Q2: True _ False _ Two-way set associative caches can cache two addresses with same cache index</li> <li>Q3: True _ False _ With write-through caches, a read miss can result in a write</li> <li>Q4: True _ False _ LRU caches are more complex than Random caches</li> <li>Q5: True _ False _ A TLB caches translations to virtual addresses</li> </ul> |  |  |  |  |  |  |  |  |

| 3/4/2013 Anthony D. Joseph CS162 ©UCB Spring 2013 11.6                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

## Quiz 11.2: Caches & TLBs Q1: True \_ False X Associative caches have fewer compulsory misses than direct mapped caches Q2: True X False \_ Two-way set associative caches can cache two addresses with same cache index Q3: True \_ False X With write-through caches, a read miss can result in a write Q4: True X False \_ LRU caches are more complex than Random caches Q5: True \_ False X A TLB caches translations to virtual addresses

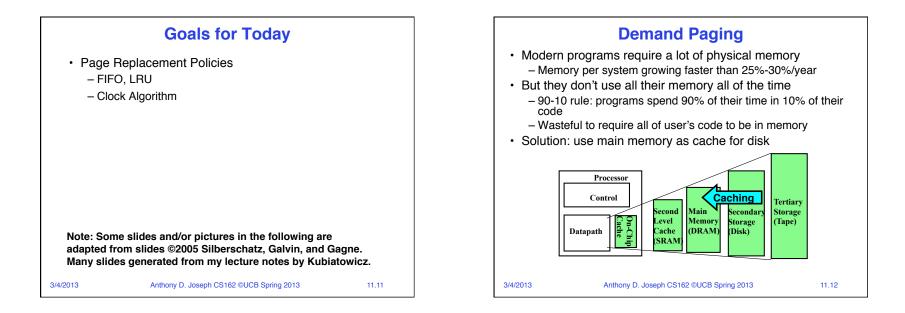

| Demand Pagi <ul> <li>Since Demand Paging is C</li> </ul>                                          | ng is Caching<br>Caching, we must ask: | Demand Paging Mechanisms           • PTE helps us implement demand paging           - Valid ⇒ Page in memory, PTE points at physical page                                                            |

|---------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Question                                                                                          | Choice                                 | <ul> <li>Not Valid ⇒ Page not in memory; use info in PTE to find it or<br/>disk when necessary</li> </ul>                                                                                            |

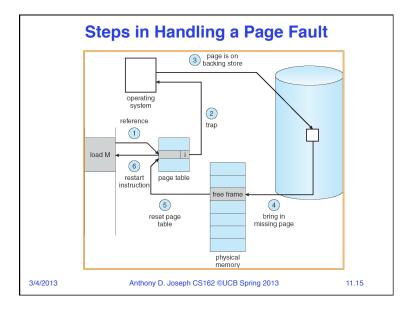

| What is the block size?                                                                           |                                        | <ul> <li>Suppose user references page with invalid PTE?</li> <li>– Memory Management Unit (MMU) traps to OS</li> </ul>                                                                               |

| What is the organization of this cache (i.e., direct-mapped, set-associative, fully-associative)? |                                        | <ul> <li>When for y management of the (MMO) traps to OS</li> <li>» Resulting trap is a "Page Fault"</li> <li>– What does OS do on a Page Fault?:</li> <li>» Choose an old page to replace</li> </ul> |

| How do we find a page in the cache?                                                               |                                        | <ul> <li>If old page modified ("D=1"), write contents back to disk</li> <li>Change its PTE and any cached TLB to be invalid</li> </ul>                                                               |

| What is page replacement policy? (i.e., LRU, Random,)                                             |                                        | <ul> <li>» Load new page into memory from disk</li> <li>» Update page table entry, invalidate TLB for new entry</li> </ul>                                                                           |

| What happens on a miss?                                                                           |                                        | <ul> <li>Continue thread from original faulting location</li> <li>TLB for new page will be loaded when thread continued!</li> </ul>                                                                  |

| What happens on a write? (i.e., write-through, write-back)                                        |                                        | <ul> <li>While pulling pages off disk for one process, OS runs anothe<br/>process from ready queue</li> </ul>                                                                                        |

| <b>.</b> ,                                                                                        |                                        | » Suspended process sits on wait queue                                                                                                                                                               |

| 3/4/2013 Anthony D. Joseph CS1                                                                    | 62 ©UCB Spring 2013 11.13              | 3/4/2013 Anthony D. Joseph CS162 ©UCB Spring 2013 11.14                                                                                                                                              |

11.18

| When will LRU perform badly?                                                        |       |   |   |   |   |   |   |   |   |   |   |   |   |

|-------------------------------------------------------------------------------------|-------|---|---|---|---|---|---|---|---|---|---|---|---|

| Consider the following: A B C D A B C D A B C D                                     |       |   |   |   |   |   |   |   |   |   |   |   |   |

| LRU Performs as follows (same as FIFO here):                                        |       |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                                     | Ref:  | Α | в | С | D | Α | в | С | D | Α | в | С | D |

|                                                                                     | Page: |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                                     | 1     | Α |   |   | D |   |   | С |   |   | в |   |   |

|                                                                                     | 2     |   | в |   |   | Α |   |   | D |   |   | С |   |

|                                                                                     | 3     |   |   | С |   |   | в |   |   | Α |   |   | D |

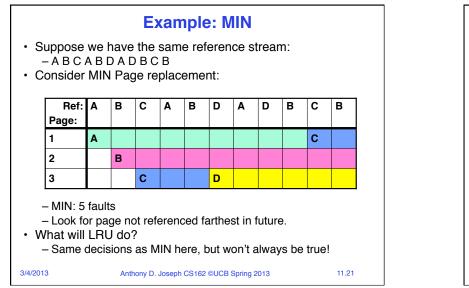

| <ul> <li>Every reference is a page fault!</li> <li>MIN Does much better:</li> </ul> |       |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                                     | Ref:  | Α | В | С | D | Α | в | С | D | Α | В | С | D |

|                                                                                     | Page: |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                                     | 1     | Α |   |   |   |   |   |   |   |   | в |   |   |

|                                                                                     | 2     |   | в |   |   |   |   | С |   |   |   |   |   |

| 3/4                                                                                 | 3     |   |   | С | D |   |   |   |   |   |   |   |   |