|

Course Format:

Ninety minutes of lecture and 2 hours of project management

meetings per week. A semester-long digital systems design project is

the centerpiece of the course.

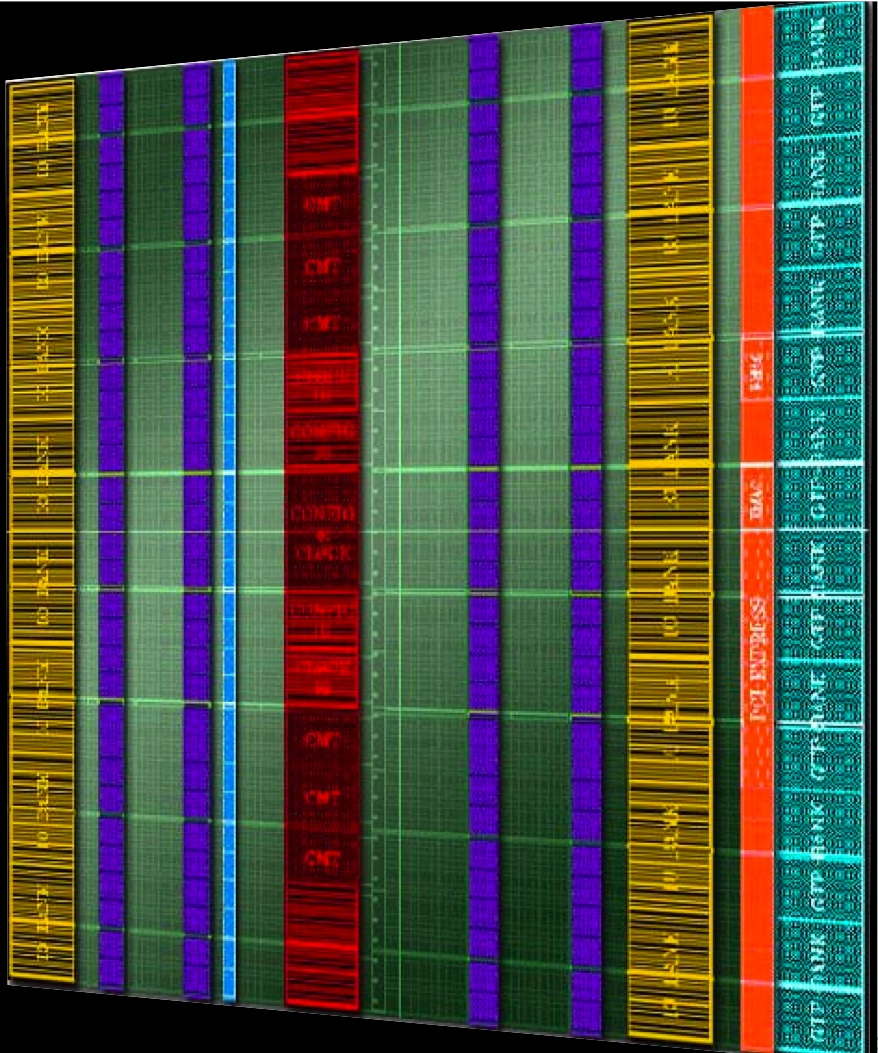

Topics: FPGA design, digital systems design, computer

architecture, network hardware design, graphics, video, and audio

hardware architecture, impact of VLSI issues on microarchitecture.

Prerequisite: For undergraduates, EECS 150.

Location: Lectures are on Monday 10:30-12:00, 405 Soda Hall.

Project management meetings will be scheduled on Fridays 10 AM to noon,

in 125 Cory, or at the Berkeley Wireless Research Center (BWRC).

Project Description:

Projects will create versatile medium-scale hardware IP with

associated testbenches, for applications compatible with RAMP Gold.

Application areas include CPU and GPU design, networks on chip, audio

and video processing -- other ideas are welcome.

The goal is completed IP that will be usable as building blocks by

future RAMP Gold developers. To achieve this goal, projects should be:

- Versatile: By using parameterized Verilog or a generator approach, a

RAMP Gold developer should be able to customize the IP. Deciding

on the appropriate level of customizability will be an important part

of the design exercises.

- Designed for FPGA: Projects should be data-path-centric, use FIFO

handshaking for I/O interfaces, and use data-stationary control.

Low-level aspects of the design should be optimized for an FPGA

L1fabric. If a project idea can be efficiently run on a CPU, it is

probably a bad choice for this class.

Projects will use these technologies:

- High-level languages: RDL for architecture projects, Simulink for DSP.

- Deliverable format: A parameterized Verilog module or an RCF-based Java program.

- Testbench format: A Java program written using JavaAPI.

- Low-level signalling: The RAMP FIFO signalling standard.

- System platform: ML-505/XUPv5 or BEE3.

- Silicon plaform: Xlinix Virtex5 LX (110 or 155).

- Management: In-class design reviews

Course Operation:

CS 194-6 is a pure project class (no exams or homeworks).

Grades will be based on three student presentations during

lecture: a project specification design review early in the term, a

project implementation design review near the mid-point of the

semester, and a final project review on the last lecture date of the

semester. Revised versions of the presentation slides (in PDF format)

are due via email to the instructor and the TA, by the deadline listed

on the class calendar.

Lectures will cover material that will be useful for the project.

Many of the Friday project management meetings will be in the lab, so

that the TA and instructor can help to diagnose problems in project

planning and implementation.

The recommended text is

Computer Organization and Design: The Hardware/Software Interface,

Third Edition, by David A. Patterson and John L. Hennessy.

Academic Honesty:

Like all EECS courses, CS 194-6 follows the EECS

Departmental Policy on Academic Dishonesty. Please follow the link

and read the policy and become aware of our expectations.

|