The design of efficient storage hierarchies generally involves the repeated running of "typical" program address traces through a simulated storage system while various hierarchy design parameters are adjusted.

This paper describes a new and efficient method of determining, in one pass of an address trace, performance measures for a large class of demand-paged, multilevel storage systems utilizing a variety of mapping schemes and replacement algorithms.

The technique depends on an algorithm classification, called "stack algorithms," examples of which are "least frequently used," "least recently used," "optimal," and "random replacement" algorithms. The techniques yield the exact access frequency to each storage device, which can be used to estimate the overall performance of actual storage hierarchies.

# Evaluation techniques for storage hierarchies

· 是是一天中心的人也是不知识,是是一个人的人,也不是一个人的人的人,也是一个人的人的人的人,也是一个人的人的人的人的人,也是一个人的人的人的人的人的人,也是一

by R. L. Mattson, J. Gecsei, D. R. Slutz, and I. L. Traiger

Increasing speed and size demands on computer systems have resulted in corresponding demands on storage systems. Since it has been generally recognized that the speed and capacity requirements of storage systems cannot be fulfilled at an acceptable cost-performance level within any single technology, storage hierarchies that use a variety of technologies have been investigated.

Several previous papers describe the general concepts of hierarchy design<sup>1-3</sup> and evaluation,<sup>4-6</sup> whereas others deal with specific hierarchy systems, such as the core-drum combination on the ICT Atlas computer<sup>7-9</sup> and the cache-core combination on the IBM System/360, Model 85.<sup>10,11</sup>

This paper introduces an efficient technique called "stack processing" that can be used in the cost-performance evaluation of a large class of storage hierarchies. The technique depends on a classification of page replacement algorithms as "stack algorithms" for which various properties are derived. These properties may be of use in the general areas of program modeling and system analysis, as well as in the evaluation of storage hierarchies. For a better understanding of storage hierarchies, we briefly review some basic concepts of their design.

MATTSON, GECSEI, SLUTZ, AND TRAIGER

78

IBM SYST J

The purpose of a st associate the informathe remainder of the Processing Unit (CPU system with instruction associated with a single device, then to the physical addressystem with the same of storage devices rarelatively inexpensive logical address space (or unequal-size segment being moved between

A hierarchy manager ment of pages and a between the logical a of the hierarchy. Whierarchy management tion of the correspo page to a fast storage these actions are "tra system (except for the is indistinguishable fra

The goal of the hiera number of times logi being referenced. As directed to the fast, sr. space is distributed system then acquires while maintaining the less expensive stores primary justification f

Clearly, many factors hierarchy. On the peri and characteristics of of the hierarchy, the hierarchy managemen references. On the cost to find and move log as the cost-per-bit an factors, it is quite diffi

The typical approach t designers has been to si at various levels of de large number of rela

; the gh a leters

g, in class y of

*₹tack* least hms. rage e of

lave e it iireosthies

chy ific the the

1g" rge cafor of sis, ter sic

T J

The purpose of a storage system is to hold information and to associate the information with a logical address space known to the remainder of the computer system. For example, the Central Processing Unit (CPU) may present a logical address to the storage system with instructions to either retrieve or modify the information associated with that address. If the storage system consists of a single device, then the logical address space corresponds directly to the physical address space of the device. Alternatively, a storage system with the same address space can be realized by a hierarchy of storage devices ranging from fast but expensive to slower but relatively inexpensive devices. In such storage hierarchies, the logical address space is often partitioned into equal-size pages (or unequal-size segments) that represent the blocks of information being moved between devices in the hierarchy.

A hierarchy management facility is included to control the movement of pages and to effect the (generally dynamic) association between the logical address space and the physical address space of the hierarchy. When the CPU references a logical address, the hierarchy management facility first determines the physical location of the corresponding logical page and may then move the page to a fast storage device where the reference is effected. Since these actions are "transparent" to the remainder of the computer system (except for timing), the logical operation of the hierarchy is indistinguishable from that of a single-device system.

The goal of the hierarchy management facility is to maximize the number of times logical information is in the faster devices when being referenced. As this goal is approached, most references are directed to the fast, small stores whereas most of the logical address space is distributed over the slower, large stores. The storage system then acquires the approximate speed of the fast stores while maintaining the approximate cost-per-bit of the slower and less expensive stores. This increase in cost-performance is the primary justification for storage hierarchies.

Clearly, many factors can affect the cost-performance of a storage hierarchy. On the performance side, one must consider the capacity and characteristics of each storage device, the physical structure of the hierarchy, the way in which information is moved by the hierarchy management facility, and the expected pattern of storage references. On the cost side, the hardware and/or software required to find and move logical information must be considered, as well as the cost-per-bit and capacity of each device. Because of these factors, it is quite difficult to design an "optimal" hierarchy.

The typical approach to hierarchy evaluation employed by computer designers has been to simulate as many hierarchy systems as possible, at various levels of detail. 9-12 During the first stages of design, a large number of relatively simple simulations may be run with

hierarchy concepts

References to th

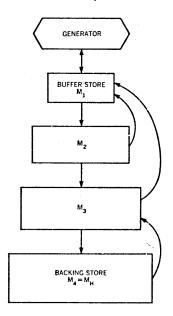

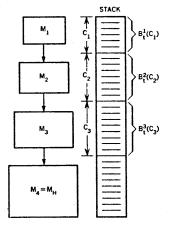

Figure 1 Linear storage hierarchy

objectives of the paper

fixed, standard address traces. These traces are assumed to be "typical" sequences of storage references obtained from existing computer systems, and they are used to approximate the reference behavior of future systems. The purpose of these simulations is to measure such statistics as data flow and frequency of access to each device in order to estimate the overall performance of an actual system. The resulting performance estimates can then be used to narrow the field of possible designs, which then receive more detailed examination.

Alternatively, one may try to develop analytical techniques that avoid point-by-point simulation but still yield accurate statistics for data flow and access frequencies. Several papers deal with such techniques for hierarchy evaluation.4-6 In general, the approach here is to run a relatively small number of simulations and extrapolate the measured statistics to a larger class of hierarchies. The difficulty with this approach is the need for various assumptions about the statistical properties of address traces and data flows required to formulate the analytical equations. Moreover, it is difficult to include a quantitative dependence on such factors as data path structure, page replacement algorithm, 13 and address mapping scheme,<sup>3</sup> so that many simulations may still be necessary.

This paper presents a technique that can be used to circumvent much of the simulation effort required in hierarchy evaluation. Specifically, we present an efficient procedure that determines, for a given address trace, the exact frequency of access to each level of a hierarchy as a function of page size, replacement algorithm, number of levels, and capacity at each level. In the following, we consider a class of multilevel, demand-paging hierarchies<sup>14</sup> with the same replacement algorithm at every level. The procedures developed here are applicable to a large class of well-known replacement algorithms having certain inclusion properties defined later. These algorithms-which we call stack algorithms-include "least frequently used," "least recently used," "optimal," and a "random" replacement algorithm.

### The system model

basic model concepts

80

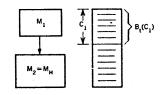

An H-level paged storage hierarchy consists of a collection of storage devices  $M_1, M_2, \cdots, M_H$ , a network of data paths connecting the devices, and a hierarchy management facility. Each device is partitioned into physical blocks called page frames. For convenience, the highest-level store  $M_1$  is called the *local store* and the lowest-level store  $M_H$  is the backing store as shown in Figure 1. The hierarchy management facility controls page movement between the devices and associates each logical page with a physical page frame. Special storage and processing hardware may be required, but they are not included in our model.

called the genera in which they a may represent th the channel, in address reference where each add set of 2<sup>n</sup> possit logical addresses resent the num low-order n the address with hierarchy is acc we can analyze by considering a where each  $x^{k}$ When we consid and denote page

A reference fro local store  $M_1$ . device  $M_i$ , i.e. must bring that a path for bring staging through for bringing a p ment hardware. In this paper we in which the on direct ones from H-1. The real paper. Note the hierarchy.

The capacity of frames, and all At any time, ea of the hierarchy erarchical level, it may occupy in

- Unconstraine storage devic

- Fully constra frame.

- Partially con:

In a later section that generates a

No. 2 · 1970

IBM SYST J

ned to be

n existing

reference

tions is to

access to

access to

ac of an

then be

n receive

ques that statistics with such approach and exerarchies. umptions ata flows ver, it is actors as l address necessary.

reumvent aluation.

nines, for ach level lgorithm, wing, we es<sup>14</sup> with rocedures nown res defined—include," and a

ection of the conty. Each nes. For cal store hown in the moveage with hardware References to the storage hierarchy are presented by a single device called the generator, and they are sequentially serviced in the order in which they are presented. References from the generator may may represent the requests of several devices, such as the CPU and the channel, in an actual system. The time sequence of logicaladdress references  $X = x_1, x_2, \dots, x_L$  is called an address trace, where each address consists of n bits as shown in Figure 2. The set of  $2^n$  possible addresses is partitioned into  $2^k$  pages of  $2^{n-k}$ logical addresses each. The high-order k bits of each address represent the number of the page containing the address, and the low-order n - k bits represent the location or displacement of the address within the page. Since information movement on the hierarchy is accomplished by transferring pages between levels, we can analyze space allocation and data movement for a trace Xby considering a corresponding page trace  $X^k = x_1^k, x_2^k, \dots, x_L^k$ where each  $x_i^k$  is the number of the page containing address  $x_i$ . When we consider a given fixed page size, we omit the superscript k, and denote pages by  $x_i$ .

A reference from the generator can be serviced only from the local store  $M_1$ . Thus if the desired page resides in a lower level device  $M_i$ , i.e. where i > 1, the hierarchy management facility must bring that page up to  $M_1$  for servicing. The hierarchy provides a path for bringing pages up to  $M_1$ , which may or may not require staging through intermediate levels. Any temporary storage required for bringing a page up to  $M_1$  is included in the hierarchy management hardware, and is therefore not represented in our model. In this paper we restrict our attention to linear storage hierarchies in which the only paths for moving pages down the hierarchy are direct ones from each level  $M_i$  to level  $M_{i+1}$ , where  $i = 1, 2, \cdots$ , H - 1. The reasons for this restriction are discussed later in this paper. Note that the four-level hierarchy in Figure 1 is a linear hierarchy.

The capacity of the backing store is assumed to be at least 2<sup>k</sup> page frames, and all logical pages initially reside in the backing store. At any time, each logical page resides in exactly one page frame of the hierarchy. A mapping function is associated with each hierarchical level, and specifies for each logical page the page frames it may occupy in that level. The mapping function is further defined as:

- Unconstrained if any page can occupy any page frame of the storage device.

- Fully constrained if each page can occupy only a single page frame.

- Partially constrained in all other cases.

In a later section, we define a technique called "congruence mapping" that generates a whole spectrum of mapping functions.

3M SYST J No. 2 · 1970

STORAGE HIERARCHY EVALUATION

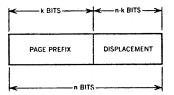

Figure 2 Logical address

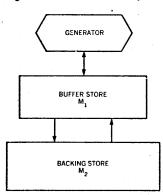

Figure 3 Two-level hierarchy

For simplicity in developing techniques for analyzing storage hierarchies, we first consider a two-level, demand-paged hierarchy with unconstrained mapping. Later, our results are extended to certain classes of multilevel linear hierarchies employing the three types of mapping functions. The local store or buffer has a capacity of C pages, and is directly connected to the backing store as shown in Figure 3. At time t, the generator presents a request for page  $x_t$  to the hierarchy. Under demand paging, if  $x_t$  is in the buffer, the reference proceeds and no page movement occurs. Otherwise,  $x_t$  is brought to the buffer from the backing store. If the buffer is already full,  $x_t$  replaces some page  $y_t$  in the buffer. The selection of the particular page  $y_t$  is performed by the buffer replacement algorithm. This operation is a key element of storage management.

In the two-level hierarchy shown in Figure 3, a reference to a page residing either at level  $M_1$  or at  $M_2$  is called an access to that level.

For a given hierarchy and page trace, we define the access frequencies  $F_1$  and  $F_2$  where  $F_i$  is the relative number of accesses to level  $M_i$  during the processing of the trace. Thus, if  $N_1$  accesses are made to level  $M_1$ , and  $N_2 = L - N_1$  accesses are made to level  $M_2$ , we obtain  $F_1 = N_1/L$  and  $F_2 = N_2/L$ .

Some important measures of storage hierarchy performance can be obtained from these access frequencies. For example, one can combine access frequencies with a set of effective access times  $\{T_i\}$  to obtain an effective (or average) hierarchy access time

$$\bar{T} = F_1 T_1 + F_2 T_2$$

In general, access times depend on the access paths, device access times, and characteristics of the hierarchy management facility. The access frequencies depend only on the page trace, capacity of the buffer, and replacement algorithm.

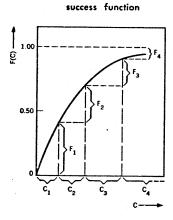

For a two-level hierarchy, accesses to the buffer are called *successes*; the relative frequency of successes as a function of capacity is given by the *success function* F(C). For a given capacity C, page trace  $X = x_1, x_2, \dots x_L$ , replacement algorithm, and arbitrary time t (where  $1 \le t \le L$ ), the set of pages in the buffer just after the completed reference to  $x_t$  is denoted by  $B_t(C)$ . The initial buffer contents is represented by  $B_0(C)$ . By convention

$$B_0(C) = \phi$$

for all C where  $\phi$  is the empty set. The set of distinct pages referenced in  $x_1, x_2, \dots, x_t$  is denoted by  $\Gamma_t$ , and the number of pages in  $\Gamma_t$  is denoted by

$$\gamma_i = |\Gamma_i|$$

82

MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

Demand paging in the following require union of disjoint sets

1. If

$$x_i \in B_{i-1}(C)$$

2. If

$$x_t \notin B_{t-1}(C)$$

$$B_{\iota}(C) = B_{\iota-1}(C)$$

3. If

$$x_t \notin B_{t-1}(C)$$

$$B_t(C) = B_{t-1}(C)$$

where  $y_t \in B_{t-1}(C)$ Under demand pagir by 1 and 2, while a sequently, referenced

# Least recently us

We now consider a recently used" (LRI can be obtained by trace. Briefly, the sof a list of pages, con this stack for exdistances are used to the LRU stack for the LRU replacement, son the related concerns.

Under LRU, the panot been referenced used page). One we trace is to simulate capacity. Such a sintime t, and counts is found in the busimulation procedu C = 1, 2, 3, 4. Paguccesses are marke

A greatly simplifie under LRU replace of that replacement capacity C, the but it fills up with the At time  $\tau$ , the buffer through time  $\tau$ . W  $(t > \tau)$ , this page re

g storage hired hierarchy extended to ing the three as a capacity ore as shown test for page n the buffer, s. Otherwise, If the buffer The selection replacement management.

ce to a page to that level.

s frequencies to level  $M_i$ es are made level  $M_2$ , we

ple, one can access times s time

levice access nent facility. ce, capacity

ed successes; capacity is ity C, page id arbitrary er just after initial buffer

s referenced pages in Γ,

IBM SYST J

Demand paging in the two-level hierarchy is formally defined by the following requirements, wherein the operator "+" denotes the union of disjoint sets:

1. If

$$x_{t} \in B_{t-1}(C)$$

then  $B_{t}(C) = B_{t-1}(C)$

2. If  $x_{t} \notin B_{t-1}(C)$  and  $|B_{t-1}(C)| < C$  then  $B_{t}(C) = B_{t-1}(C) + \{x_{t}\}$ ,

3. If  $x_{t} \notin B_{t-1}(C)$  and  $|B_{t-1}(C)| = C$  then  $B_{t}(C) = B_{t-1}(C) - \{y_{t}\} + \{x_{t}\}$

where  $y_i \in B_{i-1}(C)$  is determined by the replacement algorithm. Under demand paging, a buffer of capacity C simply fills as required by 1 and 2, while the first C distinct pages are referenced. Subsequently, referenced pages are swapped in, as required by 1 and 3.

# Least recently used replacement

We now consider a particular replacement algorithm called "least recently used" (LRU), and show that the entire success function can be obtained by stack processing in a single pass of the address trace. Briefly, the single-pass technique requires the maintaining of a list of pages, called an LRU stack, and measuring a distance on this stack for every page reference. Frequencies of these stack distances are used to calculate the success function. The existence of the LRU stack follows from an inclusion property satisfied by LRU replacement, whereas the use of distance frequencies hinges on the related concept of critical capacity.

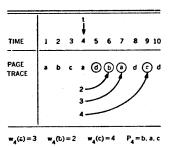

Under LRU, the page selected for replacement is the one that has not been referenced for the longest time (i.e., the least recently used page). One way to obtain the success function for a given trace is to simulate the two-level hierarchy system for each buffer capacity. Such a simulation determines the buffer contents at every time t, and counts the number of times the current reference  $x_t$  is found in the buffer. In Figure 4, we show an example of this simulation procedure for a given page trace and buffer capacities C = 1, 2, 3, 4. Pages are denoted by lower-case letters, and page successes are marked by asterisks.

A greatly simplified method for obtaining the success function under LRU replacement can be derived from certain properties of that replacement algorithm. For any page trace and buffer capacity C, the buffer is initially empty, and in say  $\tau$  time units, it fills up with the first C distinct pages referenced by the trace. At time  $\tau$ , the buffer contains the C pages most recently referenced through time  $\tau$ . When a new page is referenced at a later time  $(t > \tau)$ , this page replaces the least recently used page in the buffer.

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

success function

Figure 4 Determining success function by buffer simulation

| TIME                 | 1 | 2      | 3      | 4           | 5           | 6           | 7           | 8                | 9                | 10          |

|----------------------|---|--------|--------|-------------|-------------|-------------|-------------|------------------|------------------|-------------|

| PAGE TRACE           | a | Ь      | ь      | с           | b           | а           | đ           | с                | а                | а           |

| SIMULATIONS          |   |        |        |             |             |             |             |                  |                  |             |

| C=1<br>F(1)=0.20     | a | ь      | •      | С           | ь           | a           | đ           | c                | а                | a           |

| C = 2<br>F(2) = 0.30 | а | ь      | a<br>b | c<br>b      | c<br>b      | a<br>b      | a<br>d      | c<br>d           | c                | c<br>a      |

| C = 3<br>F(3) = 0.50 | а | a<br>b | a<br>b | a<br>b<br>c | a<br>b<br>c | a<br>b<br>c | a<br>b      | c<br>d           | a<br>c<br>d      | a<br>c<br>d |

| C = 4<br>F(4) = 0.60 | a | a      | a<br>b | a<br>b<br>c | a<br>b<br>c | a<br>b<br>c | a<br>b<br>c | a<br>b<br>c<br>d | a<br>b<br>c<br>d | a<br>b<br>c |

Thus at time t, the buffer still contains the C most recently referenced pages. It is easy to see that under LRU the buffer contains the C most recently referenced pages for all subsequent times, and that this property holds for all page traces and buffer capacities. One can generate the buffer contents  $B_t(C)$  for any time t on a trace and any capacity by scanning backward from point t and collecting the first C distinct pages encountered.

Since the set of C most recently referenced pages is always contained in the set of C+1 most recently referenced pages, the buffer contents  $B_t(C)$  at any time must be a subset of  $B_t(C+1)$ . In fact,  $B_t(C)$  is a proper subset of  $B_t(C+1)$  if at least C+1 distinct pages have been referenced through time t. More formally, under LRU replacement, the buffer contents for any page trace  $X=x_1, x_2, \cdots, x_L$  and any time t (where  $1 \le t \le L$ ) satisfy the following inclusion property:

$$B_t(1) \subset B_t(2) \subset \cdots \subset B_t(\gamma_t) = B_t(\gamma_t + 1) = \cdots$$

(1)

where

$$|B_t(C)| = C$$

for  $1 \le C \le \gamma_t$

MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

and

$$|B_i(C)| = \gamma_i$$

The inclusion t = 5, for example 1

$$B_i(1) = \{b\}$$

$$B_t(2) = \{c, b$$

$$B_t(3) = \{a, t\}$$

and

$$B_{\iota}(4) = \{a, b \mid$$

Because of the and for all canned useful was,  $(2), \dots s_i(\gamma)$

$$s_t(i) = B_t(i) -$$

Hence

$$B_t(C) = \begin{cases} \{s_t\} \\ \{s_t\} \end{cases}$$

The list  $S_t$  is entry and  $s_t(\gamma)$  for t = 5 in F

$$S_5 = [b, c, a]$$

The stack  $S_0$ : null stack, the LRU stacks C

Besides repressable stack can be F(C). Let us referenced and  $1 \le C \le \gamma_t$ .

$$x_i \in B_{i-1}(C)$$

We call C, the given in Equal not been previous contained in a

From the defithat  $C_i$  is sim-

and

$$|B_t(C)| = \gamma_t \quad \text{for } C \geq \gamma_t$$

The inclusion property can be observed in Figure 4 where at time t = 5, for example

$$B_i(1) = \{b\}$$

$$B_t(2) = \{c, b\}$$

$$B_{c}(3) = \{a, b, c\}$$

and

$$B_t(4) = \{a, b, c\}$$

Because of the inclusion property, the buffer contents at any time and for all capacities can be represented in the following compact and useful way. We order the set of pages  $\Gamma_t$  into a list  $S_t = s_t(1)$ ,  $s_i(2), \cdots s_i(\gamma_i)$ , where

$$s_i(i) = B_i(i) - B_i(i-1)$$

for  $i = 1, 2, \dots, \gamma_i$  (2)

Hence

$$B_{t}(C) = \begin{cases} \{s_{t}(1), s_{t}(2), \cdots, s_{t}(C)\} & \text{for } C \leq \gamma_{t} \\ \{s_{t}(1), s_{t}(2), \cdots, s_{t}(\gamma_{t})\} & \text{for } C \geq \gamma_{t} \end{cases}$$

(3)

The list  $S_t$  is referred to as the LRU stack, with  $s_t(1)$  as the top entry and  $s_i(\gamma_i)$  as the bottom entry. As an example, the LRU stack for t = 5 in Figure 4 is

$$S_5 = [b, c, a]$$

The stack  $S_0$  at time t = 0 has no entries and is therefore called a null stack, that is, one with no entries. The entire sequence of LRU stacks corresponding to Figure 4 is included in Figure 5.

Besides representing the buffer contents for all capacities, the LRU stack can be used to efficiently determine the success function F(C). Let us suppose that at time t, page  $x_i$  has been previously referenced and thus is a member of at least one set  $B_{t-1}(C)$ , where  $1 \le C \le \gamma_{t-1}$ . Let  $C_t$  denote the least buffer capacity such that  $x_i \in B_{i-1}(C)$

We call

$$C_t$$

the *critical capacity* since, from the inclusion property given in Equation 1,  $x_t \in B_{t-1}(C)$  if and only if  $C \ge C_t$ . If  $x_t$  has not been previously referenced, we set  $C_t = \infty$  because  $x_t$  is not contained in a buffer of any finite capacity.

From the definition of LRU stacks in Equation 2, it may be seen

that  $C_i$  is simply the position of page  $x_i$  in the stack  $S_{i-1}$ , so that

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

85

M SYST J

ferenced is the C

and that

ies. One

a trace

ollecting

ontained

e buffer

In fact,

distinct y, under

ce X =

the fol-

(1)

Figure 5 Sequence of LRU stacks

| TIME                      | 1          | 2         | 3   | 4          | 5.    | 6            | 7                                     | 8          | 9           | 10         |

|---------------------------|------------|-----------|-----|------------|-------|--------------|---------------------------------------|------------|-------------|------------|

| PAGE TRACE                | а          | b         | b   | с          | b     | а            | d                                     | c          | а           | a          |

|                           | а          | b         | ь   | c          | ь     | a .          | ď                                     | ۰ - ۲      | <b>/→</b> a | a          |

| LRU STACK                 |            | a         | a   | <b>^</b> b | ] ، 🟲 | <b>A</b> b   | • • ]                                 | <b>a</b> 3 | c c         | С          |

|                           |            |           |     | <b>*</b> a | ر •   | <b>`</b> ` ( | * p [                                 | ` 。/       | d           | đ          |

|                           |            |           |     |            |       |              | ` .)                                  | ь          | ь           | b          |

| STACK<br>DISTANCE         | <b>6</b> 0 |           | 1   | <b>c</b> o | 2     | 3            | <b>6</b> 0                            | 4          | 3           | 1          |

| DISTANCE<br>COUNTERS n(1) |            | <u></u> - |     |            |       | <del></del>  | · · · · · · · · · · · · · · · · · · · |            |             |            |

| 1                         | 0          | 0         | ,1  | 1          | 1     | 1            | 1                                     | 1          | 1           | (2)        |

| 2                         | 0          | ð         | 0   | 0          | 1     | . 1          | 1                                     | 1          | 1           | <u>(1)</u> |

| 3                         | 0          | 0         | . 0 | 0          | 0     | 1            | 1                                     | 1          | 2           | (2)        |

| 4                         | 0          | 0         | 0   | 0          | 0     | 0            | 0                                     | 1          | 1           | (1)        |

| ∞                         | 1          | 2         | 2   | 3          | 3     | 3            | 4                                     | 4          | 4           | 4          |

Figure 6 Obtaining success function from distance frequencies

DISTANCE FREQUENCY

B SUCCESS FUNCTION

$$x_t = s_{t-1}(C_t)$$

We call this page position the stack distance  $\Delta_i$ , since  $\Delta_i$  is essentially the "distance" from the top of the stack to

$$X_t = S_{t-1}(\Delta_t)$$

(Note that here  $\Delta_t = C_t$ . When constrained mapping functions are considered, the stack distance may not always equal the critical capacity.) If  $x_i$  has not been previously referenced, then  $\Delta_i$  is set to infinity. The sequence of stack distances for our example is included in Figure 5.

The significance of stack distances is that they lead directly to the success function. To see this, let  $n(\Delta)$  be the number of times the stack distance  $\Delta$  is observed in processing a trace. Since the stack distance equals the critical capacity, the number of times that the referenced page is found in the buffer is

$$N(C) = \sum_{\Delta=1}^{C} n(\Delta) \tag{4}$$

and the success function is given by the expression

$$F(C) = N(C)/L (5)$$

In practice, the set  $\{n(\Delta)\}\$  can be determined from a set of distance counters, as shown in Figure 5. All counters are set initially to zero, and the counter for each distance  $\Delta$  is incremented whenever

that distance  $2^{k} + 1$  count the conclusion counters are the 4 and 5.

We now calcu example. For counter value: is shown in F summing cum Figure 6B. O Figure 6B agre

To find the ac-C, we take  $F_1$ pages,  $F_1 = F($ 0.50, and the  $0.50T_2$ .

Note that F(c)of C for LRU summation as  $(L - \gamma_L)/L$ in the backing

To avoid con an iterative co every time t, th to their most is  $s_i(1)$  since  $s_i$ is  $s_i(2)$ , and  $s_i($

Let us suppos appears at pos must be the tor page. Consider  $1 \le j < \Delta$ . At page, and the in is added to this on stack S<sub>i</sub>. If j at time t, sin changed from t

The net effect of is moved to th down-shifted o position. If  $x_i$ on the top and a shown in Figure

No. 2 · 1970

IBM SYST J

5

Control of the second of the s

that distance occurs. For k-bit page numbers, we need at most  $2^k + 1$  counters, corresponding to  $1 \le \Delta \le 2^k$  and  $\Delta = \infty$ . At the conclusion of a page trace, the final values of the distance counters are the values  $\{n(\Delta)\}$ , and F(C) is obtained from Equations 4 and 5.

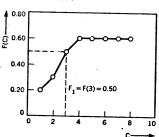

We now calculate the value of the success function in a numerical example. For  $\Delta$ 's of 1, 2, 3, 4, and  $\infty$ , the corresponding final counter values in Figure 5 are 2, 1, 2, 1, and 4. This distribution is shown in Figure 6A. Dividing by L equals 10 in Figure 5, and summing cumulatively, we obtain the success function shown in Figure 6B. One can verify that the F(C) values for the curve in Figure 6B agree with those obtained in the simulations of Figure 4.

To find the access frequencies  $F_1$  and  $F_2$ , for a given buffer capacity C, we take  $F_1 = F(C_1)$  and  $F_2 = 1 - F_1$ . As an example, for C = 3 pages,  $F_1 = F(3) = 0.50$  as indicated in Figure 6B,  $F_2 = 1 - 0.50 = 0.50$ , and the average access time  $\overline{T}$  of the hierarchy is  $0.50T_1 + 0.50T_2$ .

Note that F(C) is always a monotonic, non-decreasing function of C for LRU replacement, since F(C) is obtained by cumulative summation as shown in Equation 4. Also, F(C) never exceeds  $(L - \gamma_L)/L$  for any capacity, because all pages initially reside in the backing store.

To avoid constructing each LRU stack separately, we now give an iterative construction of  $S_t$  from  $S_{t-1}$  and  $x_t$ . Observe that at every time t, the stack  $S_t$  is simply the list of pages in  $\Gamma_t$ , according to their most recent reference. The most recently referenced page is  $s_t(1)$  since  $s_t(1) = x_t$ . The second most recently referenced page is  $s_t(2)$ , and  $s_t(\gamma_t)$  is the least recently referenced page in  $\Gamma_t$ .

Let us suppose that page  $x_i$  has been previously referenced and appears at position  $\Delta$  on stack  $S_{i-1}$ . For time t, we know that  $x_i$  must be the top entry in  $S_i$ , because it is the most recently referenced page. Consider now a page b at some position j on  $S_{i-1}$  where  $1 \leq j < \Delta$ . At time t-1, page b is the jth most recently referenced page, and the intervening pages do not include  $x_i$ . At time t, page  $x_i$  is added to this set so that page b must now be at position j+1 on stack  $S_i$ . If j is greater than  $\Delta$ , page b must remain at position j at time t, since the set of more recently referenced pages is unchanged from time t-1.

The net effect of this page motion is shown in Figure 7A. Page  $x_t$  is moved to the top of the stack, pages previously above  $x_t$  are down-shifted one position, and all other pages retain the same position. If  $x_t$  were not previously referenced,  $x_t$  would be placed on the top and all other pages would be down-shifted one position as shown in Figure 7B.

numerical example

Figure 7 Constructing LRU stacks

87

essentially

ictions are he critical  $\Delta_i$  is set xample is

tly to the times the the stack s that the

(4)

(5)

f distance nitially to whenever

IBM SYST J

No. 2 - 1970

STORAGE HIERARCHY EVALUATION

This iterative procedure can be used to generate the sequence of stacks in Figure 5. In an actual evaluation, it is not necessary to store the entire sequence of stacks. Rather, only the current stack must be maintained as the trace is scanned. When a page reference occurs, that page is put on the top of the stack, and entries in the stack are down-shifted one-by-one starting from the top. If page  $x_i$  is encountered, its distance  $\Delta_i$  is recorded, and  $x_i$  is erased because it has already been placed on top. The position vacated by  $x_i$  is filled by the page downshifted from position  $\Delta_i - 1$ . If  $x_i$  is not encountered, then the downshifting proceeds to the bottom of the stack, and distance  $\Delta_i = \infty$  is recorded.

# Stack algorithms

We now examine the general class of replacement algorithms that satisfy the inclusion property. Such algorithms are called "stack algorithms." It is shown that stacks can be iteratively maintained for any stack algorithm, and that stack distance frequencies for a given trace can be used to obtain the corresponding success function. The main problems considered are (1) to efficiently generate stacks  $\{S_i\}$  for an arbitrary stack algorithm, and (2) to identify those algorithms that are stack algorithms. Several examples of stack algorithms are described, along with one replacement algorithm that is not a stack algorithm.

A replacement algorithm is called a stack algorithm if the buffer contents in a demand-paged, two-level hierarchy satisfy the inclusion property given in Equation 1, for every page trace and every point in time. As shown for LRU replacement, a stack can be defined according to Equation 2 in such a way that the buffer contents for all capacities are given by Equation 3. Furthermore, since the stack distance  $\Delta_i$  is a critical capacity, the success function for any page trace can be obtained by summing the stack distance frequencies  $\{n(\Delta)\}$  according to Equation 4. This summation implies that the success function is a monotonic and nondecreasing function of the capacity C for every stack algorithm.

stack generation

88

Let us now consider a replacement algorithm R as a collection of mappings

$$R_c: B_{t-1}(C) \to y_t(C)$$

where  $y_t(C) \in B_{t-1}(C)$

is the page replaced by  $x_i$  in a buffer of capacity C. From the constraints of demand paging, we know that R is applied only when the following conditions are true:  $x_i \in B_{t-1}(C)$  and  $|B_{t-1}(C)| = C$ . If the inclusion property is satisfied up to and including time t-1, then R must satisfy certain restrictions at time t to maintain the inclusion property. Specifically, if a replacement is required for some capacity C+1 (and therefore for C), then  $y_i(C+1)$  must be either  $y_i(C)$  or  $s_{t-1}(C+1)$ . To prove this, let us assume the following:

MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

$B_{i-1}(C)\subset$

$|B_{t-1}(C)| =$

$|B_{t-1}(C +$

and

$x_i \notin B_{i-1}(C$

Note that  $B_{t-1}(C + s_{t-1}(C+1))$  However, p would viola

We have g same condiy<sub>t</sub>(C) or  $s_{t-}$  we concludand only if

$y_i(C+1) =$  for

$1 \leq C < \gamma$

Important r that induce use this ord be represent

$P_t = p_t(1),$

where  $p_t(i)$  l algorithm the lowest p

A convenien A is an arbit in A having and  $x_t \notin B$   $y_t(C+1)$  a

$y_i(C) = \min$

and

$y_i(C+1) =$

ON

sequence of necessary to current stack age reference entries in the top. If page ased because ted by  $x_i$  is If  $x_i$  is not of the

orithms that alled "stack maintained encies for a ess function. herate stacks entify those les of stack at algorithm

f the buffer isfy the ince and every n be defined contents for ce the stack or any page frequencies lies that the function of

ollection of

om the conly when the = C. If the t-1, then he inclusion me capacity either  $y_i(C)$  ng:

IBM SYST J

$$B_{t-1}(C) \subset B_{t-1}(C+1)$$

$$|B_{t-1}(C)| = C$$

$$|B_{t-1}(C+1)| = C+1$$

and

$$x_i \notin B_{i-1}(C+1)$$

Note that from Equation 2, page  $s_{t-1}(C+1)$  is contained in  $B_{t-1}(C+1)$  but not in  $B_{t-1}(C)$ . If page  $y_t(C+1)$  is neither  $s_{t-1}(C+1)$  nor  $y_t(C)$ , then  $y_t(C+1)$  is some other page  $z \in B_{t-1}(C)$ . However, page z is included in  $B_t(C)$ , but not in  $B_t(C+1)$ , which would violate the inclusion property.

We have given a necessary condition for stack algorithms. The same condition is also sufficient, because if  $y_i(C+1)$  is either  $y_i(C)$  or  $s_{i-1}(C+1)$ , then  $B_i(C)$  is a subset of  $B_i(C+1)$ . Therefore, we conclude that a replacement algorithm is a stack algorithm if and only if for every time t

$$y_i(C+1) = s_{i-1}(C+1)$$

or  $y_i(C+1) = y_i(C)$  (6)

for

$$1 \le C < \gamma_{t-1}$$

and  $C+1 < \Delta_t$

Important replacement algorithms that satisfy Equation 6 are those that induce a total ordering on all previously referenced pages and use this ordering to make replacement decisions. The ordering can be represented in the form of a *priority list*

$$P_t = p_t(1), p_t(2), \cdots, p_t(\gamma_{t-1})$$

where  $p_i(i)$  has a higher priority than  $p_i(i+1)$  for  $1 \le i < \gamma_{i-1}$ . The algorithm then selects for replacement the page in  $B_{i-1}(C)$  that has the lowest priority.

A convenient notation for working with priorities is  $\min(A)$ , where A is an arbitrary set of pages in  $\Gamma_{t-1}$ , and  $\min(A)$  is the unique page in A having lowest priority on the list  $P_t$ . If  $B_{t-1}(C) \subset B_{t-1}(C+1)$  and  $x_t \notin B_{t-1}(C+1)$ , we can express the replaced pages  $y_t(C)$  and  $y_t(C+1)$  as follow:

$$y_t(C) = \min [B_{t-1}(C)]$$

(7)

and

$$y_t(C+1) = \min [B_{t-1}(C+1)]$$

(8)

$$= \min \left[ B_{t-1}(C), s_{t-1}(C+1) \right] \tag{9}$$

$$= \min\{\min\{B_{t-1}(C)\}, s_{t-1}(C+1)\}$$

(10)

$$= \min [y_t(C), s_{t-1}(C+1)]$$

(11)

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

89

stack

algorithm

identification

Equations 7-9 are based on the definition of the replacement algorithm, whereas Equation 10 is based on the properties of minimization.

We conclude from Equation 11 that any replacement algorithm that induces a priority list P, for every time t satisfies Equation 6 and is therefore a stack algorithm. For example, the priority list for LRU is just the ordering of pages in  $\Gamma_{t-1}$  by most recent reference. The priority list for "least frequently used" (LFU) replacement is the ordering of referenced pages by most frequent reference together with a scheme to break ties.

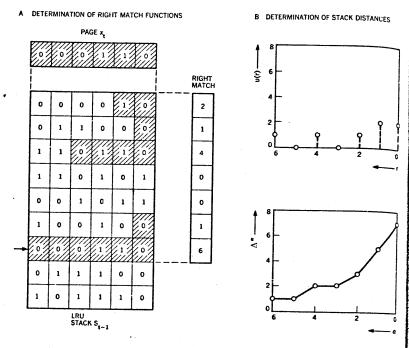

stack updating Before describing other examples of stack algorithms, let us develop a stack updating procedure for algorithms inducing a priority list. For any page trace  $X = x_1, x_2, \dots, x_L$  and any time t, where  $1 \le t \le L$ , suppose that stack  $S_{t-1}$  is available. Also, for any two pages  $a, b \in \Gamma_{t-1}$ , let max (a, b) denote the page having higher priority. If  $x_t$  has been previously referenced and appears at position  $\Delta_t$  on stack  $S_{t-1}$ , the stack at time t is given by

$$s_i(1) = x_i \tag{12}$$

$$s_i(i) = \max[y_i(i-1), s_{i-1}(i)] \quad \text{for } 2 \le i < \Delta_i$$

(13)

$$s_t(\Delta_t) = y_t(\Delta_t - 1) \tag{14}$$

$$s_i(i) = s_{i-1}(i) \quad \text{for } \Delta_i < i \le \gamma_{i-1}$$

(15)

Equations 12, 14, and 15 are based on the constraints of demand paging, whereas Equation 13 is derived from Equation 11.

If  $x_i$  has not been previously referenced, the defining equations for stack  $S_i$  are the following:

$$s_t(1) = x_t \tag{16}$$

$$s_i(i) = \max[y_i(i-1), s_{i-1}(i)] \quad \text{for } 2 \le i \le \gamma_{i-1}$$

(17)

$$s_t(\gamma_t) = y_t(\gamma_{t-1}) \tag{18}$$

In this case, Equations 16 and 17 express the fact that replacements are required for all buffer capacities in the range  $1 \le C \le \gamma_{t-1}$ . Equation 18 corresponds to the new page  $x_t$  being added to the stack, with the result that a buffer of capacity

$$\gamma_i = \gamma_{i-1} + 1$$

is now full.

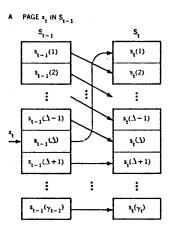

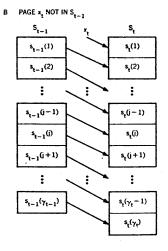

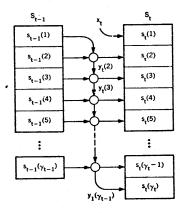

Figure 8 illustrates the stack updating procedure as given in Equations 12–18. The top entry  $s_i(1)$  is always  $x_i$ , and the first page replaced is

$$y_i(1) = s_{i-1}(1) \quad \text{for } \Delta_i > 1$$

90 MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

Figure 8 S

A PAGE X<sub>t</sub> IN S

s<sub>t-1</sub>(2 s<sub>t-1</sub>(2)

s<sub>t-1</sub>(4)

$\begin{array}{c} s_{t-1}(\Delta_t - \\ \\ s_{t-1}(\Delta_t) \\ \\ s_{t-1}(\Delta_t + \\ \end{array}$

$s_{t-1}(\gamma_{t-1})$

Each substantial  $s_{t-1}(i)$  and on stack i determine i If  $x_t$  is not i and we use does not i Only a seq  $y_t(i-1)$  is

Comparing shown in F  $s_{i-1}(C)$ . In since both reference. T

$y_t(C) = s_{t-1}$ and Equatio

$s_i(i) = \max[$

$\cdot = s_{t-1}(i)$

For an arbitr than for LRU very differen

Let us now example any replacent usage quantity priority list a

eplacement operties of

algorithm Equation 6 priority list t reference, ment is the ce together

us develop riority list. e t, where or any two ing higher at position

(12)

(13)

(14)

(15)

of demand 1.

nations for

-

(16)

(17)

(18)

placements  $C \leq \gamma_{i-1}$ . led to the

in Equafirst page

IBM SYST J

Figure 8 Stack updating

A PAGE X, IN STACK S, \_ T

B PAGE X NOT IN STACK S t-1

Each subsequent entry  $s_t(i)$  is then determined iteratively from  $s_{t-1}(i)$  and  $y_t(i-1)$  according to Equation 13 or 17. If  $x_t$  is found on stack  $S_{t-1}$  as shown in Figure 8A, we use Equation 14 to determine  $s_t(\Delta_t)$ . All lower entries are unchanged from time t-1. If  $x_t$  is not found on stack  $S_{t-1}$ , as shown in Figure 8B, then  $\Delta_t = \infty$ , and we use Equation 18. In either case, the replacement algorithm does not have to be applied to all the pages for stack updating. Only a sequence of pairwise decisions between pages  $s_{t-1}(i)$  and  $y_t(i-1)$  is required.

Comparing our stack updating procedure with the one for LRU shown in Figure 7, we see that page  $y_i(C)$  under LRU is always  $s_{i-1}(C)$ . In fact, the priority list  $P_i$  is exactly equal to stack  $S_{i-1}$ , since both lists give the order of pages in  $\Gamma_{i-1}$  by most recent reference. Thus

$$y_i(C) = s_{i-1}(C)$$

and Equations 13 and 17 then reduce to

$$s_t(i) = \max[s_{t-1}(i-1), s_{t-1}(i)]$$

=  $s_{t-1}(i-1)$

For an arbitrary stack algorithm, the stack updating is more complex than for LRU, and the order of stack elements at time t-1 may be very different from that at time t.

Let us now examine several examples of stack algorithms. In general any replacement algorithm that bases its decisions on some page usage quantity, whether measured or predicted, naturally induces a priority list and is, therefore, a stack algorithm. One example, of

examples of stack algorithms

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

course, is LRU, and another example previously mentioned is least frequently used (LFU) replacement.

Under LFU, the page replaced from a buffer at time t is that page that has been referenced the fewest number of times over the interval  $1 \le \tau \le t$ , or perhaps over some "backward window" interval  $t - h \le \tau \le t$ , where  $0 < h \le t$ . If two or more pages are tied for least frequency of use, then some arbitrary rule is used to break the tie. As long as the rule is consistent for all pages and all capacities (e.g., if the tied pages are numerically ordered) a priority list  $P_t$  is induced, and LFU is a stack algorithm.

Other examples of stack algorithms may arise in analytical studies of program behavior. If an address trace is generated from some random process, it may be desirable to study the behavior of replacement algorithms that base their decisions on the parameters of the random process. One such process is a time-invariant, first-order Markov chain, 15,16 where any page c is referenced immediately after page b with a fixed transition probability  $\pi_{bc}$ The process is completely described by the matrix  $\Pi = \{\pi_{bc}\}\$ , (where b and c range over all referenced pages) and by the page referenced at time t = 1.

One possible replacement algorithm is to remove the page least likely to be referenced next. We call this strategy "least transition probability" (LTP) since, for page  $x_i$  equal to page b, the page c chosen for removal is the one that minimizes  $\pi_{hc}$  over those pages in the buffer. Supplying an appropriate rule for breaking ties, we see that LTP induces a priority list and is a stack algorithm.

Another replacement algorithm is to remove the page with the largest expected time until next reference. We call this strategy LNR for "longest next reference." The expected times until next reference can be obtained from the II-matrix by standard techniques.<sup>17</sup> As with LTP, LNR induces a priority list if we supply an appropriate tie-breaking rule.

To analyze an actual program trace under LTP or LNR (perhaps for testing a Markov model of the program), page reference statistics may be used to estimate the matrix II. For example, the observed transition frequencies over some interval t - h to t can be used to generate a time-varying estimator matrix  $\hat{\Pi}_t$ . A priority list  $P_t$  can then be constructed for each time t, according to the probabilities in  $\hat{\Pi}_t$ , with the result that the overall strategy for replacement remains a stack algorithm.

Other stack algorithms may base their decisions on information from the programmer or compiler, or on properties of the computer system. For example, the programmer or compiler may supply to the system<sup>14</sup> special "program directives" that indicate which pages should be g case is wher pages in a m of the progra can be order replacement

In the exam variety of wa "first-in/first FIFO, the pa (continuous)

A peculiarity X = abcd

As shown in monotonic, a algorithms ha is not a stac! every time t. priorities bety C. Thus in t priority of all longest. How brought into

Whenever th the buffer, w every capacit the frequency Another case buffer.

As long as as one can c then stack-pr function.

### An optimum

We now discu value for the algorithms-fo an algorithm Belady<sup>13</sup> desc MIN, and sho page trace and we describe a

No. 2 · 1970

IBM SYST J

entioned is

s that page he interval v" interval are tied for d to break es and all ) a priority

cal studies rom some chavior of he paramme-invarireferenced bility  $\pi_{bc}$ , the page

page least transition he page coose pages ig ties, we hm.

with the s strategy until next ard techsupply an

erhaps for statistics observed be used to ist  $P_i$  can obabilities placement

computer supply to tich pages

IBM SYST J

should be given high priorities in the immediate future. Another case is where the operating system assigns priorities to program pages in a multiprogrammed system, based perhaps on the position of the program in a task queue. If all the pages in the address space can be ordered in a priority list  $P_t$  for each time t, the resulting replacement algorithm is a stack algorithm.

In the examples given, we see that priority lists can arise in a variety of ways. We now consider a replacement algorithm called "first-in/first-out" (FIFO) that is not a stack algorithm. Under FIFO, the page that has remained in the buffer for the longest (continuous) time up to time t is removed.

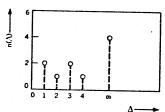

A peculiarity of FIFO is illustrated by the following page trace

X = abcdabeabcde

As shown in Reference 18, the success function for this trace is not monotonic, and takes the form shown in Figure 9. Since stack algorithms have monotonic success functions, we conclude that FIFO is not a stack algorithm and does not induce a priority list  $P_t$  at every time t. In amplifying this conclusion, we note that the relative priorities between pages in  $\Gamma_{t-1}$  may depend on the buffer capacity C. Thus in the example, one can verify that page d has lowest priority of all pages in  $B_o(3)$  in the sense that d has been in the buffer longest. However, page d has highest priority in  $B_o(4)$ , since it was brought into the buffer latest.

Whenever the priorities among pages depend on the capacity of the buffer, we cannot define a single priority list that applies to every capacity. One instance of this is when priorities depend on the frequency of reference to pages after their entering the buffer. Another case is when priorities depend on total time spent in the buffer.

As long as priorities are independent of capacity, and as long as one can order the referenced pages to reflect these priorities, then stack-processing techniques can be used to find the success function.

# An optimum replacement algorithm

We now discuss a replacement algorithm that yields the maximum value for the success frequency over the space of all replacement algorithms—for every page trace and every buffer capacity. Such an algorithm is said to be an *optimum replacement algorithm*. Belady<sup>13</sup> describes an optimum replacement algorithm called MIN, and shows how to evaluate the success frequency for a given page trace and a given buffer capacity. In the following discussion, we describe a stack algorithm called OPT and prove that it is also

first-in/ first-out

Figure 9 Success function for FIFO replacement

No. 2 - 1970

STORAGE HIERARCHY EVALUATION

an optimum replacement algorithm. Using certain properties of  $L_{RU}$  and OPT, the entire success function for OPT can be determined  $\rm i_{\rm fl}$  two passes of a page trace.

OPT

Figure 10 Example of OPT replacement

|                               |   |   |   | _ |   |   |   |   |   |    |

|-------------------------------|---|---|---|---|---|---|---|---|---|----|

| TIME                          | į | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| PAGE TRACE                    | а | b | c | a | d | b | а | d | С | d  |

| BUFFER<br>CONTENTS<br>FOR C=3 | a | a | а | a | а | a | а | a | a | a  |

|                               |   | ь | b | b | þ | b | b | b | С | С  |

|                               |   |   | c | c | đ | đ | ď | đ | đ | đ  |

|                               |   |   |   | • |   | • | • | • |   | •  |

The replacement algorithm OPT has the following characteristics. Whenever a page must be pushed from the buffer, the chosen page is the one whose next reference is farthest in the future. If a tie results because two or more buffer pages are never referenced again, the tie is broken by an arbitrary rule  $\Omega$  that pushes the page with the latest alphabetical or numerical order. An example of OPT replacement is shown in Figure 10, for the buffer capacity C=3. As an illustration, notice that at time t=5 page c is pushed from the buffer, since the other buffer pages a and b are referenced sooner. At time t=9, page b is pushed from the buffer, because page d is referenced again (at time t=10), and page a has priority over page b by our rule a.

A formal proof that OPT is an optimal replacement algorithm is given in the Appendix. We note here that OPT is not realizable in an actual computer system because it requires knowledge of future page references. However, OPT does serve as a useful benchmark for any replacement algorithm, including stack-type algorithms. To show that OPT is a stack algorithm, observe that a priority list  $P_t$  can be constructed for OPT at each time t. Specifically,  $P_t$  is the list of the pages referenced again, ordered by their time of next reference, followed by the list of the pages not referenced again, as ordered by the tie-breaking rule  $\Omega$ .

stack processing example The stack processing technique for OPT is illustrated in Figure 11. Priority lists are ordered as described above, and curly brackets denote the pages ordered under the rule  $\Omega$ . For example, at time t=8 the priority list is  $P_8=c,d,a,b$ , because c is the next page

Figure 11 Stack processing and success function for OPT replacement

| 1 | 2 | 3   | 4                 | 5                                   | 6                                                         | 7                                                                                        | 8                                                                                                | 9                                                                                                        | 10                                                                                                                               |

|---|---|-----|-------------------|-------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| a | b | c   | a                 | đ                                   | b                                                         | a                                                                                        | đ                                                                                                | С                                                                                                        | ď                                                                                                                                |

|   | a | •   | ь                 | Ь                                   |                                                           | ď                                                                                        | c                                                                                                | đ                                                                                                        | <u>(°</u>                                                                                                                        |

|   | ь | b   | a                 | a                                   | d                                                         | c                                                                                        | đ                                                                                                | ( •                                                                                                      | Jb                                                                                                                               |

|   |   | c   | c                 | đ                                   |                                                           | , ,                                                                                      | ه و                                                                                              | ₹ь′                                                                                                      | ٦                                                                                                                                |

|   |   |     |                   | c «                                 | ( b '                                                     | <b>ξ</b> υ'                                                                              | þ                                                                                                | Į.                                                                                                       | þ                                                                                                                                |

| a | ь | ċ   | 2                 | đ                                   | b                                                         |                                                                                          | d                                                                                                | С                                                                                                        | ď                                                                                                                                |

|   | * | 3   | c                 |                                     | а                                                         | ь                                                                                        | •                                                                                                | đ                                                                                                        | c                                                                                                                                |

|   |   | b   | b                 | ь                                   | d                                                         | d                                                                                        | b                                                                                                | a                                                                                                        | a                                                                                                                                |

|   |   |     |                   | Ċ                                   | c                                                         | c                                                                                        | c                                                                                                | b                                                                                                        | b                                                                                                                                |

|   |   |     | 2                 |                                     | . 3                                                       | 2                                                                                        | 3                                                                                                | 4                                                                                                        |                                                                                                                                  |

|   | a | a b | a b c a a a b b c | a b c a a a b b a c c a b c a a c c | a b c a d a a b b b a a c c d c c a b c a d a a c a b b b | a b c a d b  a a a b b a b b a c c d c c b  a b c a d b  a b c a d b  a a c a a  b b b d | a b c a d b a  a a a b b a d  b b a a d c  c c d c a b  b  a b c a d b a  a a c a a b  b b b d d | a b c a d b a d  a a a b b a d c b b a a d c d c c d c a b b  a b c a d b a d  a a c a a b a b b b d d b | a b c a d b a d c  a a a b b a d c d  b b a a d c d  c c d c a a b b  c b b c  a b c a d b a d c  a a c a a b a d  b b b d d b a |

MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

referenced Pages a and ing to rule priority lis distance fr amount of

Fortunately priority list  $w_i(a)$  to a p in  $x_{i+1}$ , ... t). If page a as infinity, pages in  $\Gamma$  illustrative Figure 12.

If the forward the new form the set  $a \neq x_t$  and  $w_t(a) = \begin{cases} w \\ 0 \end{cases}$

To determine trace X, consuppose the that  $x_i$  and reverse trace. At time j, referenced in However, the distance  $w_i$  distances for of the sequentrace X.

These results for determine technique is scan of the left-pointing order, on a using OPT Forward disting the OPT pri

The LRU sta important in

No. 2 - 1970

erties of LRU etermined in

aracteristics. chosen page are. If a tie enced again, e page with ple of OPT city C = 3, sushed from aced sooner, se page d is riority over

algorithm is ealizable in ge of future benchmark algorithms. priority list y,  $P_t$  is the me of next ed again, as

Figure 11. ly brackets sle, at time a next page

IBM SYST J

No. 2 · 1970

referenced (at t=9) and d is the second page referenced (at t=10). Pages a and b are not referenced again, and thus are ordered according to rule  $\Omega$ . The sequence of OPT stacks is constructed using the priority lists, and the success function is obtained from the stack distance frequencies. A major difficulty with the technique is the amount of forward scanning required to construct the priority lists.

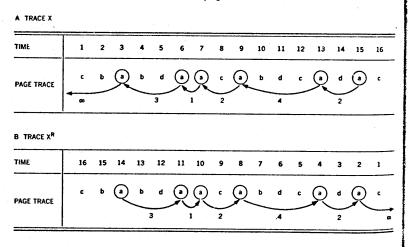

Fortunately, a more efficient procedure exists for obtaining the priority lists. For a given page trace X, we define the forward distance  $w_t(a)$  to a page a at time t as the number of distinct pages referenced in  $x_{t+1}, \dots, x_{t'}$ , (where  $x_t$  is the first reference to page a after time t). If page a is not referenced again, the forward distance is defined as infinity. Note that the priority list under OPT is a listing of the pages in  $\Gamma_{t-1}$  according to their increasing forward distances. An illustrative example of forward distance determination is given in Figure 12.

If the forward distances to all pages in  $\Gamma_{t-1}$  are known at time t-1, the new forward distances at time t can be determined iteratively from the single forward distance  $w_t(x_t)$ . Specifically, for page  $a \neq x_t$  and  $w_t \triangleq w_t(x_t)$ , we have

$$w_{t}(a) = \begin{cases} w_{t-1}(a) - 1 & \text{for } w_{t-1}(a) \leq w_{t} \text{ and } w_{t-1}(a) \neq \infty \\ w_{t-1}(a) & \text{for } w_{t-1}(a) > w_{t} \text{ or } w_{t-1}(a) = \infty \end{cases}$$

$$(19)$$

To determine the sequence of forward distances  $\{w_i\}$  for a page trace X, consider the reverse trace  $X^R = x_L, x_{L-1}, \dots, x_2, x_1$ . Suppose that  $X^R$  is analyzed according to LRU replacement and that  $x_i$  and  $x_j$  denote two successive references to page a in the reverse trace. Thus  $X^R = x_L, \dots, x_i = a, \dots, x_j = a, \dots, x_1$ . At time j, the stack distance  $\Delta_j$  is the number of distinct pages referenced in  $x_1, \dots, x_{j+1}$ . (Note that  $x_{j+1}$  precedes  $x_j$  in  $X^R$ .) However, this number of distinct pages is precisely the forward distance  $w_j$  for page trace X. Thus the sequence of LRU stack distances for trace  $X^R$ , namely,  $\Delta_L$ ,  $\Delta_{L-1}$ ,  $\ldots$ ,  $\Delta_2$ ,  $\Delta_1$ , is the reverse of the sequence of forward distances  $w_1, w_2, \dots, w_{L-1}, w_L$  for trace X.

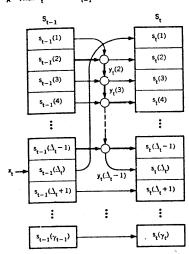

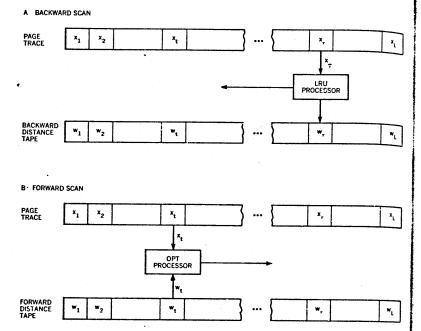

These results form the basis of a two-pass stack processing technique for determining the success function for OPT replacement. The technique is illustrated by Figure 13. The first pass is a backward scan of the page trace X using LRU replacement, denoted by the left-pointing arrow. The LRU stack distances are stored, in reverse order, on a "distance tape." The second pass is a forward scan using OPT replacement, as shown by the right-pointing arrow. Forward distances read from the distance tape are used to maintain the OPT priority lists according to Equation 19.

The LRU stack distances gathered from the reverse page trace yield important information about the forward page trace. Specifically,

forward distance

Figure 12 Determination of forward distances at time t = 4

maximum success function

S

Figure 13 Two-pass technique for LRU and OPT replacement

Sequence of LRU distances for page a

we claim that the success function for the reverse trace  $X^R$  under LRU replacement is equal to the success function for the forward trace X under LRU replacement. Thus one can use the backward scan of X, not only to generate the distance tape for OPT, but also to generate the success function for LRU.

To prove this result, let  $F_{LRU}(C, X)$  denote the LRU success function for trace X, and consider the set of LRU stack distances measured for a given page a in X and  $X^R$ . As the example in Figure 14 illustrates, these sets are always identical. Since this holds for every

distinct page identical, so are equal.

Another resu is equal to  $F_{\alpha}$ for trace X. forward-back During the fi the distance function for

#### Random re

In the stack tion is associ techniques to that does no if the buffer ! ment with a perform a N obtain a RAl yield a set of sample succes success funct

A question t generate a sai that bases a variable. We there certain! property fails

Our approacl stack algoriti each capacity time t, the pr of pages in likely to be c induces a price

To establish that a replace Since  $y_i(C) =$ bility that any

One difficulty priority list P. actually const

No. 2 · 1970

IBM SYST J

distinct page in the trace, the distance frequencies for X and  $X^R$  are identical, so that the success functions  $F_{LRU}(C, X^R)$  and  $F_{LRU}(C, X)$  are equal.

Another result, which is proved in the Appendix, is that  $F_{OPT}(C, X)$  is equal to  $F_{OPT}(C, X^R)$ , where  $F_{OPT}(C, X)$  is the OPT success function for trace X. Thus, our two-pass technique can be implemented with forward-backward scans as well as with backward-forward scans. During the first scan, the success function for LRU is obtained, and the distance tape generated. During the second scan the success function for OPT is obtained.

# Random replacement

x,

w<sub>L</sub>

x,

w<sub>L</sub>

In the stack algorithms considered thus far, a unique success function is associated with each trace. We now extend stack-processing techniques to cover a "random replacement" algorithm (RAND) that does not always yield a unique success function. With RAND, if the buffer has a capacity of C, any given page is chosen for replacement with a probability of 1/C. In analyzing RAND, one might perform a Monte Carlo simulation for each buffer capacity to obtain a RAND success function. Repeating these simulations would yield a set of sample success functions to characterize RAND. The sample success functions could then be used to estimate an "average" success function.

A question that arises is whether stack processing can be used to generate a sample success function for RAND or any other algorithm that bases a replacement choice on the value of some random variable. We observe that RAND is not a stack algorithm, because there certainly exists a trace and a time t for which the inclusion property fails to hold with a nonzero probability.

Our approach is to define a replacement algorithm RR, which is a stack algorithm having the same statistical properties as RAND for each capacity C. The algorithm RR is defined as follows: at each time t, the priority list  $P_t$  is obtained by randomly ordering the set of pages in  $\Gamma_{t-1}$  (each of the  $\gamma_{t-1}$ ! possible orderings is equally likely to be chosen). Observe that RR is a stack algorithm, since it induces a priority list.

To establish that RR is statistically equivalent to RAND, assume that a replacement is necessary in a buffer of capacity C at time t. Since  $y_i(C) = \min [B_{i-1}(C)]$ , and  $P_i$  is randomly chosen, the probability that any given page is  $y_i(C)$  is 1/C—the same as for RAND.

One difficulty in implementing RR is the generation of the random priority list  $P_t$ . Fortunately, it is possible to update the stack without actually constructing the entire priority list. Assuming that  $\Delta_t > j$ ,

Figure 14

$X^R$  under

ne forward

backward

T, but also

ss function

s for every

IBM SYST J

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

let  $q_i(t)$  denote the probability that page  $s_{t-1}(j)$  has priority over page  $y_t(j-1)$  at time t. If  $s_{t-1}(j)$  does not have priority over  $y_t(j-1)$ , we know that  $s_{t-1}(j) = \min [B_{t-1}(j)]$ . Since this occurs with probability 1/j, we obtain

$$1 - q_i(t) = 1/i$$

or

$$q_i(t) = (j-1)/j \tag{20}$$

Using Equation 20, the stack can be updated at time t for RR replacement by choosing page  $s_i(j) = s_{i-1}(j)$  with probability (j-1)/j, for  $2 \le j < \Delta_t$  and  $j < \gamma_{i-1}$ . As a check, let us compute the probability Q that an arbitrary page b is pushed from a buffer of capacity C at time t. Assuming that page b occurs at some position k on stack  $S_{i-1}$  where  $1 \le k \le C$ , then Q is given by the following expression:

$$Q = P_r\{y_t(C) = b\}$$

$$= P_r\{s_t(k) = y_t(k-1), s_t(k+1) = s_{t-1}(k+1),$$

$$s_t(k+2) = s_{t-1}(k+2), \dots, s_t(C) = s_{t-1}(C)\}$$

(21)

The events in the joint probability in Equation 21 are independent, so that we obtain

$$Q = P_{r}\{s_{t}(k) = y_{t}(k-1)\} \cdot P_{r}\{s_{t}(k+1) = s_{t-1}(k+1)\}$$

$$\cdot P_{r}\{s_{t}(k+2) = s_{t-1}(k+2)\} \cdot \cdots \cdot P_{r}\{s_{t}(C) = s_{t-1}(C)\}$$

$$= \left(\frac{1}{k}\right) \left(\frac{k}{k+1}\right) \left(\frac{k+1}{k+2}\right) \cdot \cdots \cdot \left(\frac{C-1}{C}\right)$$

$$= \frac{1}{C}$$

Since Q=1/C holds for any page b and capacity C, we have verified that the stack updating for RR can be accomplished using Equation 20, and that RR has the same statistical properties as RAND for each buffer capacity. Note that although a particular value of a point on the success function, for example F(4)=0.3, is equally likely to occur under both RAND and RR, the occurrence of a particular success function is not equally likely.

As the example with RR illustrates, stack processing techniques can be extended to cover probabilistic replacement algorithms. In fact, a replacement algorithm can have a mixture of probabilistic and nonprobabilistic aspects. For instance, the arbitrary rule used to break ties in LFU and other algorithms may choose a page at random. Another possibility is for a replacement algorithm to favor some pages probabilistically in the construction of the priority list. thereby realizing a so-called "biased replacement" algorithm. <sup>12</sup> In any case, the only requirement is that the priority list be constructed

to reflect

# Congrue

Up to no hierarchie this type or referenced that all a that seldo mapping is that expages in treplaceme informati offset the employed only a su

One such the  $2^k$  disjoint ca  $2^{k-\alpha}$  pag  $2^{\alpha} - 1$ , a bits of the class called the the class for all pa

In a two-l class is as be used e the class buffer in may appereference occupied selects or replacement

Note that class, and C is a potential class for a fixe the mapper constrain

No. 2 · 19

IBM SYST J

1 1

iority over iority over this occurs

(20)

t for RR

probability

is compute

m a buffer

ne position

: following

dependent.

$= s_{i-1}(C)$

(21)

to reflect the probabilistic properties of the desired replacement algorithm for every capacity C.

# Congruence mapping

Up to now, we have restricted our attention to two-level storage hierarchies with unconstrainted mapping at the first level. Under this type of mapping, any page in the buffer may be replaced by the referenced page. The advantages of unconstrained mapping are that all available page frames in the buffer can be used, and also that seldom used pages cannot become "locked" into the buffer by mapping constraints. A disadvantage with unconstrained mapping is that extensive associative searches may be necessary to locate pages in the buffer. Moreover, the implementation overhead of the replacement algorithm may be excessive, since relative priority information must be maintained for all pages in the buffer. To offset these disadvantages, a constrained mapping scheme can be employed whereby each page is restricted to occupy a member of only a subset of the buffer page frames.

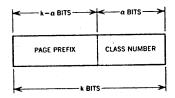

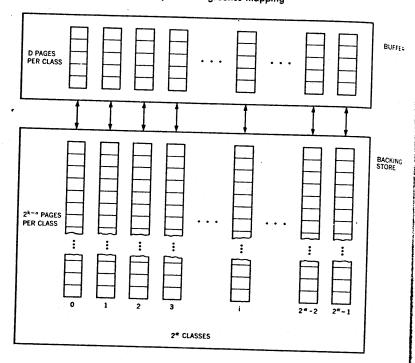

One such mapping technique is called *congruence mapping*, by which the  $2^k$  distinct pages in the address space are partitioned into  $2^{\alpha}$  disjoint *congruence classes*, where  $0 \le \alpha \le k$ , and each class contains  $2^{k-\alpha}$  pages. The classes are numbered consecutively from 0 to  $2^{\alpha} - 1$ , and class membership is determined from the  $\alpha$  low-order bits of the page number. In this case, the  $\alpha$  low-order bits constitute the *class number* [x] of a page, and the remaining  $k - \alpha$  bits are called the *page prefix* as shown in Figure 15. The quantity  $\alpha$  is called the *class length*. For a class length equal to zero, we set [x] = 0 for all pages.

In a two-level hierarchy with congruence mapping, every congruence class is assigned an equal number of page frames in the buffer—to be used exclusively by members of that class. This number is called the class capacity and is denoted by D. (The total capacity of the buffer in pages is thus  $C = 2^a \cdot D$ .) When a page x is referenced, it may appear in any of the D page frames reserved for class [x]. If the reference page is not in the buffer, and if the D page frames are all occupied by other members of class [x], a replacement algorithm selects one of these pages for removal. We assume that the same replacement algorithm is used separately for each of the classes.

Note that when the class length  $\alpha$  is zero, all pages are in the same class, and the mapping is unconstrained. When the buffer capacity C is a power of 2, and when  $C = 2^{\alpha}$ , only one page is allocated to each class, and the mapping function is fully constrained. Thus for a fixed buffer capacity  $C = 2^h$ , where  $0 \le h \le k$ , we can vary the mapping function from unconstrained to partially and fully constrained simply by varying the value of  $\alpha$  from 0 to h.

No. 2 · 1970

STORAGE HIERARCHY EVALUATION

Figure 15 Page number

shed using perties as particular 0.3, is recurrence

, we have

techniques rithms. In obabilistic rule used a page at n to favor iority list, ithm.<sup>12</sup> In onstructed

IBM SYST J

Figure 16 Two-level hierarchy with congruence mapping

Since the congruence classes are disjoint, and since the same number of buffer page frames are allocated to each class, it is possible to treat a buffer as a collection of  $2^a$  distinct buffers—one for each class [x]. If we also view the backing store as  $2^a$  individual backing stores, as shown in Figure 16, the two-level hierarchy partitions into a collection of  $2^a$  distinct subhierarchies, each with a buffer capacity of D page frames. When the replacement algorithm is a stack algorithm, these subhierarchies can be evaluated separately using stack processing techniques. In practice,  $2^a$  stacks (one for each subhierarchy) can be maintained as the trace is processed. Each page reference x causes only the stack for class [x] to be updated, and a stack distance  $\Delta$  to be determined from that stack.

In congruence mapping, to calculate the success function for a given trace and given class length  $\alpha$ , the stack distances must be carefully interpreted. Whenever a stack distance  $\Delta$  is measured, the corresponding critical capacity of the entire buffer is  $2^{\alpha} \cdot \Delta$ , since this is the minimum buffer capacity necessary to contain the referenced page. Therefore, the success function  $F^{\alpha}(C)$  for the set of capacities  $C = 2^{\alpha} \cdot D$  where  $D = 1, 2, \cdots$ , is given by

$$F^{\alpha}(C) = F^{\alpha}(2^{\alpha} \cdot D) = \sum_{\Delta=1}^{D} \frac{n(\Delta)}{L}$$

MATTSON, GECSEI, SLUTZ, AND TRAIGER

IBM SYST J

where  $n(\Delta)$  any of the