## **CS 268: Router Design**

Ion Stoica February 27, 2003

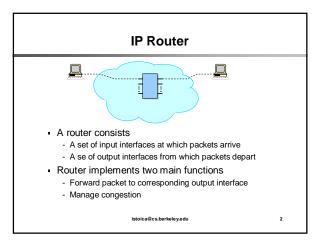

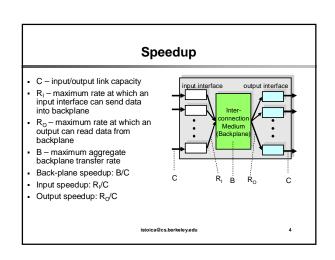

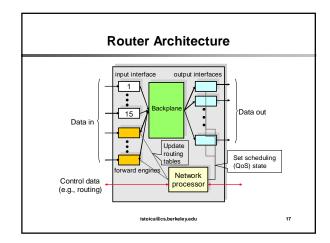

# Generic Router Architecture Input and output interfaces are connected through a backplane A backplane can be implemented by Shared memory Low capacity routers (e.g., PC-based routers) Shared bus Medium capacity routers Medium capacity routers

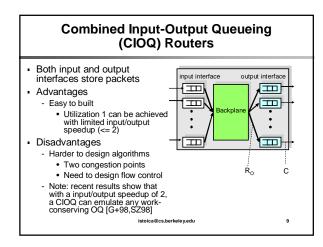

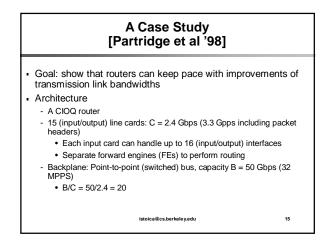

# Generic Architecture of a High Speed Router Today

- Combined Input-Output Queued Architecture

- Input/output speedup <= 2

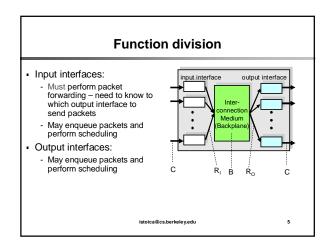

- Input interface

- Perform packet forwarding (and classification)

- Output interface

- Perform packet (classification and) scheduling

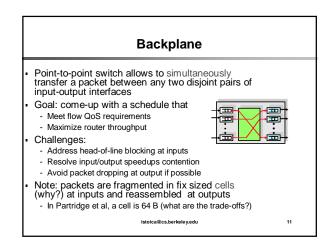

- Backplane

- Point-to-point (switched) bus; speedup N

- Schedule packet transfer from input to output

istoica@cs.berkeley.edu

10

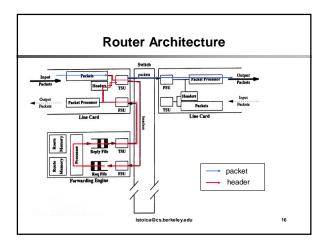

### **Router Architecture: Data Plane**

- Line cards

- Input processing: can handle input links up to 2.4 Gbps

- Output processing: use a 52 MHz FPGA; implements QoS

- Forward engine:

- 415-MHz DEC Alpha 21164 processor, three level cache to store recent routes

- Up to 12,000 routes in second level cache (96 kB); ~ 95% hit rate

- Entire routing table in tertiary cache (16 MB divided in two banks)

istoica@cs.berkeley.edu

ovedu

### **Router Architecture: Control Plane**

- Network processor: 233-MHz 21064 Alpha running NetBSD 1.1

- Update routing

- Manage link status

- Implement reservation

- Backplane Allocator: implemented by an FPGA

- Schedule transfers between input/output interfaces

istoica@cs.berkeley.edu

### **Data Plane Details: Checksum**

- Takes too much time to verify checksum

- Increases forwarding time by 21%

- Take an optimistic approach: just incrementally update it

- Safe operation: if checksum was correct it remains correct

- If checksum bad, it will be anyway caught by end-host

- Note: IPv6 does not include a header checksum anyway!

istoica@cs.berkeley.edu

# Data Plane Details: Slow Path Processing

- 1. Headers whose destination misses in the cache

- 2. Headers with errors

- 3. Headers with IP options

- 4. Datagrams that require fragmentation

- 5. Multicast datagrams

- Requires multicast routing which is based on source address and inbound link as well

- Requires multiple copies of header to be sent to

different line cords.

istoica@cs.berkeley.edu

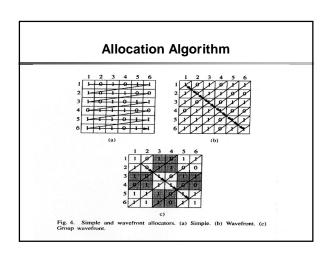

### **Control Plane: Backplane Allocator**

- Time divided in epochs

- An epoch consists of 16 ticks of data clock (8 allocation clocks)

- Transfer unit: 64 B (8 data clock ticks)

- During one epoch, up to 15 simultaneous transfers in an epoch

- One transfer: two transfer units (128 B of data + 176 auxiliary bits)

- Minimum of 4 epochs to schedule and complete a transfer but scheduling is pipelined.

- 1. Source card signals that it has data to send to the destination card

- 2. Switch allocator schedules transfer

- 3. Source and destination cards are notified and told to configure themselves

- 4. Transfer takes place

- Flow control through inhibit pins

istoica@cs.berkeley.edu

22

### The Switch Allocator Card

- Takes connection requests from function cards

- Takes inhibit requests from destination cards

- Computes a transfer configuration for each epoch

- 15X15 = 225 possible pairings with 15! Patterns

istoica@cs.berkeley.edu

### The Switch Allocator

- Disadvantages of the simple allocator

- Unfair: there is a preference for low-numbered sources

- Requires evaluating 225 positions per epoch, which is too fast for an FPGA

- Solution to unfairness problem: Random shuffling of sources and destinations

- Solution to timing problem: Parallel evaluation of multiple locations

- Priority to requests from forwarding engines over line cards to avoid header contention on line cards

istoica@cs.berkeley.edu

25

# Summary: Design Decisions (Innovations)

- Each FE has a complete set of the routing tables

- A switched fabric is used instead of the traditional shared bus

- 3. FEs are on boards distinct from the line cards

- 4. Use of an abstract link layer header

- 5. Include QoS processing in the router

istoica@cs.berkeley.edu

26

### **Check-Point Presentation (cont'd)**

- Next Tuesday (March 4) project presentations:

- Each group has 10 minutes

- 7 minutes for presentations

- 3 minutes for questions

- Time will be very strictly enforced

- Don't use more than five slides (including the title slide)

istoica@cs.berkeley.edu

### **Check-Point Presentation (cont'd)**

- 1st slide: Title

- 2<sup>nd</sup> slide: motivations and problem formulation

- Why is the problem important?

- What is challenging/hard about your problem

- 3<sup>rd</sup> slide: main idea of your solution

- 4<sup>th</sup> slide: status

- 5<sup>th</sup> slide: future plans and schedule

istoica@cs.berkeley.edu

28