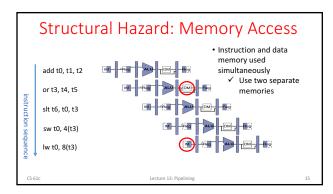

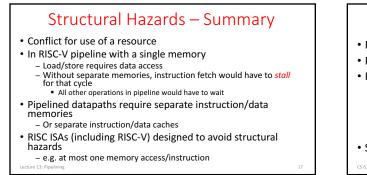

## Structural Hazard

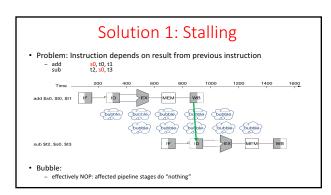

- **Problem:** Two or more instructions in the pipeline compete for access to a single physical resource

- **Solution 1:** Instructions take it in turns to use resource, some instructions have to stall

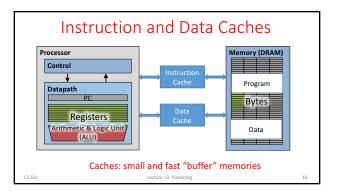

- Solution 2: Add more hardware to machine

- Can always solve a structural hazard by adding more hardware

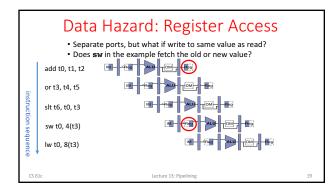

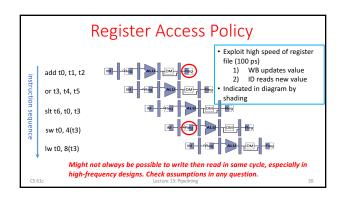

## **Regfile Structural Hazards**

- Each instruction:

- can read up to two operands in decode stage

can write one value in writeback stage

- Avoid structural hazard by having separate "ports"

two independent read ports and one independent write port

- Three accesses per cycle can happen simultaneously

18

11 cycles

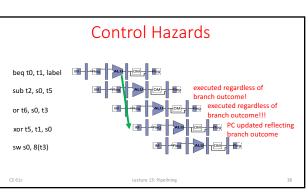

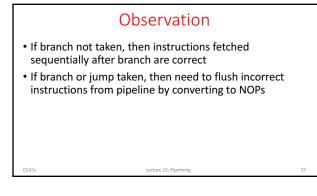

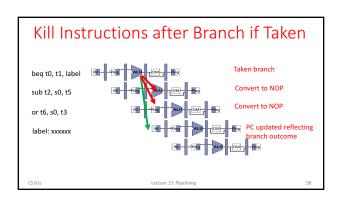

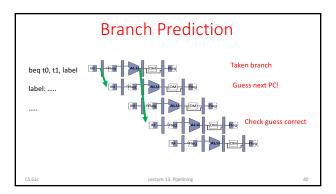

## Reducing Branch Penalties Every taken branch in simple pipeline costs 2 dead cycles To improve performance, use "branch prediction" to guess which way branch will go earlier in pipeline Only flush pipeline if branch prediction was incorrect

## In Conclusion

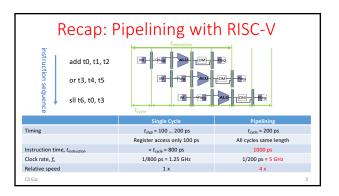

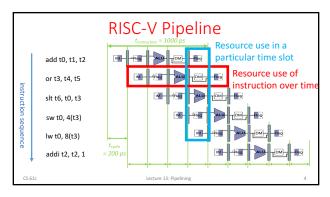

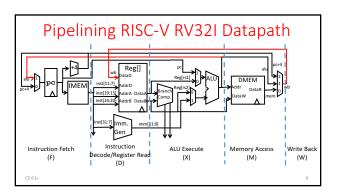

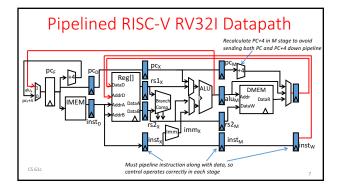

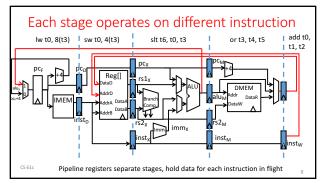

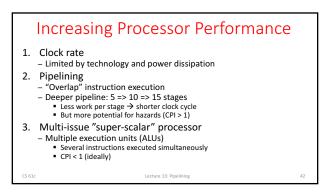

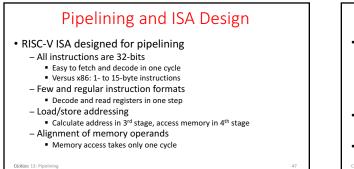

- Pipelining increases throughput by overlapping execution of multiple instructions

- All pipeline stages have same duration – Choose partition that accommodates this constraint

- Hazards potentially limit performance

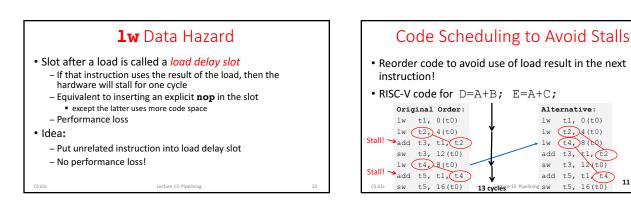

- Maximizing performance requires programmer/compiler assistance

E.g. Load and Branch delay slots

Lecture 13: Pipe

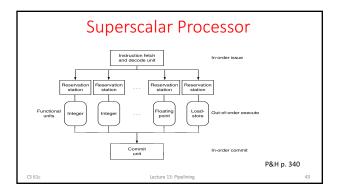

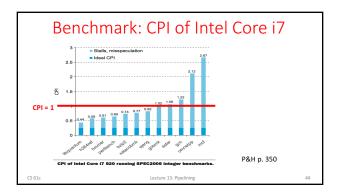

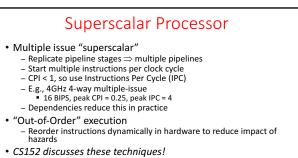

- Superscalar processors use multiple execution units for additional instruction level parallelism

- Performance benefit highly code dependent

- CS 61c

S 61c Lecture 13: Pipelining