Discussion 6: October 7, 2019

## 1 Boolean Logic

In digital electronics, it is often important to get certain outputs based on your inputs, as laid out by a truth table. Truth tables map directly to Boolean expressions, and Boolean expressions map directly to logic gates. However, in order to minimize the number of logic gates needed to implement a circuit, it is often useful to simplify long Boolean expressions.

We can simplify expressions using the nine key laws of Boolean algebra:

| Name         | AND Form                                      | OR form                                         |

|--------------|-----------------------------------------------|-------------------------------------------------|

| Commutative  | AB = BA                                       | A + B = B + A                                   |

| Associative  | AB(C) = A(BC)                                 | A + (B + C) = (A + B) + C                       |

| Identity     | 1A = A                                        | 0 + A = A                                       |

| Null         | 0A = 0                                        | 1 + A = 1                                       |

| Absorption   | A(A + B) = A                                  | A + AB = A                                      |

| Distributive | (A + B)(A + C) = A + BC                       | A(B + C) = AB + AC                              |

| Idempotent   | A(A) = A                                      | A + A = A                                       |

| Inverse      | $A(\overline{A}) = 0$                         | $A + \overline{A} = 1$                          |

| Demorgan's   | $\overline{AB} = \overline{A} + \overline{B}$ | $\overline{A + B} = \overline{A}(\overline{B})$ |

[1.1] Simplify the following Boolean expressions:

(a)

$$(A+B)(A+\overline{B})C$$

(b)

$$\bar{A}\bar{B}\bar{C} + \bar{A}B\bar{C} + AB\bar{C} + A\bar{B}\bar{C} + ABC + A\bar{B}C$$

(c)

$$\overline{A(\bar{B}\bar{C} + BC)}$$

(d)

$$\overline{A}(A+B) + (B+AA)(A+\overline{B})$$

## 2 Logic Gates

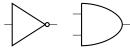

2.1 Label the following logic gates:

2.2 Convert the following to boolean expressions on input signals A and B:

- (a) NAND

- (b) XOR

- (c) XNOR

2.3 Create an AND gate using only NAND gates. (Hint: use 2.2!)

## 3 State Intro

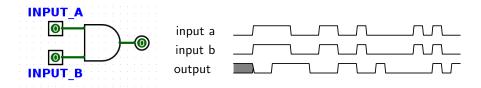

There are two basic types of circuits: combinational logic circuits and state elements. **Combinational logic** circuits simply change based on their inputs after whatever propagation delay is associated with them. For example, if an AND gate (pictured below) has an associated propagation delay of 2ps, its output will change based on its input as follows:

You should notice that the output of this AND gate always changes 2ps after its inputs change.

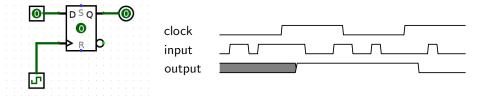

**State elements**, on the other hand, can *remember* their inputs even after the inputs change. State elements change value based on a clock signal. A rising edge-triggered register, for example, samples its input at the rising edge of the clock (when the clock signal goes from 0 to 1).

Like logic gates, registers also have a delay associated with them before their output will reflect the input that was sampled. This is called the **clk-to-q** delay. ("Q" often indicates output). This is the time between the rising edge of the clock signal and the time the register's output reflects the input change.

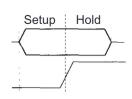

The input the register samples has to be stable for a certain amount of time around the rising edge of the clock for the input to be sampled accurately. The amount of time before the rising edge the input must be stable is called the **setup** time, and the time after the rising edge the input must be stable is called the **hold** time. Hold time is included in clk-

to-q delay, so clk-to-q time will always be greater than or equal to hold time. From another perspective, the fact that clk-to- $q \ge hold$  time makes sense since it only takes clk-to-q seconds to copy the value over, so there's no need to have the value fed into the register for any longer.

For the following register circuit, assume **setup** of 2.5ps, **hold** time of 1.5ps, and a **clk-to-q** time of 1.5ps. The clock signal has a period of 13ps.

You'll notice that the value of the output in the diagram above doesn't change immediately after the rising edge of the clock. Clock cycle time must be small enough that inputs to registers don't change within the hold time and large enough to account for clk-to-q times, setup times, and combinational logic delays.

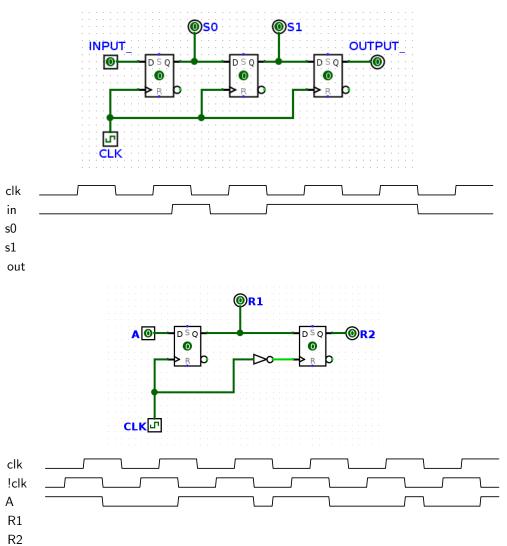

3.1 For the following 2 circuits, fill out the timing diagram. The clock period (rising edge to rising edge) is 8ps. For every register, clk-to-q delay is 2ps, setup time is 4ps, and hold time is 2ps. NOT gates have a 2ps propagation delay

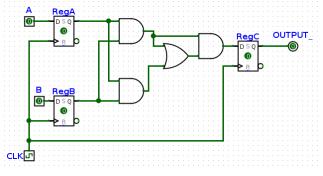

3.2 In the circuit below, RegA and RegB have setup, hold, and clk-to-q times of 4ns, all logic gates have a delay of 5ns, and RegC has a setup time of 6ns. What is the maximum allowable hold time for RegC? What is the minimum acceptable clock cycle time for this circuit, and clock frequency does it correspond to?