# What to do on a write hit?

- Write-through

- update the word in cache block and corresponding word in memory

- Write-back

- update word in cache block

allow memory word to be "stale"

- ⇒ add 'dirty' bit to each block indicating that memory needs to be updated when block is replaced

- ⇒ OS flushes cache before I/O...

- Performance trade-offs?

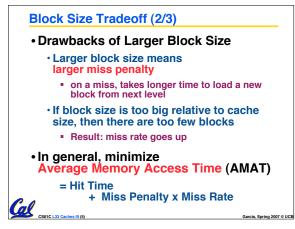

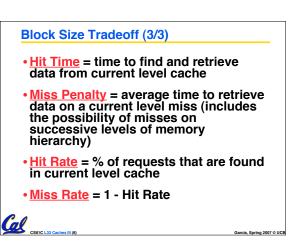

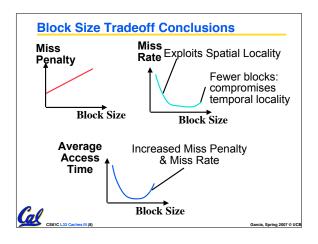

### Block Size Tradeoff (1/3)

Cal cont

#### Benefits of Larger Block Size

- <u>Spatial Locality</u>: if we access a given word, we're likely to access other nearby words soon

- Very applicable with Stored-Program Concept: if we execute a given instruction, it's likely that we'll execute the next few as well

Garcia, Spring 2007 © UCB

Works nicely in sequential array accesses too

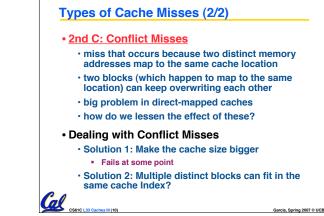

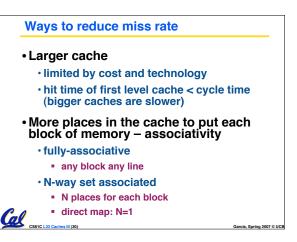

# Types of Cache Misses (1/2) "Three Cs" Model of Misses 1st C: Compulsory Misses occur when a program is first started cache does not contain any of that program's data yet, so misses are bound to occur can't be avoided easily, so won't focus on these in this course

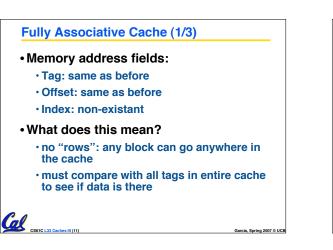

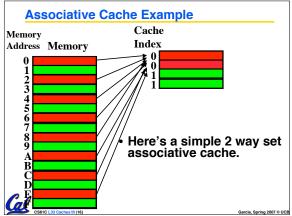

# N-Way Set Associative Cache (1/3)

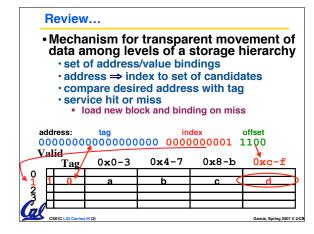

### • Memory address fields:

- · Tag: same as before

- Offset: same as before

- · Index: points us to the correct "row" (called a set in this case)

### So what's the difference?

- · each set contains multiple blocks

- once we've found correct set, must compare with all tags in that set to find our data

Garcia, Spring 2007 @ UCE

Garcia, Spring 2007 © UCB

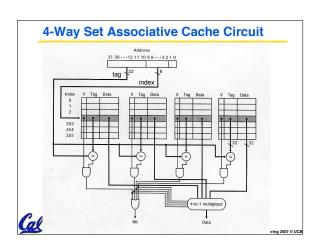

### N-Way Set Associative Cache (2/3)

#### Basic Idea

CS61C L33 Caches III (15)

- · cache is direct-mapped w/respect to sets

- · each set is fully associative

- · basically N direct-mapped caches working in parallel: each has its own valid bit and data

- Given memory address:

s III (17)

- Find correct set using Index value.

- · Compare Tag with all Tag values in the determined set.

- · If a match occurs, hit!, otherwise a miss.

- · Finally, use the offset field as usual to find the desired data within the block.

# N-Way Set Associative Cache (3/3)

#### What's so great about this?

hes III (18)

- even a 2-way set assoc cache avoids a lot of conflict misses

- hardware cost isn't that bad: only need N comparators

## In fact, for a cache with M blocks,

- it's Direct-Mapped if it's 1-way set assoc

- · it's Fully Assoc if it's M-way set assoc

- so these two are just special cases of the more general set associative design

Garcia, Spring 2007 © UCB

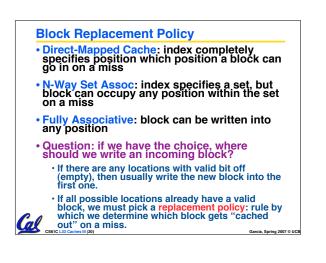

# **Block Replacement Policy: LRU**

# LRU (Least Recently Used)

- · Idea: cache out block which has been accessed (read or write) least recently

- Pro: temporal locality ⇒ recent past use implies likely future use: in fact, this is a very effective policy

- · Con: with 2-way set assoc, easy to keep track (one LRU bit); with 4-way or

|     | and much time to keep track |                           |

|-----|-----------------------------|---------------------------|

| Cal | CSBIC L33 Caches III (21)   | Garcia, Spring 2007 © UCB |

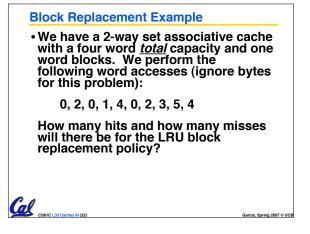

| Block Replacement Example: LRU loc 0 loc 1   |                           |  |  |  |

|----------------------------------------------|---------------------------|--|--|--|

| • Addresses 0, 2, 0, 1, 4, 0,                | set 0 0 Iru               |  |  |  |

| 0: miss, bring into set 0 (loc 0)            | set 1                     |  |  |  |

| 2: miss, bring into set 0 (loc 1)            | set 0 <sup>ru</sup> 02    |  |  |  |

|                                              | set 1                     |  |  |  |

| 0: hit                                       | set 0 0 ru2               |  |  |  |

| 0                                            | set 1                     |  |  |  |

| 1: miss, bring into set 1 (loc 0)            | set 0 0 ru2               |  |  |  |

|                                              | set 1 1 <sup>Iru</sup>    |  |  |  |

| 4: miss, bring into set 0 (loc 1, replace 2) | set 0 <sup>Iru</sup> 0 4  |  |  |  |

|                                              | set 1 1 <sup>Iru</sup>    |  |  |  |

| 0: <u>hit</u>                                | set 0 0 <sup>Iru</sup> 4  |  |  |  |

|                                              | set 1 1 <sup>Iru</sup>    |  |  |  |

| CS61C L33 Caches III (23)                    | Garcia, Spring 2007 © UCE |  |  |  |

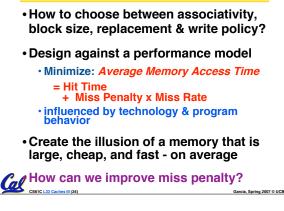

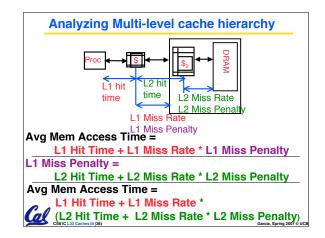

# **Big Idea**

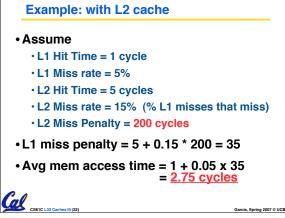

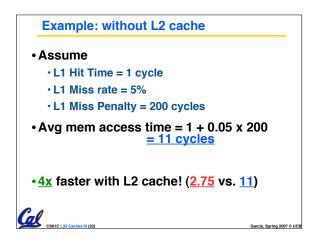

- When caches first became popular, Miss Penalty ~ 10 processor clock cycles

- Today 2400 MHz Processor (0.4 ns per clock cycle) and 80 ns to go to DRAM

⇒ 200 processor clock cycles!

Solution: another cache between memory and the processor cache: <u>Second Level (L2) Cache</u>

|                                            | Peer Instructions                                                            |           |                  |

|--------------------------------------------|------------------------------------------------------------------------------|-----------|------------------|

|                                            |                                                                              |           |                  |

|                                            |                                                                              |           |                  |

|                                            |                                                                              |           |                  |

|                                            |                                                                              |           |                  |

| of DRAMs & the cycle time of processors ha | In the last 10 years, the gap between the access time                        |           | ABC              |

|                                            | of DRAMs & the cycle time of processors has<br>decreased. (I.e., is closing) | 0:        | FFF              |

| 2.                                         | A 2-way set-associative cache can be outperformed                            | 2:        | FTF              |

| by a direct-mapped cache.                  | by a direct-mapped cache.                                                    | 3:        | FTT<br>TFF       |

| 3.                                         | Larger block size ⇒ lower miss rate                                          | 5:        | TFT              |

| Ca                                         | 1                                                                            | 6:<br>7:  | TTF<br>TTT       |

| 1                                          | CS61C L33 Caches III (38)                                                    | Garcia, S | pring 2007 © UCB |