CS61C, Spring 2008

[TA] Ben Sussman

(This page looks best in Firefox. Use it)

Due Saturday, April 5, 2008 @ 11:59:59pm

But, pretend it's due Friday, as HW7 is on its way soon

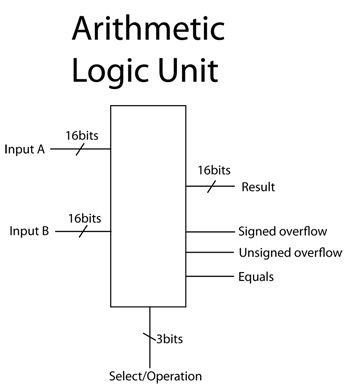

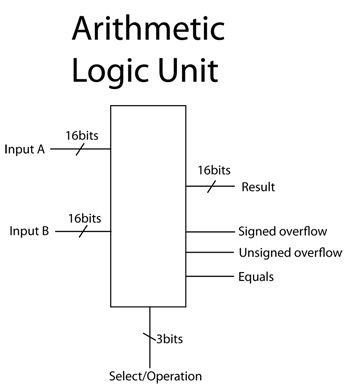

In this assignment, you will implement a 16 bit ALU in logisim. NOTICE: There is a new diagram as there seemed to be a lot of confusion generated from the strange layout of the inputs and outputs on the previous one. I hope this one is more clear.

The nine functions that you will implement are: add, subtract, OR, AND, shift left logical, shift right logical, shift right arithmetic, set less than, and EQUAL. The ALU will perform a desired function on two 16-bit inputs (X and Y, where x0 is the lowest order bit for x, etc...) and output the result (RESULT). The function will be determined by the value of a control signal (S), as listed below.

In addition to the 16 bits of output provided in RESULT, three additional outputs will be provided: unsigned overflow, signed overflow and equal. Unsigned overflow will have a high value iff the command was an add and unsigned overflow occured. Signed overflow will have a high value iff the command was an add or a subtract, and signed overflow occured. (You need not worry about unsigned overflow for subtractions.) Equal will have a high value when the two inputs are IDENTICAL, and will have a low value at all other times. Notice how the equals signal is generated REGARDLESS of the value of the control signal S.

For the shift instructions detailed below (sll, srl, sra), the shift amount is ONLY the 4 least significant bits of Y. You can ignore the other bits of Y.

Here's what occurs for each operation:

| S | opp | Result |

|---|---|---|

| 000 | add | X + Y (signal if either type of overflow occurs) |

| 001 | sub | X - Y (signal if signed overflow occurs) |

| 010 | or | X | Y |

| 011 | and | X & Y |

| 100 | sll | X << Y (but logically, don't sign extend!) |

| 101 | srl | X >> Y (but logically, don't sign extend!) |

| 110 | sra | X >> Y (but arithmetically, do sign extend!) |

| 111 | slt | if (X < Y) //Treat X and Y as SIGNED! then result = 1 else result = 0 |

| XXX | eq | X == Y (Have this value be on the equals output regardless of selection) |

Think about intuitive ways to test your ALU. If the grader can look at your logisim file and immediately see that everything is in working order, it will be to your advantage. You might consider some method for automatically testing your ALU, such as a counter. Perhaps you should add testing logic that signals an error if an incorrect value is seen. Think about this, we want to see some form of testing suite in your outter-most circuit design.

You may only use tools from the "Base" and "Gates" libraries in Logisim. Do not use any items from the Memory, Plexers, Arithmetic, or Legacy libraries. Any ALU pieces built using any of these illegal components will be given no credit.

Create a directory named 'hw6' containing a README, alu.circ, and any additional files needed for your submission. While in that directory, run 'submit hw6'. If you included an image, make sure to say "yes" when the submit script prompts you about it.