## **Today**

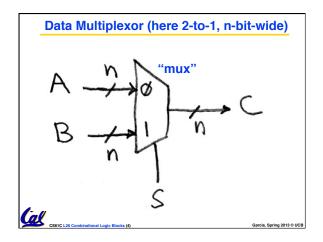

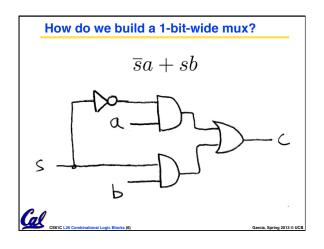

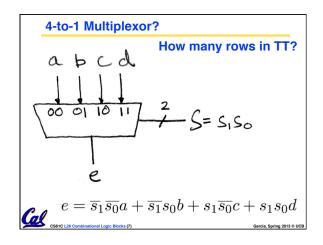

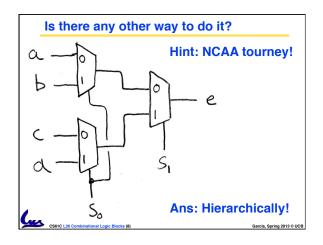

- Data Multiplexors

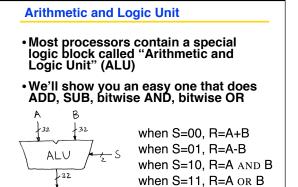

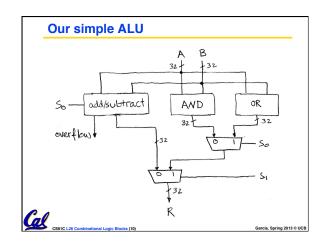

- Arithmetic and Logic Unit

- Adder/Subtractor

R

CS61C L2

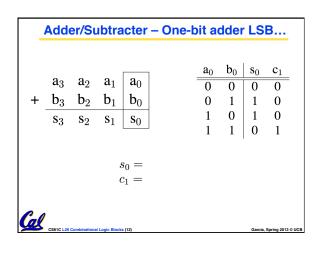

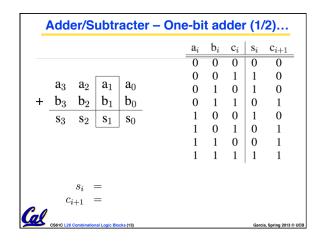

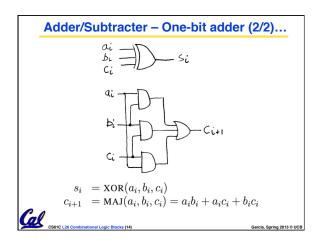

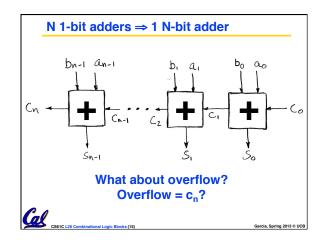

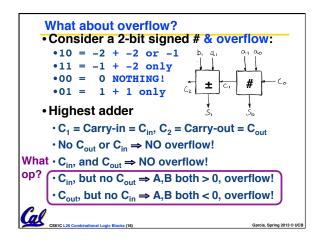

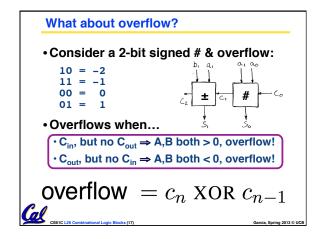

## Adder/Subtracter Design -- how? Truth-table, then determine canonical form, then minimize and implement as we've seen before Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

## **Peer Instruction**

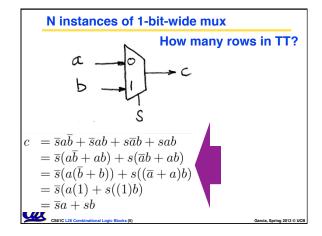

1) Truth table for mux with 4-bits of signals has 24 rows

12 a) FF b) FT c) TF d) TT

2) We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl

## "And In conclusion..."

- Use muxes to select among input

- ·S input bits selects 2<sup>S</sup> inputs

- Each input can be n-bits wide, indep of S

- Can implement muxes hierarchically

- ALU can be implemented using a mux

- Coupled with basic block elements

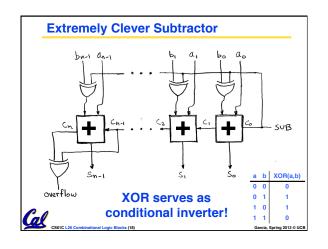

- N-bit adder-subtractor done using N 1-bit adders with XOR gates on input

- · XOR serves as conditional inverter