nst.eecs.berkeley.edu/~cs61c UCB CS61C : Machine Structures

Lecture 33 - Virtual Memory I

Sr Lecturer SOE Dan Garcia

#### **GOOGLE GLASS SPECS OUT**

Display: "high res equivalent to 25 inch HD screen from 8 feet away", 16GB flash, WiFi, Bluetooth, 5MP camera, 720p video, battery works for a day. GPS and text requires Android App. No 3rd party ads either.

#### Review

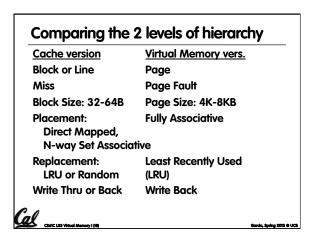

- Cache design choices:

- Size of cache: speed v. capacity

- Block size (i.e., cache aspect ratio)

- Write Policy (Write through v. write back)

- Associativity choice of N (direct-mapped v. set v. fully) associative)

- Block replacement policy

- 2nd level cache?

- o 3rd level cache?

- Use performance model to pick between choices, depending on programs, technology,

budget, ...

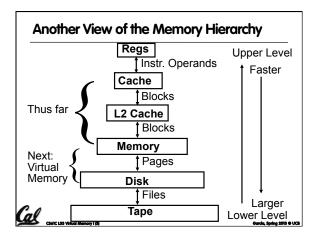

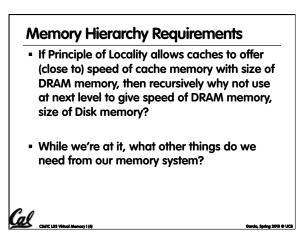

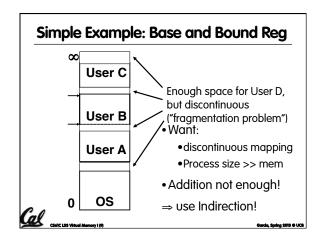

# **Memory Hierarchy Requirements**

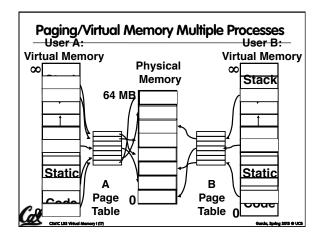

- Allow multiple processes to simultaneously occupy memory and provide protection don't let one program read/write memory from another

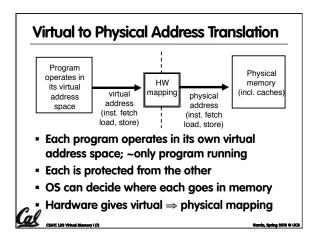

- Address space give each program the illusion that it has its own private memory

- Suppose code starts at address 0x40000000. But different processes have different code, both residing at the same address. So each program has a different view of memory. Call CSATC L33 Virtual Memory 1 (8)

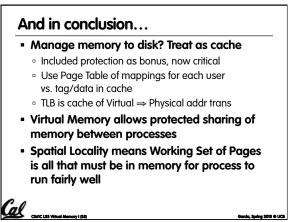

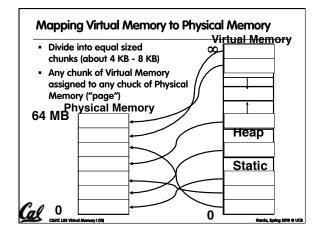

# Virtual Memory

- Next level in the memory hierarchy:

- Provides program with illusion of a very large main memory:

- Working set of "pages" reside in main memory others reside on disk

- Also allows OS to share memory, protect programs from each other

- Today, more important for protection vs. just another level of memory hierarchy

- Each process thinks it has all the memory to itself

Garda, Spring 2013 © UCB

(Historically, it predates caches)

Garda, Spring 2013 © UCB

# Analogy

Cal

- Book title like virtual address

- Library of Congress call number like physical address

- Card catalogue like page table, mapping from book title to call #

- On card for book, in local library vs. in another branch like valid bit indicating in main memory vs. on disk

- On card, available for 2-hour in library use (vs. 2-week checkout) like access rights

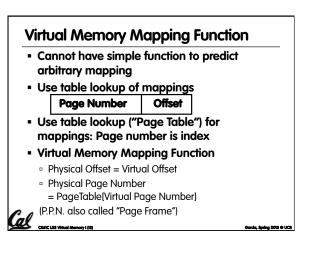

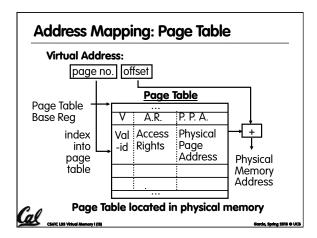

#### Page Table Entry (PTE) Format **Requirements revisited** - Remember the motivation for VM: - Contains either Physical Page Number or indication not in Main Memory Sharing memory with protection - OS maps to disk if Not Valid (V = 0) Different physical pages can be allocated to different processes (sharing) P. P.N. A.R • A process can only touch pages in its own page Page Table Physical Access Val table (protection) -id Rights Page - P.T.E. Separate address spaces Number Since programs work only with virtual addresses, ٧ A.R. P. P. N. different programs can have different data/code at the same address! If valid, also check if have permission to use What about the memory hierarchy? page: Access Rights (A.R.) may be Read Only, Read/Write, Executable Cal

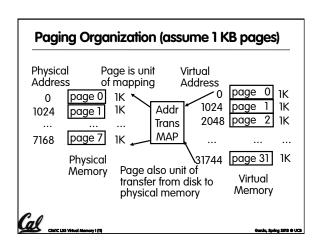

#### Notes on Page Table

- Solves Fragmentation problem: all chunks same size, so all holes can be used

- OS must reserve "Swap Space" on disk for each process

- To grow a process, ask Operating System

- If unused pages, OS uses them first

- If not, OS swaps some old pages to disk

- (Least Recently Used to pick pages to swap)

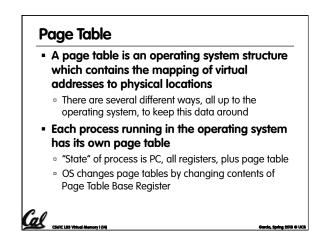

- Each process has own Page Table

- Will add details, but Page Table is essence of Virtual Memory

- Why would a process need to "grow"? A program's address space stack contains 4 regions: stack: local variables, grows downward • heap: space requested for

- pointers via malloc(); resizes dynamically, grows upward

- heap static data static data: variables declared code outside main, does not grow or For now, OS somehow prevents accesses between stack

a, Spring 2013 © UCE

Main

Memory

code: loaded when program starts, does not change

shrink

- and heap (gray hash lines)

- Virtual Memory Problem #1 Translation Look-Aside Buffers (TLBs) ■ Map every address ⇒ 1 indirection via Page • TLBs usually small, typically 128 - 256 entries Table in memory per virtual address  $\Rightarrow$  1 virtual - Like any other cache, the TLB can be direct memory accesses = mapped, set associative, or fully associative 2 physical memory accesses  $\Rightarrow$  SLOW! hit Observation: since locality in pages of data, there PΔ must be locality in virtual address translations of TLB Cache<sup>miss</sup> Processor Lookup those pages miss hit Since small is fast, why not use a small cache of data Transvirtual to physical address translations to make lation translation fast? - For historical reasons, cache is called a On TLB miss, get page table entry from main memory Translation Lookaside Buffer, or TLB ax

| _  | Peer Instruction                                                                                                                      |           |                 |

|----|---------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

|    |                                                                                                                                       |           |                 |

|    |                                                                                                                                       |           |                 |

|    |                                                                                                                                       |           |                 |

|    |                                                                                                                                       |           |                 |

| 1) | Locality is important yet different for cache and<br>virtual memory (VM): temporal locality for caches<br>but spatial locality for VM | a)<br>b)  | 12<br>FF<br>FT  |

| 2) | VM helps both with security and cost                                                                                                  | c)<br>d)  | TF<br>TT        |

| Ga | CSATC 133 Vinuel Memory 1 (23)                                                                                                        | Garda, Sj | xing 2018 © UCB |