Lecturer: Alan Christopher

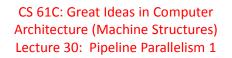

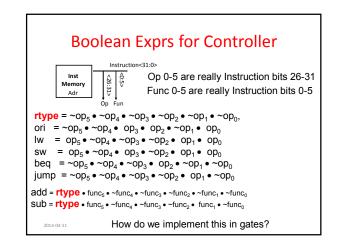

#### **Boolean Exprs for Controller** RegDst = add + sub ALUSrc = ori + lw + sw MemtoReg = Iw RegWrite = add + sub + ori + lw MemWrite = sw nPCsel = beq Jump = jump ExtOp = lw + sw ALUctr[0] = sub + beq ALUctr[1] = ori (assume ALUctr is 00 ADD, 01 SUB, 10 OR) How do we implement this in gates? 2014-04-11 Spring 2014 -- Lecture #31

### Administrivia/Clicker

• How many Gflop/s right now?

a) 0 <= F <= 4

- b) 4 < F <= 8

- c) 8 < F <= 12

- d) 12 < F <= 16

- e) 16 < F

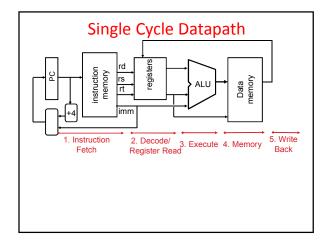

# Single Cycle Performance

• Assume time for actions are

100ps for register read or write; 200ps for other events

Clock rate is?

| Instr    | Instr fetch | Register<br>read | ALU op | Memory<br>access | Register<br>write | Total time |

|----------|-------------|------------------|--------|------------------|-------------------|------------|

| lw       | 200ps       | 100 ps           | 200ps  | 200ps            | 100 ps            | 800ps      |

| sw       | 200ps       | 100 ps           | 200ps  | 200ps            |                   | 700ps      |

| R-format | 200ps       | 100 ps           | 200ps  |                  | 100 ps            | 600ps      |

| beq      | 200ps       | 100 ps           | 200ps  |                  |                   | 500ps      |

· What can we do to improve clock rate?

- Will this improve performance as well?

- Want increased clock rate to mean faster programs

# Single Cycle Performance

- Assume time for actions are

- 100ps for register read or write; 200ps for other events

- Clock rate is?

| Instr    | Instr fetch | Register<br>read | ALU op | Memory<br>access | Register<br>write | Total time |

|----------|-------------|------------------|--------|------------------|-------------------|------------|

| lw       | 200ps       | 100 ps           | 200ps  | 200ps            | 100 ps            | 800ps      |

| sw       | 200ps       | 100 ps           | 200ps  | 200ps            |                   | 700ps      |

| R-format | 200ps       | 100 ps           | 200ps  |                  | 100 ps            | 600ps      |

| beq      | 200ps       | 100 ps           | 200ps  |                  |                   | 500ps      |

• What can we do to improve clock rate?

Will this improve performance as well? Want increased clock rate to mean faster programs

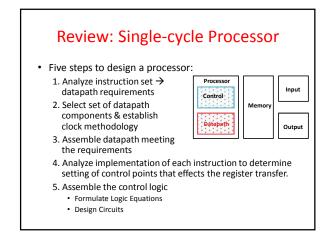

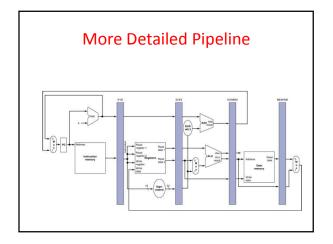

## So, in conclusion

- You now know how to implement the control logic for the single-cycle CPU.

– (actually, you already knew it!)

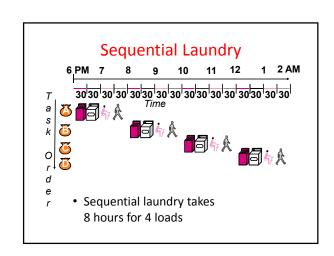

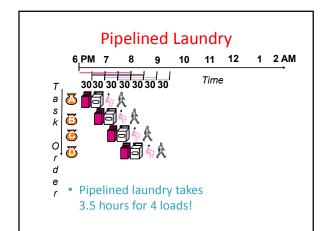

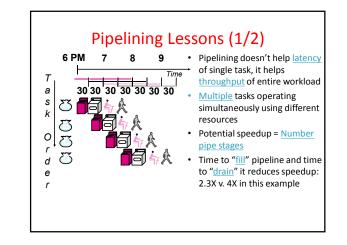

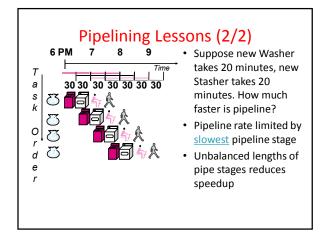

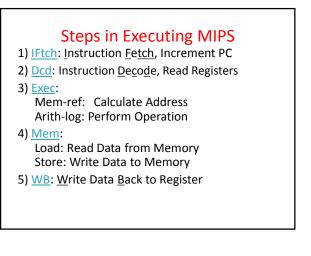

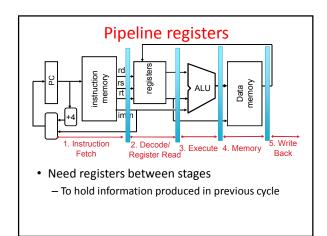

- Pipelining improves performance by increasing instruction throughput: exploits ILP

- Executes multiple instructions in parallel

- Each instruction has the same latency

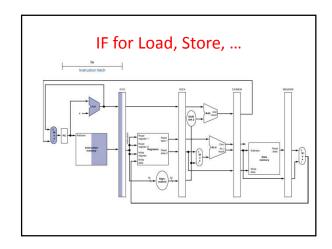

- Next: hazards in pipelining:

- Structure, data, control