nst.eecs.berkeley.edu/~cs61c

**CS61C: Machine Structures**

Lecture #12 - MIPS Instruction Rep III, Running a Program I aka Compiling, Assembling, Linking, Loading (CALL)

2007-7-16

### **Scott Beamer, Instructor**

**New Direction** Service Announced

DIR-ECT-IONS

### **Review of Floating Point**

Reserve exponents, significands:

Exponent Significand Object O O nonzero **Denorm** 1-254 anything +/- fl. pt. # 255 +/- ∞ 255 nonzero NaN

- Integer mult, div uses hi, lo regs ·mfhi and mflo copies out.

- Four rounding modes (to even default)

- MIPS FL ops complicated, expensive

#### **Clarification Unbiased Rounding**

- Round to (nearest) even (default)

- Normal rounding, almost:  $2.5 \Rightarrow 2, 3.5 \Rightarrow 4$

- · Insures fairness on calculation

- · Half the time we round up, other half down

- Decimal gives a good initial intuition, but remember computers use binary

- Steps to Use it (in binary)

- · Determine place to be rounded to

- Figure out the two possible outcomes (its binary so 1 or 0 in last place)

- If one outcome is closer to current number than other, pick that outcome

If both outcomes are equidistant pick the

outcome that ends in 0

# **Decoding Machine Language**

- · How do we convert 1s and 0s to C code? Machine language ⇒ C?

- For each 32 bits:

- · Look at opcode: 0 means R-Format, 2 or 3 mean J-Format, otherwise I-Format.

- Use instruction type to determine which fields exist.

- · Write out MIPS assembly code, converting each field to name, register number/name, or decimal/hex number.

- Logically convert this MIPS code into valid C code. Always possible? Unique?

# **Decoding Example (1/7)**

Here are six machine language instructions in hexadecimal:

> 00001025<sub>hex</sub> 0005402A<sub>hex</sub> 11000003<sub>hex</sub> 00441020<sub>hex</sub>  ${\tt 20A5FFFF}_{\tt hex}$ 08100001<sub>hex</sub>

- · Let the first instruction be at address  $4,194,304_{\text{ten}} (0x00400000_{\text{hex}}).$

- Next step: convert hex to binary

#### **Decoding Example (2/7)**

The six machine language instructions in binary:

0000000000000000001000000100101 0000000000001010100000000101010 001000001010010111111111111111111

Next step: identify opcode and format

| R   | 0       | rs             | rt | rd        | shamt funct |  |

|-----|---------|----------------|----|-----------|-------------|--|

| - 1 | 1, 4-31 | rs             | rt | immediate |             |  |

| J   | 2 or 3  | target address |    |           |             |  |

#### **Decoding Example (3/7)**

Select the opcode (first 6 bits) to determine the format:

#### Format:

- 0000000000000000001000000100101 00000000000001010100000000101010 0000000001000100000100000100000 001000 001010100101111111111111111 000010

- Look at opcode: 0 means R-Format, 2 or 3 mean J-Format, otherwise I-Format.

#### **Decoding Example (4/7)**

Fields separated based on format/opcode:

| R | 0 | 0         | 0 | 2 | 0  | 37 |

|---|---|-----------|---|---|----|----|

| R | 0 | 0         | 5 | 8 | 0  | 42 |

| 1 | 4 | 8         | 0 |   | +3 |    |

| R | 0 | 2         | 4 | 2 | 0  | 32 |

| 1 | 8 | 5         | 5 |   | -1 |    |

| J | 2 | 1,048,577 |   |   |    |    |

• Next step: translate ("disassemble") to MIPS assembly instructions

# **Decoding Example (5/7)**

• MIPS Assembly (Part 1):

| Address:            | Assembly instructions: |             |  |  |

|---------------------|------------------------|-------------|--|--|

| 0x00400000          | or                     | \$2,\$0,\$0 |  |  |

| $0 \times 00400004$ | slt                    | \$8,\$0,\$5 |  |  |

| $0 \times 00400008$ | beq                    | \$8,\$0,3   |  |  |

| 0x0040000c          | add                    | \$2,\$2,\$4 |  |  |

| 0x00400010          | addi                   | \$5,\$5,-1  |  |  |

| $0 \times 00400014$ | Ė                      | 0×100001    |  |  |

Better solution: translate to more meaningful MIPS instructions (fix the branch/jump and add labels, règisters)

CS61C L12 MIPS Instruction Rep III, Running a Program I (9)

# **Decoding Example (6/7)**

• MIPS Assembly (Part 2):

```

$<del>v</del>0,$0,$0

$t0,$0,$a1

Loop:

slt

beq

$t0,$0,Exit

$v0,$v0,$a0

add

addi

$a1,$a1,-1

j

Loop

Exit:

```

• Next step: translate to C code (be creative!)

Cal

# **Decoding Example (7/7)**

#### Before Hex: After C code (Mapping below) \$v0: product 00001025<sub>hex</sub> \$a0: multiplicand 0005402A<sub>hex</sub> \$a1: multiplier 11000003<sub>hex</sub> product = 0; 00441020<sub>hex</sub> 20A5FFFF<sub>hex</sub> while (multiplier > 0) { product += multiplicand; 08100001<sub>hex</sub> multiplier -= 1;

\$v0,\$0,\$0 orLoop: slt \$t0,\$0,\$a1 beq \$t0,\$0,Exit add \$v0,\$v0,\$a0 addi \$a1,\$a1,-1 Loop Exit:

**Demonstrated Big 61C** Idea: Instructions are iust numbers, code is treated like data

#### Administrivia...Midterm in 7 days!

- Project 2 due Friday @ 11:59pm

- Midterm 7/23 @ 7-10pm 60 Evans

- Bring...

- NO backpacks, cells, calculators, pagers, PDAs

- 2 writing implements (we'll provide write-in exam booklets) - pencils ok!

- One handwritten (both sides) 8.5"x11" paper

- One green sheet (or copy of it)

- Review Session Friday @ ...

#### Review from before: lui

- •So how does lui help us?

- · Example:

addi \$t0,\$t0, 0xABABCDCD

becomes:

lui \$at, 0xABAB

ori \$at, \$at, 0xCDCD

add \$t0,\$t0,\$at

- Now each I-format instruction has only a 16bit immediate.

- Wouldn't it be nice if the assembler would this for us automatically?

- If number too big, then just automatically replace addi with lui, ori, add

### **True Assembly Language (1/3)**

- Pseudoinstruction: A MIPS instruction that doesn't turn directly into a machine language instruction, but into other MIPS instructions

- What happens with pseudoinstructions?

- They're broken up by the assembler into several "real" MIPS instructions.

- But what is a "real" MIPS instruction? Answer in a few slides

- First some examples

CSSIC I 12 MIDS Instruction Rep III Bunning a Program I (14)

leamer Summer 2007 © I

#### **Example Pseudoinstructions**

Register Move

move reg2,reg1

Expands to:

add reg2,\$zero,reg1

Load Immediate

li reg,value

If value fits in 16 bits:

addi reg,\$zero,value

else:

lui reg,upper 16 bits of value

ori reg,\$zero,lower 16 bits

CS61C L12 MIPS Instruction Rep III, Running a Program I (15)

Seamer Summer 2007 © UC

# **True Assembly Language (2/3)**

- Problem:

- When breaking up a pseudoinstruction, the assembler may need to use an extra reg.

- If it uses any regular register, it'll overwrite whatever the program has put into it.

- Solution:

- Reserve a register (\$1, called \$at for "assembler temporary") that assembler will use to break up pseudo-instructions.

- Since the assembler may use this at any time, it's not safe to code with it.

CS61C L12 MIPS Instruction Rep III, Running a Program I (16)

Seamer, Summer 2007 © II

#### **Example Pseudoinstructions**

Rotate Right Instruction

ror reg, value

Expands to:

srl \$at, reg, value

sll reg, reg, 32-value

or reg, reg, \$at

01 10g/ 10g/ <del>1</del>40

• "No OPeration" instruction

Expands to instruction =  $0_{\text{ten}}$ , s11 \$0, \$0, 0

Beamer, Summer 2007 © UCB

# **Example Pseudoinstructions**

Wrong operation for operand

addu reg, reg, value # should be addiu

If value fits in 16 bits, addu is changed to:

addiu reg,reg,value

else:

lui \$at,upper 16 bits of value

ori \$at,\$at,lower 16 bits

addu reg,reg,\$at

How do we avoid confusion about whether we are talking about MIPS assembler with or without pseudoinstructions?

CS61C L12 MIPS Instruction Rep III, Running a Program I (18)

Beamer, Summer 2007 © UC

#### **True Assembly Language (3/3)**

- MAL (MIPS Assembly Language): the set of instructions that a programmer may use to code in MIPS; this includes pseudoinstructions

- TAL (True Assembly Language): set of instructions that can actually get translated into a single machine language instruction (32-bit binary string)

- A program must be converted from MAL into TAL before translation into 1s & 0s.

ner, Summer 200

#### **Questions on Pseudoinstructions**

- Question:

- How does MIPS recognize pseudoinstructions?

- Answer:

- It looks for officially defined pseudoinstructions, such as ror and move

- It looks for special cases where the operand is incorrect for the operation and tries to handle it gracefully

Beamer, Summer 2007 © U

#### **Rewrite TAL as MAL**

•TAL:

or \$v0,\$0,\$0 Loop: slt \$t0,\$0,\$a1 beq \$t0,\$0,Exit add \$v0,\$v0,\$a0 addi \$a1,\$a1,-1 j Loop

- This time convert to MAL

- It's OK for this exercise to make up MAL instructions

CS61C L12 MIPS Instruction Rep III. Running a Program I (21)

leamer Summer 2007

#### **Rewrite TAL as MAL (Answer)**

• TAL:

Loop:

slt \$\text{\$\text{\$\text{\$t0}\$,\$\footnote{\$\text{\$0}\$,\$\footnote{\$\text{\$ald}\$}}\$} \$\$

beg add \$\text{\$\text{\$\text{\$\text{\$\$\text{\$\$\text{\$\$y0}\$,\$\text{\$\$\text{\$\$c1}\$}}\$} \$\$

addi \$\text{\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$}\$}\$} \$\$

beg add \$\text{\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\$\$\$\$\$\$}\$}\$}\$} \$\$

con \$\text{\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\$}\$}\$}\$}\$} \$\$

\$\text{\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\$}\$}\$}\$} \$\$

\$\text{\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\$}\$}\$}\$} \$\$

\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\ext{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\ext{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\ext{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\text{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\ext{\$\$\exititt{\$\$\ext{\$\$\

Exit:

• MAL:

Loop: bge \$zero,\$a1,Exit add \$v0,\$v0,\$a0 decr \$a1, 1 j Loop

Exit:

Cal

namer Summer 2007 © LIC

#### **Peer Instruction**

Which of the instructions below are MAL and which are TAL?

```

A. addi $t0, $t1, 40000

B. beq $s0, 10, Exit

C. sub $t0, $t1, 1

```

ABC

1: MMM

2: MMT

3: MTM

4: MTT

5: TMM

6: TMT

7: TTM

8: TTT

#### In semi-conclusion...

- Disassembly is simple and starts by decoding opcode field.

- · Be creative, efficient when authoring C

- Assembler expands real instruction set (TAL) with pseudoinstructions (MAL)

- · Only TAL can be converted to raw binary

- · Assembler's job to do conversion

- · Assembler uses reserved register \$at

- · MAL makes it much easier to write MIPS

CS61C L12 MIPS Instruction Rep III, Running a Program I (25)

leamer, Summer 2007 © UCB

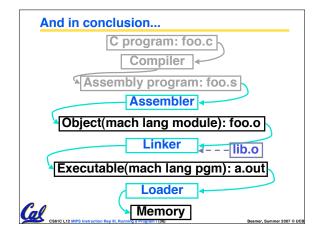

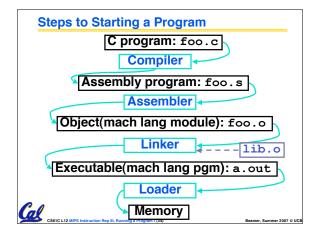

#### **Overview**

- Interpretation vs Translation

- Translating C Programs

- Compiler

- Assembler (next time)

- · Linker (next time)

- Loader (next time)

- An Example (next time)

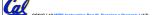

# **Interpretation vs Translation**

- How do we run a program written in a source language?

- Interpreter: Directly executes a program in the source language

- Translator: Converts a program from the source language to an equivalent program in another language

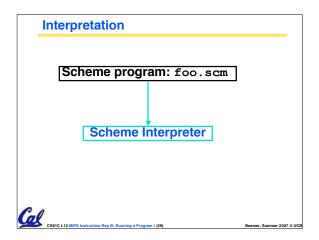

- For example, consider a Scheme program foo.scm

# Scheme program: foo.scm Scheme Compiler (+ assembler & linker) Executable(mach lang pgm): a.out Hardware \*Scheme Compiler is a translator from Scheme to machine language. Color Liz MPS instruction Rep. II, Running a Program (18)

# Interpretation

- Any good reason to interpret machine language in software?

- SPIM useful for learning / debugging

- What if you want to run compiled programs (executables) from another ISA?

- Examples

- VirtualPC let Windows (compiled to x86) run on old Macs (680x0 or PowerPC)

- · Run old video games on newer consoles

CSSIC L12 MIPS Instruction Rep III, Running a Program I (31)

Beamer, Summer 2007 6:

#### **Machine Code Interpretation**

- Apple's Two Conversions

- In the last 2 years, switched to Intel's x86 from IBM's PowerPC

- Could require all programs to be re-translated from high level language

- Did so with minimal disruption to programmer, and especially the user

- Rosetta allows old PowerPC programs to run on the new x86 systems by runtime translation

- Universal Binaries contain the machine code for both platforms, so both systems can run at native speeds

- Did a similar thing 13 years ago when they switched from Motorola 680x0 instruction architecture to PowerPC

....

### Interpretation vs. Translation?

- Easier to write interpreter

- Interpreter closer to high-level, so gives better error messages (e.g., SPIM)

- Translator reaction: add extra information to help debugging (line numbers, names)

- Interpreter slower (10x?) but code is smaller (1.5X to 2X?)

- Interpreter provides instruction set independence: run on any machine

- Apple switched to PowerPC. Instead of retranslating all SW, let executables contain old and/or new machine code, interpret old code in software if necessary

# Compiler

- Input: High-Level Language Code (e.g., C, Java such as foo.c)

- Output: Assembly Language Code (e.g., foo.s for MIPS)

- Note: Output may contain pseudoinstructions

- Pseudoinstructions: instructions that assembler understands but not in machine. E.g.,

- mov  $$s1,$s2 \Rightarrow or $s1,$s2,$zero$

Cal

CS61C L12 MIPS Instruction Rep III, Running a Program I (35)

Beamer Summer 2007