#### Laws of Boolean Algebra complementarity $x \cdot \overline{x} = 0$ $x + \overline{x} = 1$ $x\cdot 0=0$ x+1=1laws of 0's and 1's $x \cdot 1 = x$ x + 0 = xidentities idempotent law $x \cdot x = x$ x + x = x $x\cdot y=y\cdot x$ x + y = y + xcommutativity (xy)z = x(yz)(x+y) + z = x + (y+z)associativity distribution $x(y+z) = xy + xz \qquad x + yz = (x+y)(x+z)$ xy + x = x(x+y)x = xuniting theorem $\overline{x\cdot y}=\overline{x}+\overline{y}$ $\overline{(x+y)}=\overline{x}\cdot\overline{y}$ DeMorgan's Law **Cal** CS61C L17.0

# Data MultiplexorsArithmetic and Logic UnitAdder/Subtractor

**Today**

• Programmable Logic Arrays

#### **Administrivia**

- Assignments

- · HW5 due 7/26

- · HW6 due 729

- Midterm Regrade Policy

- · What you do...

- On paper, explain what was graded incorrectly

- Staple to front of exam and give to TA or Scott by 8/1

- · What we do...

- Regrade the entire exam blind

- Then look at what you wrote, discuss as staff, and regrade

- Warning: your grade can go down

Reamer Summer 2007 © U

## What does it mean to "clobber" midterm?

- You STILL have to take the final even if you aced the midterm!

- The final will contain midterm-material Qs and new, post-midterm Qs

- · They will be graded separately

- If you do "better" on the midterm-material, we will clobber your midterm with the "new" score! If you do worse, midterm unchanged.

- · What does "better" mean?

- · Better w.r.t. Standard Deviations around mean

- What does "new" mean?

- Score based on remapping St. Dev. score on final midterm-material to midterm score St. Dev.

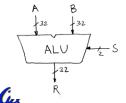

**Our simple ALU**

eamer Summer 2007 ©

# **Arithmetic and Logic Unit**

- Most processors contain a special logic block called "Arithmetic and Logic Unit" (ALU)

- We'll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR

when S=00, R=A+B when S=01, R=A-B when S=10, R=A AND B when S=11, R=A OR B

Reamer Summer 2007 © UCF

#

# Adder/Subtracter Design -- how?

- Truth-table, then determine canonical form, then minimize and implement as we've seen before

- Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

Beamer, Summer 2007 © UCE

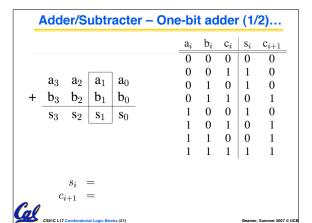

# Adder/Subtracter - One-bit adder LSB...

$$\begin{array}{c|cccc} a_0 & b_0 & s_0 & c_1 \\ \hline 0 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 1 \\ \end{array}$$

$$s_0 = c_1 = c_1 = c_1$$

amer Summer 2007 @ HC

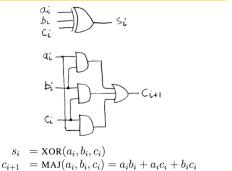

# Adder/Subtracter – One-bit adder (2/2)...

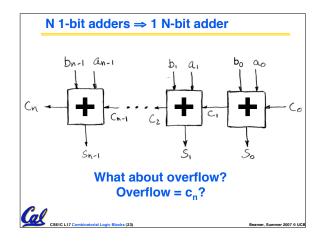

#### What about overflow?

Consider a 2-bit signed # & overflow:

Highest adder

Cal

- $\cdot$  C<sub>1</sub> = Carry-in = C<sub>in</sub>, C<sub>2</sub> = Carry-out = C<sub>out</sub>

- No  $C_{out}$  or  $C_{in} \Rightarrow NO$  overflow!

What  $\cdot C_{in}$ , and  $C_{out} \Rightarrow NO$  overflow!

op?  $\left( \cdot C_{\text{in}} \right)$ , but no  $C_{\text{out}} \Rightarrow A,B \text{ both } > 0$ , overflow!

• C<sub>out</sub>, but no C<sub>in</sub> ⇒ A,B both < 0, overflow!</p>

Beamer, Summer 2007 © UCB

#### What about overflow?

Consider a 2-bit signed # & overflow:

$$10 = -2 \\

11 = -1 \\

00 = 0 \\

01 = 1$$

- Overflows when...

- $C_{in}$ , but no  $C_{out} \Rightarrow A,B$  both > 0, overflow! •  $C_{out}$ , but no  $C_{in} \Rightarrow A,B$  both < 0, overflow!

overflow  $= c_n \text{ XOR } c_{n-1}$

Beamer, Summer 2007 © UCB

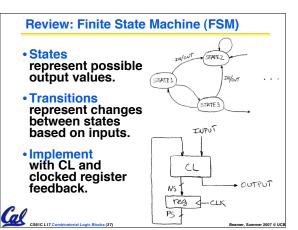

# Finite State Machines extremely useful!

- They define

- How output signals respond to input signals and previous state.

- How we change states depending on input signals and previous state

- We could implement very detailed FSMs w/Programmable Logic Arrays

Reamer Summer 2007 © UC

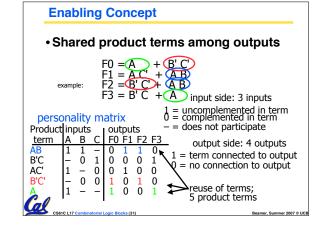

# Taking advantage of sum-of-products

- Since sum-of-products is a convenient notation and way to think about design, offer hardware building blocks that match that notation

- One example is Programmable Logic Arrays (PLAs)

- Designed so that can select (program) ands, ors, complements <u>after</u> you get the chip

- Late in design process, fix errors, figure out what to do later, ...

ogic Blocks (29)

Reamer Summer 2007 © I

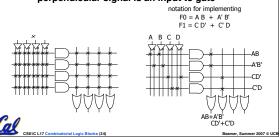

#### **Programmable Logic Arrays** · Pre-fabricated building block of many AND/OR gates · "Programmed" or "Personalized" by making or breaking connections among gates · Programmable array block diagram for sum of products form Or Programming: How to combine product terms?How many outputs? inputs OR AND product array outputs How many inputs?How to combine inputs? · How many product terms?

# **Before Programming**

• All possible connections available before "programming"

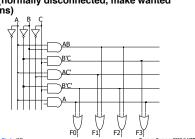

# **After Programming**

- Unwanted connections are "blown"

- · Fuse (normally connected, break unwanted ones)

- Anti-fuse (normally disconnected, make wanted connections)

## **Alternate Representation**

Cal

- · Short-hand notation--don't have to draw all

- · X Signifies a connection is present and perpendicular signal is an input to gate

# "And In conclusion..."

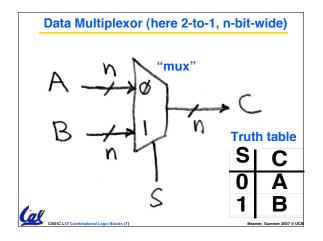

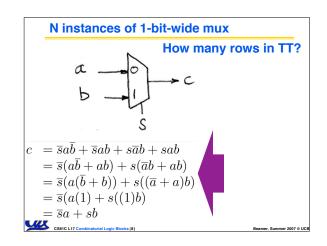

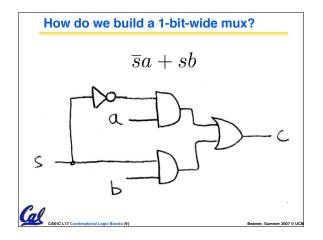

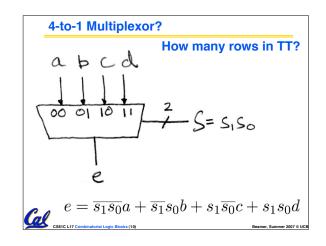

- Use muxes to select among input

- · S input bits selects 2<sup>S</sup> inputs

- · Each input can be n-bits wide, indep of S

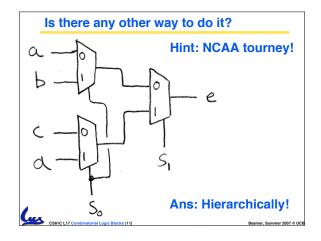

- Implement muxes hierarchically

- ALU can be implemented using a mux

- · Coupled with basic block elements

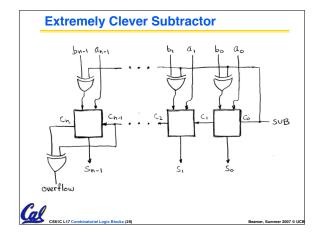

- N-bit adder-subtractor done using N 1-bit adders with XOR gates on input

- · XOR serves as conditional inverter

Programmable Logic Arrays are often used to implement our CL

#### **Peer Instruction**

- A. Truth table for mux with 4-bits of signals has 24 rows

- B. We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl

- C. If 1-bit adder delay is T, the N-bit adder delay would also be T

ABC 1: FFF 2: **FFT** FTF 4: FTT 5: TFF 6: **TFT** TTF 8: TTT