Cal

## **Historical Trivia**

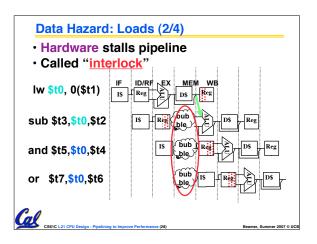

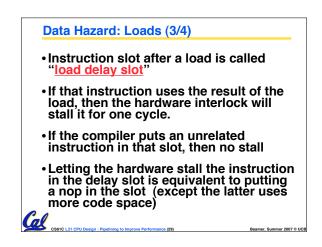

- First MIPS design did not interlock and stall on load-use data hazard

- Real reason for name behind MIPS: Microprocessor without Interlocked **P**ipeline **Stages**

Word Play on acronym for Millions of Instructions Per Second, also called MIPS

|            | Peer Instruction                                     |    |     |

|------------|------------------------------------------------------|----|-----|

|            |                                                      |    |     |

|            |                                                      |    |     |

|            |                                                      |    |     |

|            |                                                      |    |     |

|            |                                                      |    |     |

| Α.         | Thanks to pipelining, I have reduced the time in     | :  | ABC |

|            | took me to wash my shirt.                            | 0: | FFF |

|            | I an an all all and an all and a state of a large    | 1: | FFT |

| <b>B</b> . | Longer pipelines are <u>always a win</u> (since less | 2: | FTF |

|            | work per stage & a faster clock).                    | 3: | FTT |

| c.         | We can rely on compilers to help us avoid data       | 4: | TFF |

| 0.         | hazards by reordering instrs.                        | 5: | TFT |

|            | nazarus by reordening Instrs.                        | 6: | TTF |

| Co         |                                                      | 7: | TTT |

|            |                                                      |    |     |

## **Things to Remember**

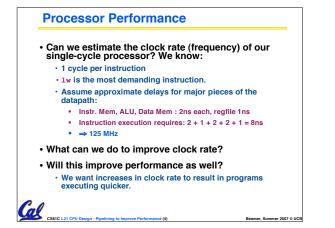

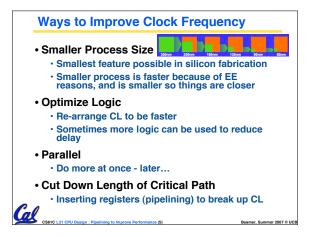

## Optimal Pipeline

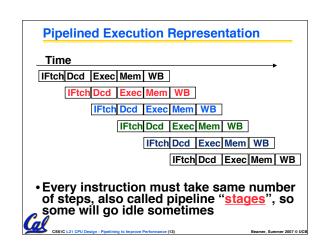

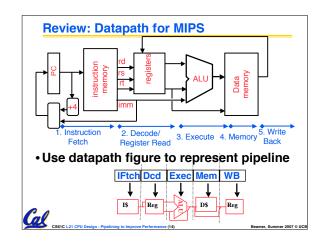

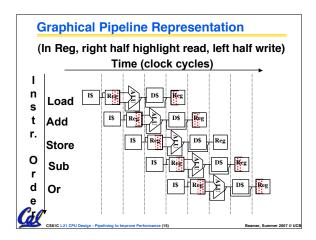

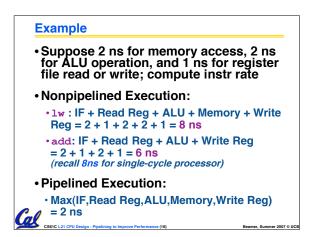

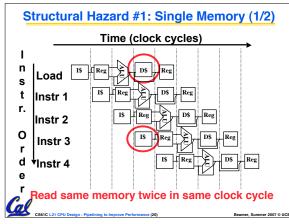

- Each stage is executing part of an instruction each clock cycle.

- One instruction finishes during each clock cycle.

- On average, execute far more quickly.

- What makes this work?

- Similarities between instructions allow us to use same stages for all instructions (generally).

- · Each stage takes about the same amount of time as all others: little wasted time. **G**

mer, Summer 2007 © UCB