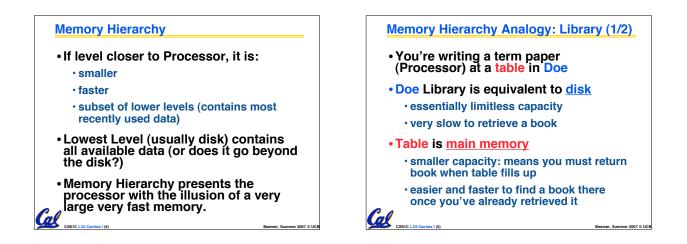

- Open books on table are <u>cache</u>

- smaller capacity: can have very few open books fit on table; again, when table fills up, you must close a book

- much, much faster to retrieve data

- Illusion created: whole library open on the tabletop

- Keep as many recently used books open on table as possible since likely to use again

- Also keep as many books on table as possible, since faster than going to library

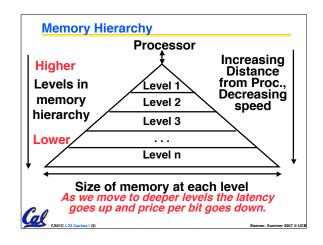

## Memory Hierarchy Basis

- Cache contains copies of data in memory that are being used.

- Memory contains copies of data on disk that are being used.

- Caches work on the principles of temporal and spatial locality.

- Temporal Locality: if we use it now, chances are we'll want to use it again soon.

- Spatial Locality: if we use a piece of memory, chances are we'll use the neighboring pieces soon.

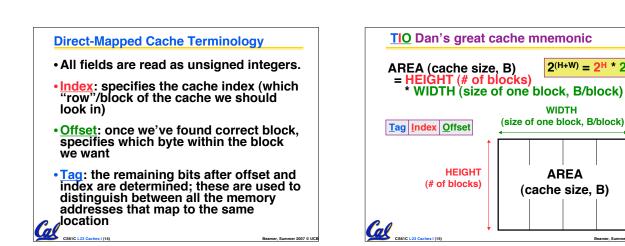

$2^{(H+W)} = 2^{H} * 2^{W}$

WIDTH

AREA

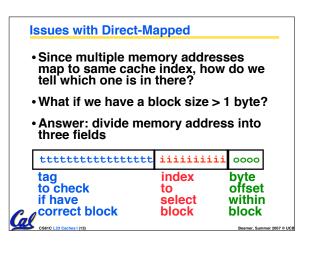

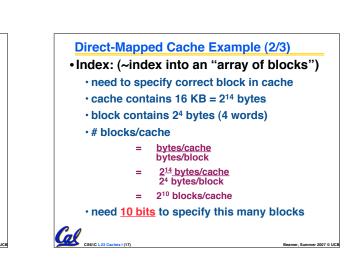

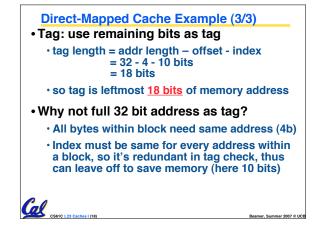

**Direct-Mapped Cache Example (1/3)**

Suppose we have a 16KB of data in a

offset fields if we're using a 32-bit

need <u>4 bits</u> to specify correct byte

block contains 4 words

architecture

Offset

Cal

direct-mapped cache with 4 word blocks

need to specify correct byte within a block

= 16 bytes = 2<sup>4</sup> bytes

Determine the size of the tag, index and

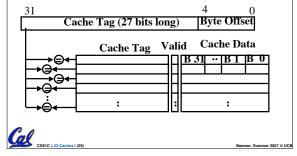

## Fully Associative Cache (1/3)

### • Memory address fields:

- Tag: same as before

- Offset: same as before

- Index: non-existant

CS61C L23 Caches I (28)

CS61C L23 Caches I (30)

#### • What does this mean?

• no "rows": any block can go anywhere in the cache

• must compare with all tags in entire cache to see if data is there

• Fully Associative Cache (e.g., 32 B block) · compare tags in parallel

Fully Associative Cache (2/3)

# Fully Associative Cache (3/3)

# Benefit of Fully Assoc Cache

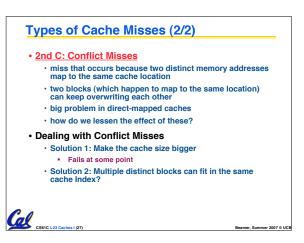

No Conflict Misses (since data can go anywhere)

#### • Drawbacks of Fully Assoc Cache

Need hardware comparator for every single entry: if we have a 64KB of data in cache with 4B entries, we need 16K comparators: infeasible

## Third Type of Cache Miss

CS61C L23 Caches I (31)

## Capacity Misses

- $\boldsymbol{\cdot}$  miss that occurs because the cache has a limited size

- miss that would not occur if we increase the size of the cache

- sketchy definition, so just get the general idea

Beamer, Summer 2007 © UCB

• This is the primary type of miss for Fully Associative caches.

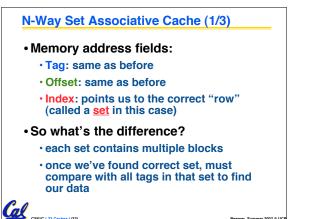

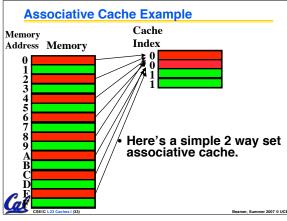

# N-Way Set Associative Cache (2/3)

#### Basic Idea

- · cache is direct-mapped w/respect to sets

- · each set is fully associative

- basically N direct-mapped caches working in parallel: each has its own valid bit and data

#### Given memory address:

- Find correct set using Index value.

- Compare Tag with all Tag values in the determined set.

- If a match occurs, hit!, otherwise a miss.

- Finally, use the offset field as usual to find the desired data within the block.

## What's so great about this?

- even a 2-way set assoc cache avoids a lot of conflict misses

- hardware cost isn't that bad: only need N comparators

#### In fact, for a cache with M blocks,

Cal

- it's Direct-Mapped if it's 1-way set assoc

- it's Fully Assoc if it's M-way set assoc

- so these two are just special cases of the more general set associative design

| _   | Peer Instruction                                                                    |           |                 |

|-----|-------------------------------------------------------------------------------------|-----------|-----------------|

|     |                                                                                     |           |                 |

|     |                                                                                     |           |                 |

|     |                                                                                     |           |                 |

|     |                                                                                     |           |                 |

|     |                                                                                     |           |                 |

| Α.  | Mem hierarchies were invented before<br>1950. (UNIVAC I wasn't delivered 'til 1951) | 0:        | ABC<br>FFF      |

| в.  | If you know your computer's cache size,<br>you can often make your code run faster. | 1:        | FFT             |

| C.  |                                                                                     | 3:        | FTT             |

| С.  | Memory hierarchies take advantage of<br>spatial locality by keeping the most recent | 4:        | TFF             |

|     | data items closer to the processor.                                                 | 5:        | TFT<br>TTF      |

| Cal | ,                                                                                   | 7:        | TTT             |

|     | CS61C L23 Caches I (37) Be                                                          | amer, Sur | nmer 2007 © UCB |