Cal

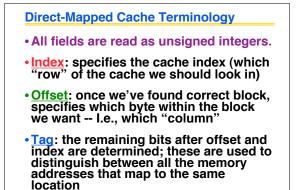

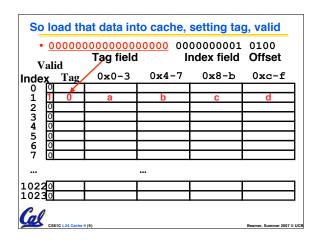

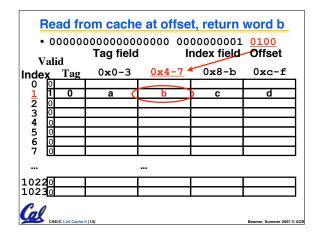

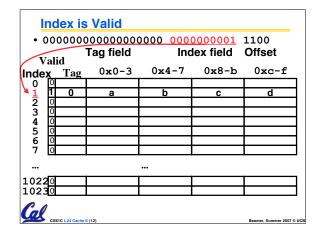

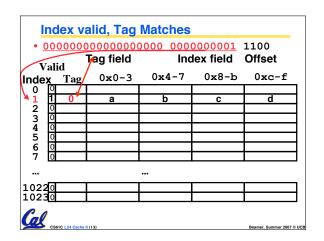

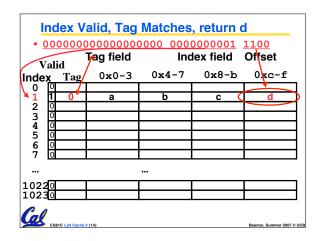

| 2. Read 0x0000001C = 000 0001 1100<br>• 000000000000000 000000001 1100<br>Tag field Index field Offset |                   |       |   |   |       |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-------------------|-------|---|---|-------|--|--|--|--|

|                                                                                                        | lid<br><u>Tag</u> | 0x0-3 |   |   | 0xc-f |  |  |  |  |

|                                                                                                        | 10                | a     | b | С | d     |  |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                        | 0                 |       |   |   |       |  |  |  |  |

| 5                                                                                                      | 0                 |       |   |   |       |  |  |  |  |

| 7                                                                                                      | 0                 |       |   |   |       |  |  |  |  |

| <br>1022                                                                                               | 0                 |       |   |   |       |  |  |  |  |

| 1023                                                                                                   |                   |       |   |   |       |  |  |  |  |

| CS61C L24 Cache II (11) Beamer, Summer 2007 @ UC                                                       |                   |       |   |   |       |  |  |  |  |

|                | Peer Instructions                                                                                                                                              |                      |                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|

|                |                                                                                                                                                                |                      |                                 |

|                |                                                                                                                                                                |                      |                                 |

|                |                                                                                                                                                                |                      |                                 |

|                |                                                                                                                                                                |                      |                                 |

|                |                                                                                                                                                                |                      |                                 |

| 1.             | In the last 10 years, the gap between the access time                                                                                                          |                      | ABC                             |

| 1.             | In the last 10 years, the gap between the access time<br>of DRAMs & the cycle time of processors has                                                           | 0:                   | ABC<br>FFF                      |

| 1.             |                                                                                                                                                                | 0:                   |                                 |

|                | of DRAMs & the cycle time of processors has<br>decreased. (I.e., is closing)                                                                                   |                      | FFF                             |

|                | of DRAMs & the cycle time of processors has                                                                                                                    | 1:                   | FFF<br>FFT                      |

|                | of DRAMs & the cycle time of processors has<br>decreased. (I.e., is closing)<br>A 2-way set-associative cache can be outperformed                              | 1:                   | FFF<br>FFT<br>FTF               |

| 2.             | of DRAMs & the cycle time of processors has<br>decreased. (I.e., is closing)<br>A 2-way set-associative cache can be outperformed                              | 1:<br>2:<br>3:       | FFF<br>FFT<br>FTF<br>FTT        |

| 1.<br>2.<br>3. | of DRAMs & the cycle time of processors has<br>decreased. (I.e., is closing)<br>A 2-way set-associative cache can be outperformed<br>by a direct-mapped cache. | 1:<br>2:<br>3:<br>4: | FFF<br>FFT<br>FTF<br>FTT<br>TFF |

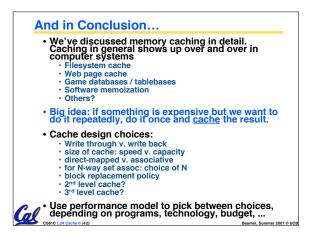

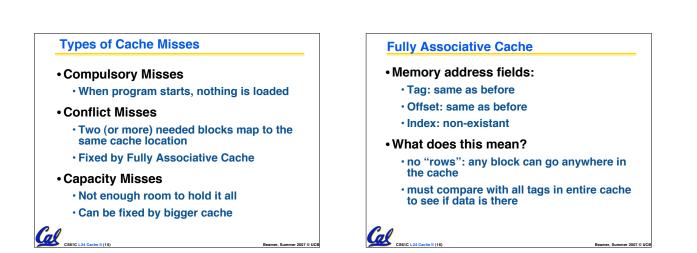

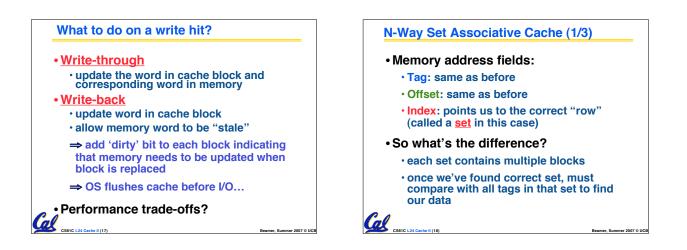

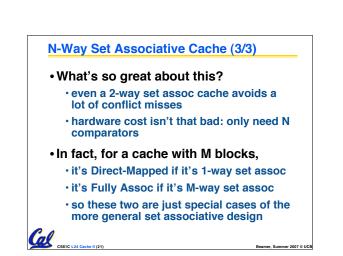

## Block Replacement Policy

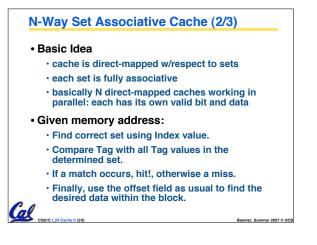

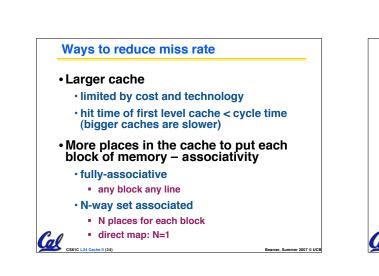

- Direct-Mapped Cache: index completely specifies position which position a block can go in on a miss

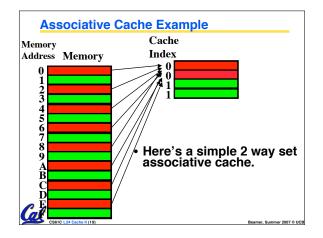

- N-Way Set Assoc: index specifies a set, but block can occupy any position within the set on a miss

- Fully Associative: block can be written into any position

- Question: if we have the choice, where should we write an incoming block?

al

- If there are any locations with valid bit off (empty), then usually write the new block into the first one.

- If all possible locations already have a valid block, we must pick a replacement policy: rule by which we determine which block gets "cached out" on a miss.

2 points extra added for taking survey (still anonymous)

I don't see results until long after grades due

Cal

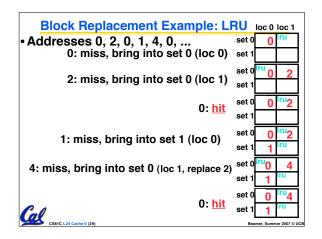

## Block Replacement Policy: LRU LRU (Least Recently Used) Idea: cache out block which has been accessed (read or write) least recently Pro: temporal locality ⇒ recent past use implies likely future use: in fact, this is a very effective policy Con: with 2-way set assoc, easy to keep track (one LRU bit); with 4-way or greater, requires complicated hardware and much time to keep track of this

## **Block Replacement Example**

• We have a 2-way set associative cache with a four word <u>total</u> capacity and one word blocks. We perform the following word accesses (ignore bytes for this problem):

0, 2, 0, 1, 4, 0, 2, 3, 5, 4

How many hits and how many misses will there be for the LRU block replacement policy?

|    | Peer Instructions                                                |    |                            |

|----|------------------------------------------------------------------|----|----------------------------|

|    |                                                                  |    |                            |

|    |                                                                  |    |                            |

|    |                                                                  |    |                            |

|    |                                                                  |    |                            |

|    |                                                                  |    |                            |

| 1. | All caches take advantage of                                     |    | ABC                        |

|    | spatial locality.                                                | 0: | FFF                        |

| 2. | All caches take advantage of temporal locality.                  | 1: | FFT<br>FTF                 |

|    |                                                                  | 3: | FTT                        |

| 3. | On a wood, the veture value will depend as                       | 4: | TFF                        |

| з. | On a read, the return value will depend on what is in the cache. | 5: | TFT                        |

| 1  | A                                                                | 6: | TTF<br>TTT                 |

| a  | CS61C L24 Gache II (40)                                          |    | 1 1 1 1<br>1mer 2007 © UCB |