## **EE105 – Fall 2014 Microelectronic Devices and Circuits**

Prof. Ming C. Wu wu@eecs.berkeley.edu 511 Sutardja Dai Hall (SDH)

Lecture 8: MOSFET (1): physics

1

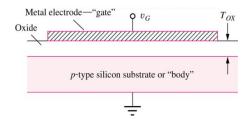

# MOS (Metal-Oxide-Semiconductor) Capacitor Structure

- First electrode Gate: Consists of low-resistivity material such as metal or doped polycrystalline silicon

- Second electrode Substrate or Body: n- or p-type semiconductor

- Dielectric Silicon dioxide: stable high-quality electrical insulator between gate and substrate.

Lecture 8: MOSFET (1): physics

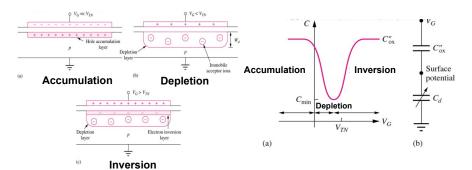

#### **MOS Capacitors in Three Bias Regions**

Threshold voltage:  $V_{TN}$  Gate voltage:  $V_G$

• Accumulation:  $V_G << V_{TN}$

Depletion: V<sub>G</sub> < V<sub>TN</sub>

Inversion: V<sub>G</sub> > V<sub>TN</sub>

Total capacitance modeled as series combination of fixed oxide capacitance and voltage-dependent depletion-layer capacitance.

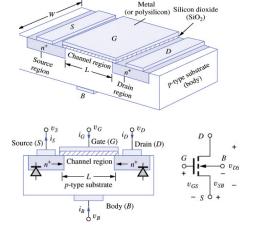

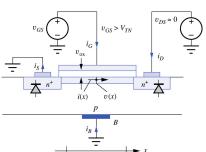

#### **NMOS Transistor Structure**

- 4 device terminals: Gate(G), Drain(D), Source(S) and Body(B).

- Source and drain regions form pn junctions with substrate.

- v<sub>SB</sub>, v<sub>DS</sub> and v<sub>GS</sub> always positive during normal operation.

- v<sub>SB</sub> always < v<sub>DS</sub> and v<sub>GS</sub> to reverse bias pn junctions

## NMOS Transistor: Qualitative I-V Behavior

- V<sub>GS</sub> << V<sub>TN</sub>: Only small leakage current flows.

- V<sub>GS</sub> < V<sub>TN</sub>: Depletion region formed under gate merges with source and drain depletion regions. No current flows between source and drain.

- V<sub>GS</sub> > V<sub>TN</sub>: Channel formed between source and drain. If v<sub>DS</sub> > 0, finite i<sub>D</sub> flows from drain to source.

- $i_B = 0$  and  $i_G = 0$ .

Lecture 8: MOSFET (1): physics

5

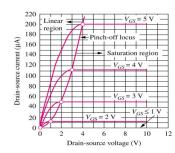

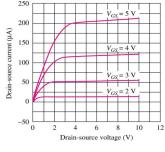

#### NMOS Transistor: Triode Region Characteristics

$$K_n = \mu_n C_{ox}^{"} \left( \frac{W}{I} \right)^{"}$$

$C_{ox}^{"} = \varepsilon_{ox}/T_{ox}$ : oxide capacitance per unit area

$\varepsilon_{ox}$  = oxide permittivity (F/cm)

$T_{ox}$  = oxide thickness (cm)

Cal

Lecture 8: MOSFET (1): physics

Charge per unit length in channel:

$$Q'(x) = -WC''_{ox}(v_{GS} - v(x) - V_{TN})$$

[F/cm]

v(x): voltage of channel at position x

$$i(x) = Q'(x)v_x(x),$$

$v_{r}(x)$ : electron velocity at x

$$v_x(x) = -\mu_n E_x = -\mu_n \frac{dv(x)}{dx}$$

$\mu_n$ : electron mobility

$$\int_{0}^{L} i(x) dx = \int_{0}^{L} W \mu_{n} C_{ox}^{*} (v_{GS} - v(x) - V_{TN}) \frac{dv(x)}{dx} dx$$

$$i_D L = \int_{0}^{v_{DS}} W \mu_n C_{ox}^{"}(v_{GS} - v(x) - V_{TN}) dv(x)$$

$$i_D = K_n \left( v_{GS} - V_{TN} - \frac{v_{DS}}{2} \right) v_{DS}$$

for

$$v_{GS} - V_{TN} \ge v_{DS} \ge 0$$

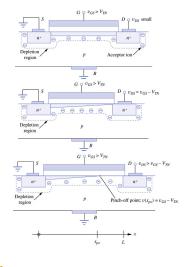

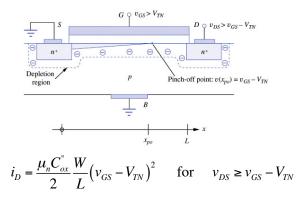

# **NMOS Transistor: Saturation Region**

- If  $v_{DS}$  increases above triode region limit, the channel region disappears and is said to be pinched-off.

- Current saturates at constant value, independent of v<sub>DS</sub>.

- Saturation region operation mostly used for analog amplification.

Lecture 8: MOSFET (1): physics

7

#### NMOS Transistor: Saturation Region (cont.)

$v_{DSAT} = v_{GS} - V_{TN}$  is termed the saturation or pinch-off voltage

Lecture 8: MOSFET (1): physics

#### **Transconductance of an MOS Device**

Transconductance relates the change in drain current to a change in gate-source voltage

$$g_m = \frac{\partial i_D}{\partial v_{GS}}\bigg|_{Q-pi}$$

Taking the derivative of the expression for the drain current in saturation region,

$$g_m = \mu_n C_{ox}^{"} \frac{W}{L} (V_{GS} - V_{TN}) = \frac{2I_D}{V_{GS} - V_{TN}}$$

Lecture 8: MOSFET (1): physics

9

### **Channel-Length Modulation**

- $\begin{array}{c|c} & v_{GS} & v_{DS} \\ \hline & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$

- As  $v_{DS}$  increases above  $v_{DSAT}$ , the length of the depleted channel beyond the pinch-off point, DL, increases and the actual L decreases.

- i<sub>D</sub> increases slightly with v<sub>DS</sub> instead of being constant.

$$i_D = \frac{\mu_n C_{ox}^{"}}{2} \frac{W}{L} (v_{GS} - V_{TN})^2 (1 + \lambda v_{DS})$$

λ = channel length modulation parameter

Lecture 8: MOSEET (1): physics

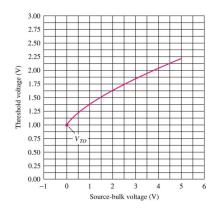

#### **Body Effect or Substrate Sensitivity**

Non-zero v<sub>SB</sub> changes threshold voltage, causing substrate sensitivity modeled by

$$V_{TN} = V_{TO} + \gamma \left( \sqrt{v_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right)$$

where

$V_{TO}$  = threshold voltage for  $v_{SB}$  = 0

$$\gamma = \text{body} - \text{effect parameter } \left(\sqrt{V}\right)$$

$$2\phi_F$$

= surface potential (V)

Lecture 8: MOSFET (1): physics

11

### **NMOS Model Summary**

#### NMOS TRANSISTOR MATHEMATICAL MODEL SUMMARY

Equations (4.24) through (4.28) represent the complete model for the i-v behavior of the NMOS transistor.

For all regions,

$$K_n = K'_n \frac{W}{L}$$

$K'_n = \mu_n C''_{ox}$   $i_G = 0$   $i_B = 0$

Cutoff region:

$$i_D = 0$$

for  $v_{GS} \le V_{TN}$  (4.25)

Triode region:

$$i_D = K_n \left( v_{GS} - V_{TN} - \frac{v_{DS}}{2} \right) v_{DS} \quad \text{for } v_{GS} - V_{TN} \ge v_{DS} \ge 0$$

(4.26)

Saturation region:

$$i_D = \frac{K_n}{2} (v_{GS} - V_{TN})^2 (1 + \lambda v_{DS})$$

for  $v_{DS} \ge (v_{GS} - V_{TN}) \ge 0$  (4.27)

Threshold voltage:

$$V_{TN} = V_{TO} + \gamma \left( \sqrt{v_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right) \tag{4.28}$$

$V_{TN}>0$  for enhancement-mode NMOS transistors. Depletion-mode NMOS devices can also be fabricated, and  $V_{TN}\leq 0$  for these transistors.

SFET (1): physics

(4.24)

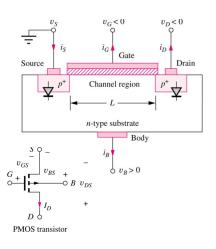

## PMOS Transistors: Enhancement-Mode Structure

- p-type source and drain regions in an n-type substrate.

- v<sub>GS</sub> < 0 required to create p-type inversion layer in channel region

- For current flow,  $v_{GS} < V_{TP}$

- To maintain reverse bias on source-substrate and drain -substrate junctions,  $v_{SB} < 0$  and  $v_{DB} < 0$

- Positive bulk-source potential causes V<sub>TP</sub> to become more negative

Lecture 8: MOSFET (1): physics

13

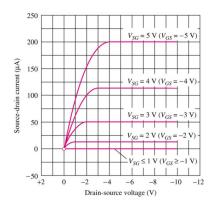

# **PMOS Transistors: Output Characteristics**

- For  $v_{GS} > V_{TP}$ , transistor is off.

- For more negative  $v_{\rm GS}$ , drain current increases in magnitude.

- PMOS device is in the triode region for small values of V<sub>DS</sub> and in saturation for larger values.

- Remember V<sub>TP</sub> < 0 for an enhancement mode transistor</li>

Lecture 8: MOSFET (1): physics

**BSAC**

### **PMOS Model Summary**

#### PMOS TRANSISTOR MATHEMATICAL MODEL SUMMARY

Equations (4.29) through (4.33) represent the complete model for the *i-v* behavior of the PMOS transistor

For all regions,

$$K_p = K'_p \frac{W}{L}$$

$K'_p = \mu_p C''_{ox}$   $i_G = 0$   $i_B = 0$  (4.29)

Cutoff region:

$$i_D = 0$$

for  $V_{GS} \ge V_{TP}$  (4.30)

Hou

$$i_D = K_p \left( v_{GS} - V_{TP} - \frac{v_{DS}}{2} \right) v_{DS} \quad \text{for } 0 \le |v_{DS}| \le |v_{GS} - V_{TP}|$$

(4.31)

Saturation region:

$$i_D = \frac{K_p}{2} (v_{GS} - V_{TP})^2 (1 + \lambda |v_{DS}|) \quad \text{for } |v_{DS}| \ge |v_{GS} - V_{TP}| \ge 0$$

(4.32)

Threshold voltage:

$$V_{TP} = V_{TO} - \gamma \left( \sqrt{v_{BS} + 2\phi_F} - \sqrt{2\phi_F} \right) \tag{4.33}$$

For the enhancement-mode PMOS transistor,  $V_{TP} < 0$ . Depletion-mode PMOS devices can also be fabricated;  $V_{TP} \geq 0$  for these devices.

Lecture 8: MOSFET (1): physics