## FINAL SOLUTIONS

Problem 1 of 4: Answer each question briefly and clearly. (3 points each, total 24)

What type of electrical current (drift or diffusion?) and what type of carriers (holes or electrons?) flows between the source and the drain of an n-channel MOS transistor?

Where is the maximum absolute electric field within an MOS capacitor in depletion, made of Al, Si0<sub>2</sub> and p-type doped Silicon? (Mark your answer on the graph and give brief explanation)

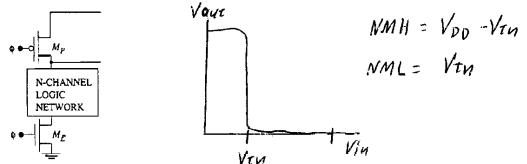

What are the noise margins of a dynamic logic gate that employs an n-channel logic network?

What physical aspect of a planar bipolar transistor determines its Early Voltage value?

The width of the base (through the phenomenon human as "base width" modulation)

Is it important to build a current supply source with an extremely high output resistance when biasing a common collector amplifier? Explain your answer.

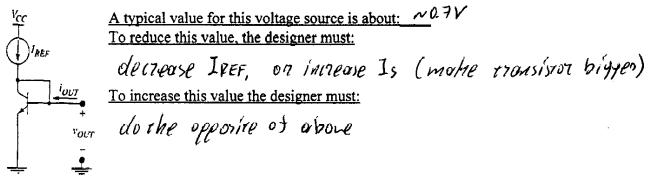

What can a circuit designer do to adjust the output voltage of the following npn bipolar diodeconnected voltage source?

What single-stage amplifiers suffer from the so-called "Miller effect" that limits their frequency response?

What is the definition of the common-mode rejection ratio of a differential amplifier?

## Problem 2 of 4 (26 points)

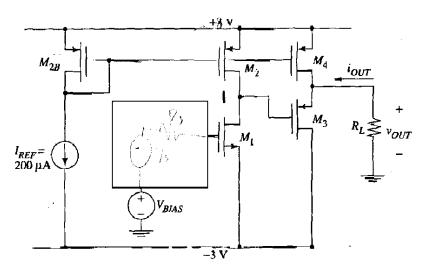

Below is given a voltage amplifier with  $(W/L)_1 = 50/2$ ,  $(W/L)_3 = 100/2$  and  $(W/L)_{2B} = (W/L)_2 = (W/L)_4 = 50/4$ . Assume that all backgates are shorted to their respective sources. Assume that  $V_{BIAS}$  is set such that all devices are operating in their constant current region.

Fall 1998

For each of the following questions, make sure that you show the expressions <u>before</u> you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

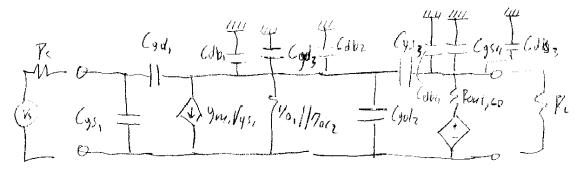

a) Draw the small signal model for the CS-CD stages, including parasitic capacitances. (5 points)

b) Draw the two-port model of this CS-CD stage and calculate the following parameters:  $A_V$  (i.e. unloaded DC voltage gain of the entire amplifier), Rin and Rout. Also calculate the DC voltage gain  $v_{out}/v_s$  when  $R_s = 5k\Omega$  and  $R_L = 500\Omega$ . (5 points)

c) Find the  $\omega_{3db}$  for this amplifier using the method of open-circuit time constants. (Hint #1: make sure that you include these parasitic capacitances:  $C_{gs1}$ ,  $C_{gd1}$ ,  $C_{db1}$ ,  $C_{db2}$ ,  $C_{gd3}$ ,  $C_{gs3}$ ,  $C_{db3}$  and  $C_{db4}$ . Hint #2: all these capacitances combine to *five* distinct capacitances, for which you will then have to calculate the open circuit time constants.) Answer this question in the following four steps:

c1) From part (a), combine all these capacitances to the following five, and calculate their values.

(3 points)

$$C_{gs1} = \frac{2}{3} W_1 L_1 (0 \times + (0 \vee_1 W_1) = \frac{2}{3} \times 50 \times 2 \times 7.3 + 50 \times 20.5 = \boxed{178 fF}$$

C<sub>1</sub> (capacitance between ground and node "1") =

$$C_{ab1} + C_{gd3} + C_{ab2} + C_{gd2} = 61 + 112 + 50 + 5 = 249 fF$$

$$C_{ab1} = W_1 L_{diffn} C_{jn} + W_{+2} L_{diffn} C_{jswn} = 50 \times 6 \times 0.1 + (50 + 12) \times 0.5 = 61 fF$$

$$C_{ab2} = C_{ab4} = 50 \times 6 \times 0.3 + (50 + 12) \times 0.75 = 112 fF$$

$$C_{gs3} = \frac{(362 \pm (364 \pm 30 \times 6 \times 6.5 \pm 50 + 12) \times 0.75 \pm 112 fF}{\frac{2}{3} W_3 L_3 C_{0x} + W_3 C_{0xp} = \frac{2}{3} \times 100 \times 2.3 + 100 \times 0.5 \pm 357 fF}$$

$$C_L = (354 + (954 + (353 = 112 + 3)2 + 219 = 663 FF)$$

$(954 = \frac{2}{3} \cdot 50 \times 4 \times 1.3 + 50 \times 0.5 = 332 FF$

(26.3 =  $(00 \times 6 \times 6.3 + (100 + 12) \times 0.35 = 219 \text{ } FF$  c2) Calculate the resistance "seen" by each of the above capacitances. (2 points)

$$R_{71} = Y_{01} || Y_{002} = | \overline{66.7 \text{ ks}} |$$

$$R_{71} = Y_{01} || Y_{002} = | \overline{66.7 \text{ ks}} |$$

$$= 66.7 \text{ k} \left( 1 - \frac{500}{1.41 \text{ k + 500}} \right) + 1.41 \text{ k /1 } .500 = | 49.6 \text{ k s} |$$

c3) Calculate the dominant pole for the circuit. (1 point)  $RT_{,L} = RL // \frac{1}{9m_3} = \frac{369 \Omega}{369 \Omega}$

45

0

-45

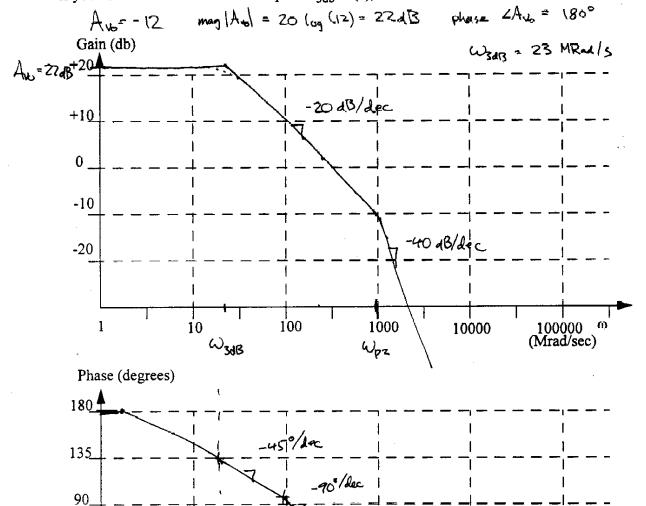

- d) Assuming that, in addition to the dominant pole you found in part c, this amplifier has a second pole at 1000Mrad/sec, draw the amplitude and phase diagrams. (5 points)

- If you could not find the loaded DC voltage gain in (b), assume it is -20V/V and check here:  $\Box$  If you could not find the dominant pole  $\omega_{3db}$  in (c), assume it is 30Mrad/s and check this box:  $\Box$

100

10

1000

10000

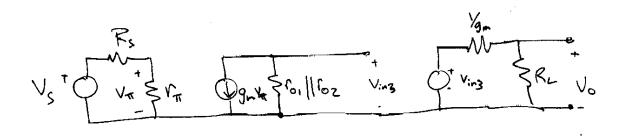

100000 ω (Mrad/sec) e) Quite frankly, this is not a very good amplifier, so go ahead and replace  $M_1$  with an npn bipolar transistor, redraw the circuit and calculate the new loaded DC voltage gain. (5 points)

$$R_{S} = 5k \qquad g_{m} = \frac{200 \, \text{M}}{.0259} = .0077 \, \text{S}$$

$$R_{C} = 5000 \, \text{L}$$

$$V_{TI} = \frac{B}{g_{m_{I}}} = \frac{100}{.0077} = 13 \, \text{k}$$

$$V_{TI} = \frac{V_{A}}{I_{C}} = \frac{25V}{200 \, \text{M}} = 125k$$

$$\lambda = 0.1 \, \text{Vium}$$

$$\lambda = .025 \, \text{V}^{-1}$$

$$G_{DI} = \frac{1}{\sqrt{1}} = \frac{1}{\sqrt{1}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 10^{-6} \cdot 50 \cdot 200 \, \text{M}}} = \frac{1}{\sqrt{2.25 \cdot 1$$

$$A_{V} = \frac{13k}{18k} \cdot -.0077 \cdot \left( \frac{200k \cdot 125k}{200k \cdot 125k} \right) \cdot \frac{500}{500 + 1414}$$

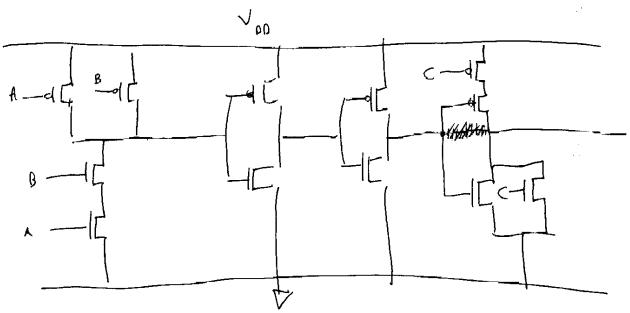

## Problem 3 of 4 (25 points)

Consider the following static CMOS logic circuit. The two capacitances on the schematic represent the capacitance of the wiring connecting these gates.

For each of the following questions, make sure that you show the expressions <u>before</u> you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

$$\begin{array}{c|c}

A & & \\

B & & \\

\hline

&$$

a) Write the logical expression for Q in terms of A, B and C, and fill out the truth table. (3 points)

| A | В | C | Q  |

|---|---|---|----|

| 0 | 0 | 0 | o  |

| 0 | 1 | 0 | 0  |

| 1 | 0 | 0 | Q. |

| 1 | 1 | 0 | (  |

| 0 | 0 | 1 | Q  |

| 0 | 1 | 1 | 6  |

| 1 | 0 | 1 | 9  |

| 1 | 1 | 1 | 0  |

b) Re-draw this circuit showing all the transistors that implement the logical functions depicted above in CMOS static logic, using a 5V supply voltage. (4 points)

c) All transistors have a channel length  $L=2\mu m$ . The widths of the n-channel transistors for the inverters and logic gates are as follows:

NAND gate:  $W_n = 4\mu m$ , Inverter 1:  $W_n = 6\mu m$ , Inverter 2:  $W_n = 18\mu m$ , NOR gate:  $W_n = 4\mu m$ . Determine the widths of the p-channel transistors in the circuit such that the inverters have equal propagation delays  $t_{PHL} = t_{PLH}$  and that the logic gates have equal worst-case propagation delays. (6 points)

d) Find the numerical value of the worst-case propagation delay  $t_p$  for the NAND gate. The drain-bulk capacitances can be neglected because of the large wire capacitance. (But do take into account the effect of the gate capacitance through  $C_{ox}$ !)(6 points)

$$\begin{array}{l}

+_{\rho LH} = \frac{\left(C_{w} + C_{G}\right) \left(\frac{V_{\rho \rho}}{2}\right)}{\frac{1}{2} \left(\frac{\omega}{2L}\right) \mu_{n} \left(o_{X} \left(V_{\rho \rho} - V_{T_{n}}\right)^{2}}{\frac{1}{2} \left(\frac{\omega}{2L}\right) \mu_{n} \left(o_{X} \left(V_{\rho \rho} - V_{T_{n}}\right)^{2}}\right) \\

C_{G} = C_{kinvl} = C_{a_{X}} \left(\omega_{n} L_{n} + \omega_{p} L_{\rho}\right) = 2.3 f\left(6.2 + 17.2\right) = 82.8 f\\

C_{w} = 250 f\\

\Rightarrow +_{\rho LH} = \frac{332.8 \left(2.5\right)}{\frac{1}{2} \left(\frac{4}{4}\right) 50 \mu \left(\frac{4}{4}\right)^{2}} = 2.08 \text{ ns}

\end{array}$$

e) Find the numerical value of the propagation delay t<sub>p</sub> from the input to Inverter 1 to the output of Inverter 2. The drain-bulk capacitance can be neglected because of the large wire capacitance (Again, do take into account the gate capacitances of the driven gates). (6 points)

## Problem 4 of 4 (25 points)

Consider the following circuit. Note that this is NOT a common gate amplifier, since the transistor is only going to be operating in the *triode* region.

$$C_1 = 100 \text{pF} \left( = 10^5 \text{fF} \right)$$

$$V_S = ImV \cos(\omega t)$$

$$M_1 = \frac{50/2}{2 \times 5V}$$

$$V_S = ImV \cos(\omega t)$$

a) Note that this transistor is operating in the triode region and is playing the role of a variable resistor. Calculate the sheet resistance of the channel of this transistor, as a function of  $V_{GS}$ . Do this calculation for  $V_{GS}$  values of 2, 3, and 5V. (5 points)

TRIODE EQ. ID =

$$\frac{W}{U}$$

unlox  $\frac{(Vgs-VT)-VDS}{VDS}$   $\frac{VDS}{VDS}$   $\frac{(HAVDS)}{VDS}$  REMEMBER FROM LAB

IDTERIODE  $\sim \frac{(W)}{U}$ , unlox  $\frac{(Vgs-VT)}{VDS}$  FOR  $\frac{VDS}{VDS}$   $\sim \frac{1}{(W)}$ , unlox  $\frac{(Vgs-VT)}{U}$   $\sim \frac{1}{(W)}$ , unlox  $\frac{(Vgs-VT)}{U}$   $\sim \frac{1}{(W)}$ , unlox  $\frac{(Vgs-VT)}{U}$   $\sim \frac{1}{(W)}$   $\sim \frac{1}{$

| V <sub>GS</sub> (V) | R <sub>□</sub> (Ohms/□) |

|---------------------|-------------------------|

| 2                   | 20-103                  |

| 3                   | 10 · 103                |

| 5                   | 5.103                   |

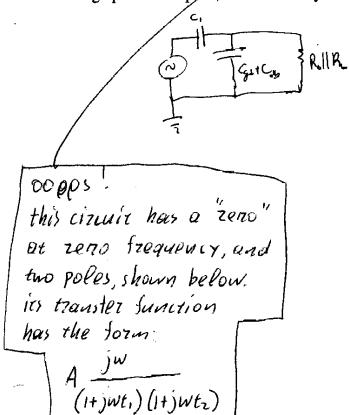

$C_{i}$

b) Given that the size of this transistor is 50/2, calculate the equivalent small signal channel resistance for its channel. (Hint: the small channel resistance in this case is NOT determined by the  $\lambda$  of the transistor!). (5 points)

R=RDL (A LOT OF PEOPLE USED R=RD W

THIS IS A NO-NO)

$$L = \frac{2}{50} \Rightarrow .04$$

$$R(2v) = \frac{20.10^{3}.04}{20.04} \Rightarrow 800.01$$

R(SV): 10.103,04 => 4001 R(SV): 5.103,04 => 2001

| V <sub>GS</sub> (V) | r <sub>channel</sub> (Ohms) |

|---------------------|-----------------------------|

| 2                   | 800A                        |

| 3                   | 400 A                       |

| 5                   | 200.1                       |

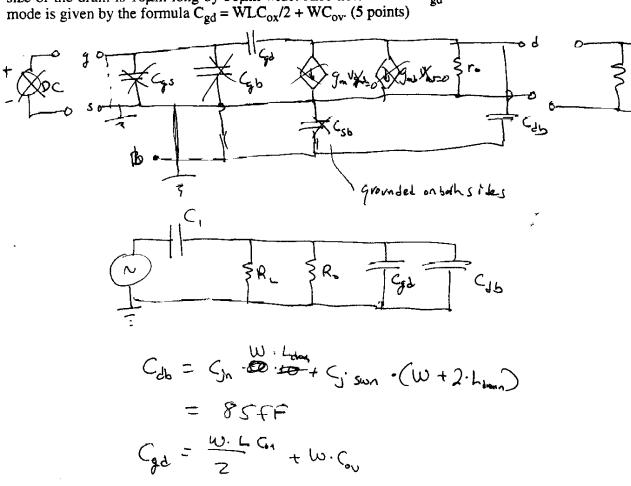

c) Write the small signal model and include and calculate the parasitic capacitances. Note that the size of the drain is  $10\mu m$  long by  $50\mu m$  wide. Also note that the  $C_{gd}$  for a transistor in a triode mode is given by the formula  $C_{gd} = WLC_{ox}/2 + WC_{ox}$ . (5 points)

= 180f F

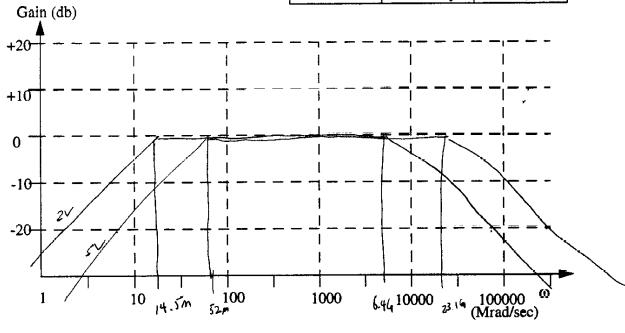

d) Calculate the first pole and first zero for this circuit for  $V_{GS}$  values of 2 and 5 volts and draw the two voltage transfer characteristics versus frequency for each value of  $V_{GS}$ . (Use the same graph for both plots, but make sure you mark each carefully.) (5 points)

14 of 15

pde at (RollRe)(Con + Cub)

pde ut 6.44 G rat 14.5 M ray 14.5 M ray pole ut 23.1 G rat 52 M rat 52 M rat

| Parameter  | Value when V <sub>GS</sub> = 2V | Value when $V_{GS} = 5V$ |

|------------|---------------------------------|--------------------------|

| first zero | <u>—(1)</u>                     | — ( <sub>1</sub> )       |

| first pole | 14.5 M. 500                     | 52 May                   |

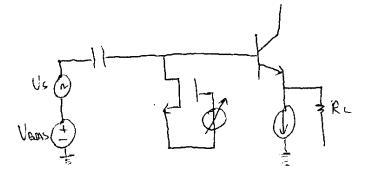

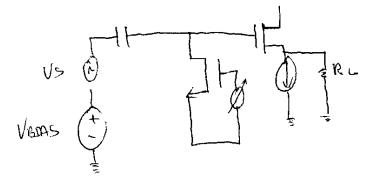

e) What amplifier stage would you consider adding between this filter and the load in order to make the frequency response of the entire circuit largely independent of the value of the load? (Note that you have to use a transistor type and an amplifier stage that will not limit the high frequency response of this filter). Draw the new circuit and explain your choice. (5 points)

WE WANT:

- 1) BUFFERING, SPECIFICALLY VOLTAGE BUFFERRING

- 2) LARGE INPUT RESISTANCE, SMALL OUTPUT RESISTANCE AND MO MILLER EFFECT TO LIMIT BANDWINTH

Common - Collecter

Common - Drain