### Lecture 33

- Last time:

- Frequency response of voltage and current buffers

- Voltage/Current sources using MOS transistors

- Today :

- Improved current sources

- Current mirrors

## Equivalent Circuit for I-Source

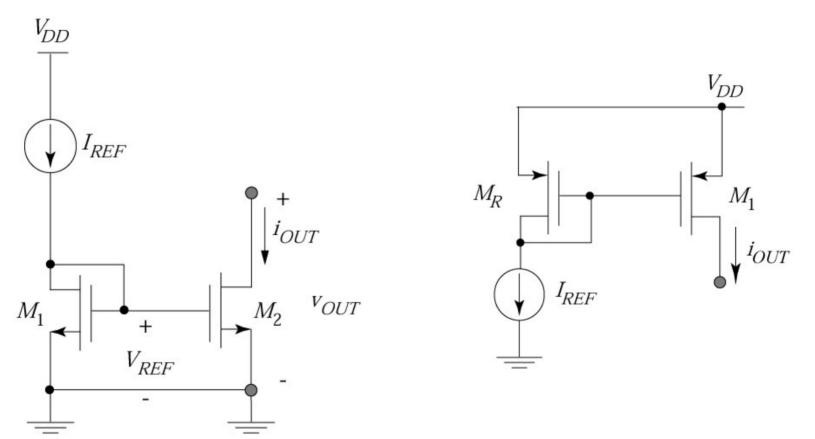

Find the DC current for "gray circle" equivalent circuit

$$I_{OUT} = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right)_2 (V_{REF} - V_{Tn})^2 \quad \text{Substitute for } V_{REF}$$

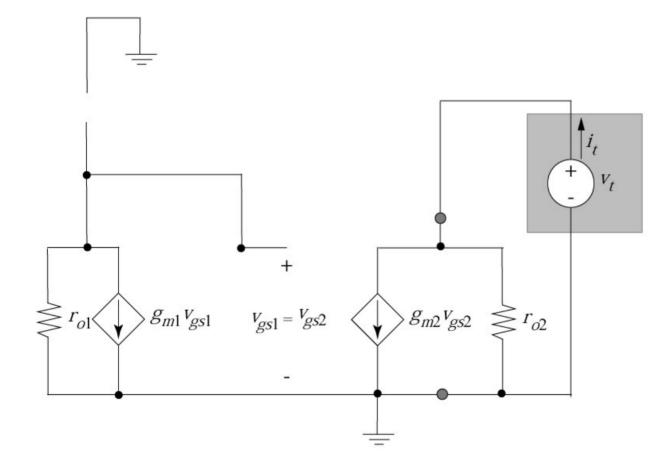

#### Small-Signal Resistance of *I*-Source

## Improved Current Sources

Goal: increase  $r_{oc}$ Approach: look at *amplifier* (?) output resistance results ... to see topologies that boost resistance

University of California at Berkeley

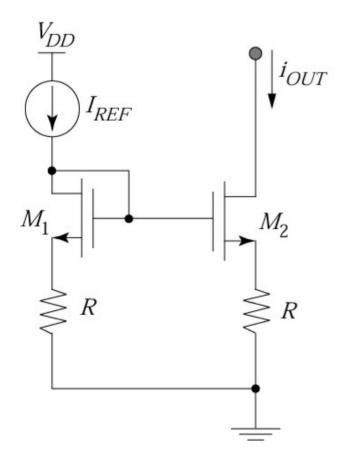

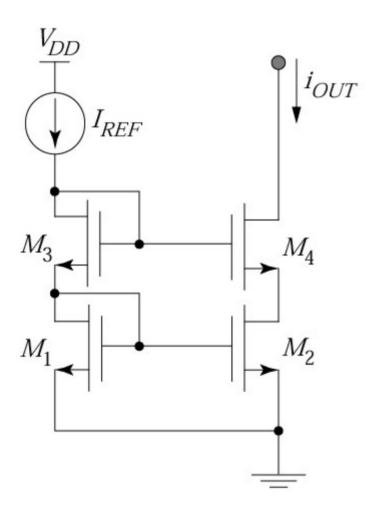

#### Cascode (or Stacked) Current Source

Insight:  $V_{GS2}$  = constant AND  $V_{DS2}$  = constant

Small-Signal Resistance  $r_{oc}$ :

University of California at Berkeley

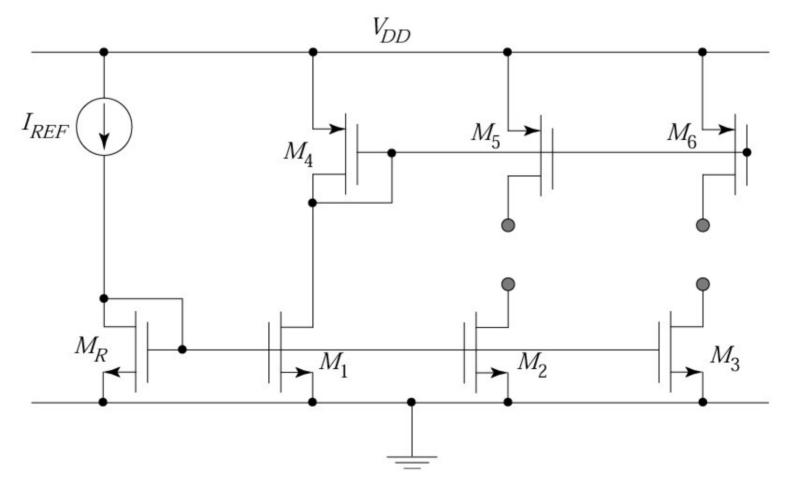

# Drawback of Cascode I-Source

Minimum output voltage for all transistors saturated:

$$V_{OUT,MIN} = V_{DS4,SAT} + V_{S4} = V_{DS4,SAT} + V_{GS2}$$

# Current Sinks and Sources

Sink: output current goesSource: output current comesto groundfrom voltage supply

## **Current Mirrors**

*Idea*: we only need one reference current to set up all the current sources and sinks needed for a multistage amplifier.

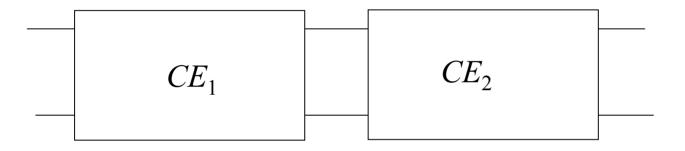

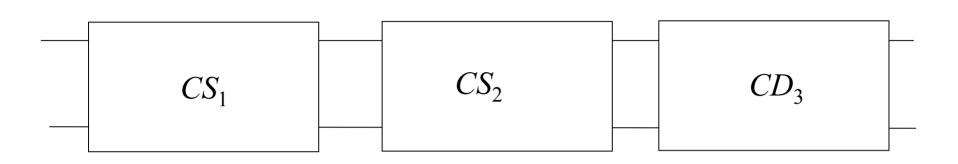

# Multistage Amplifiers

Necessary to meet typical specifications for any of the 4 types

We have 2 flavors (NMOS, PMOS) of CS, CG, and CD and the npn versions of CE, CB, and CC (for a BiCMOS process)

What are the constraints?

1. Input/output resistance matching

2. DC coupling (no passive elements to block the signal)

#### Start: Two-Stage Voltage Amplifier

• Use two-port models to explore whether the combination "works"

Results:

$$R_{in} = R_{in1}, R_{out} = R_{out2}, A_v =$$

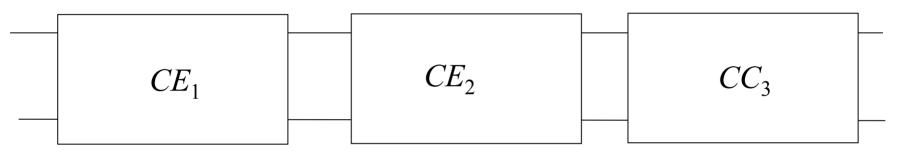

# Add a Third Stage: CC

Goal: reduce the output resistance (important spec. for a voltage amp)

Output resistance:

# Using CMOS Stages

#### Input resistance:

Voltage gain (2-port parameter):

Output resistance: