# Chapter 3

# Silicon Device Fabrication Technology

Over 10<sup>15</sup> transistors (or 100,000 for every person in the world) are manufactured every year.

VLSI (Very Large Scale Integration) ULSI (Ultra Large Scale Integration)

Variations of this versatile technology are used for flat-panel displays, micro-electro-mechanical systems (*MEMS*), and even DNA chips for DNA screening...

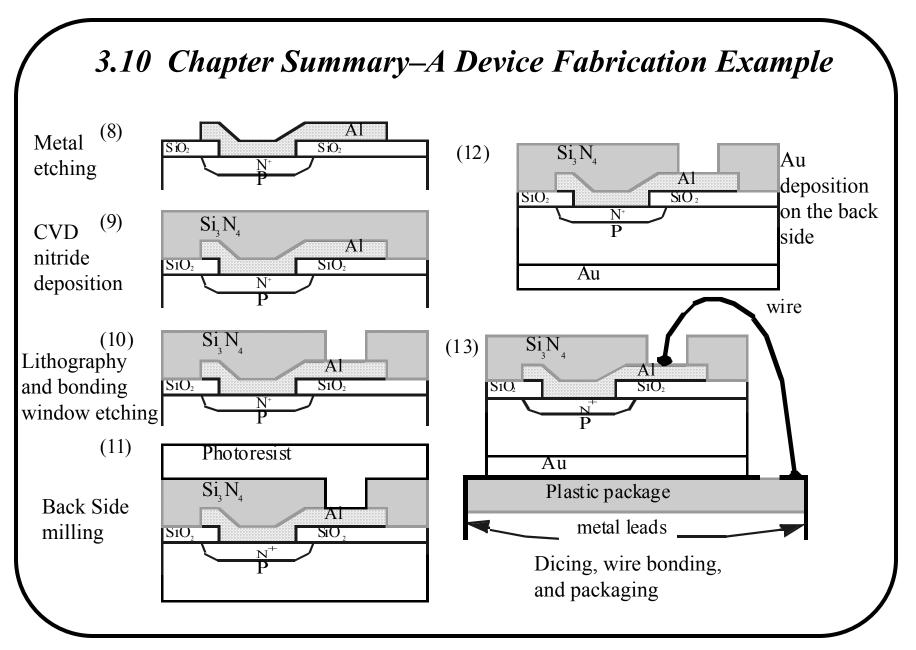

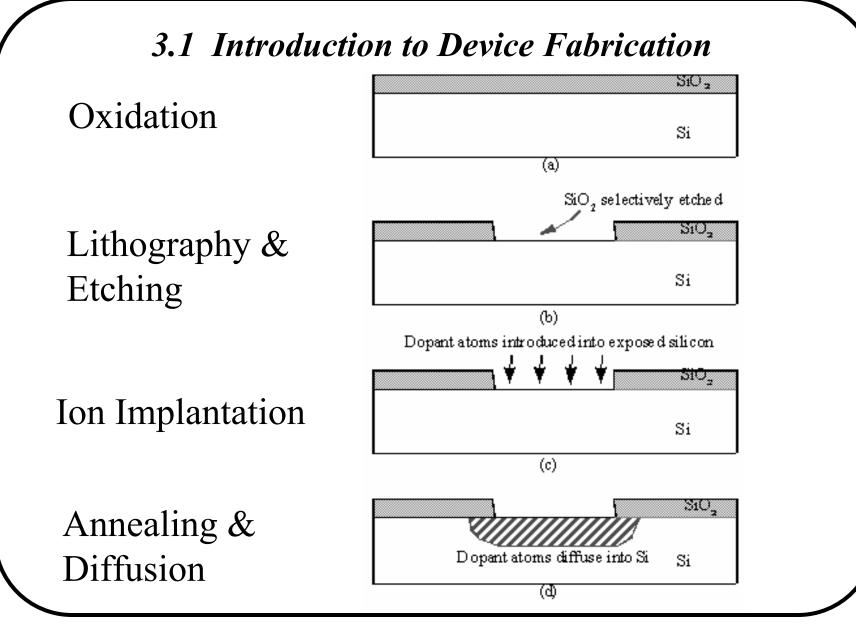

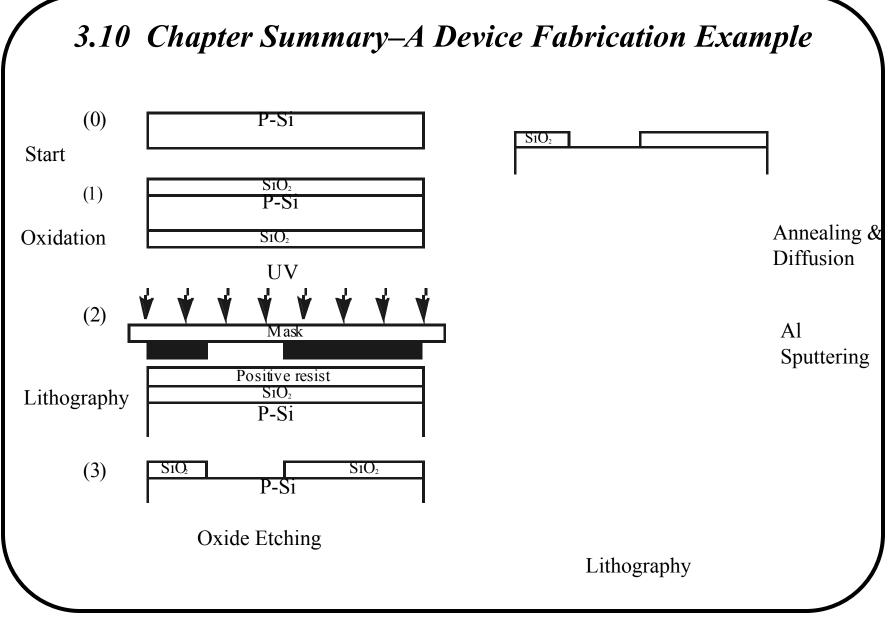

#### 3.2 Oxidation of Silicon

Dry Oxidation :

$Si + O_2 \rightarrow SiO_2$

Wet Oxidation :

$Si + 2H_2O \rightarrow SiO_2 + 2H_2$

Semiconductor Devices for Integrated Circuits (C. Hu)

## 3.2 Oxidation of Silicon

**EXAMPLE : Sequential Oxidation**

(a) How long does it take to grow  $0.1 \mu m$  of dry oxide at  $1000 \, {}^{\circ}C$ ?

(b) After step (a), how long will it take to grow an additional  $0.2 \mu m$  of oxide at 900 °C in a wet ambient ?

#### Solution:

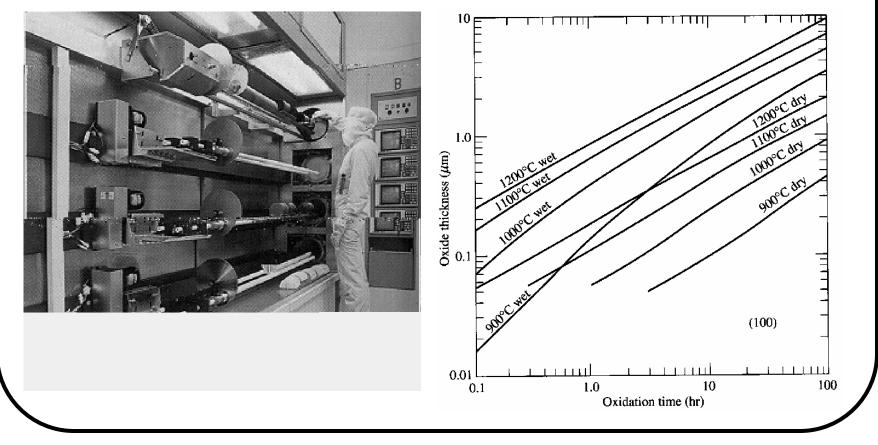

(a) From the "1000°C dry" curve in Slide 3-3, it takes 2.5 hr to grow 0.1 μm of oxide.

(b) Use the "900°C wet" curve only. It would have taken 0.7hr to grow the 0.1 μm oxide and 2.4hr to grow 0.3 μm oxide from bare silicon. The answer is 2.4hr–0.7hr = 1.7hr.

Semiconductor Devices for Integrated Circuits (C. Hu)

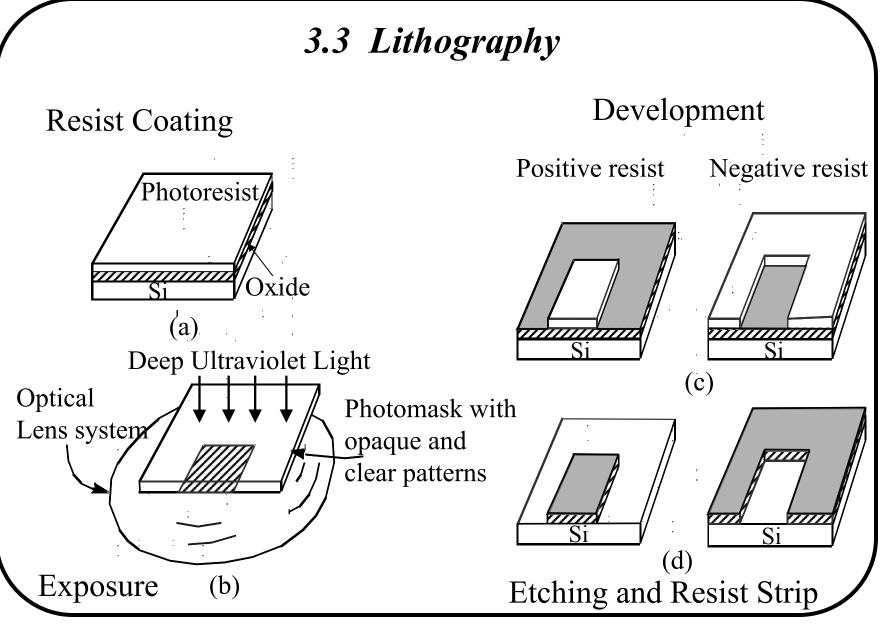

## 3.3 Lithography

#### Wafers are being loaded into a stepper in a clean room.

Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 3-8

# 3.3 Lithography

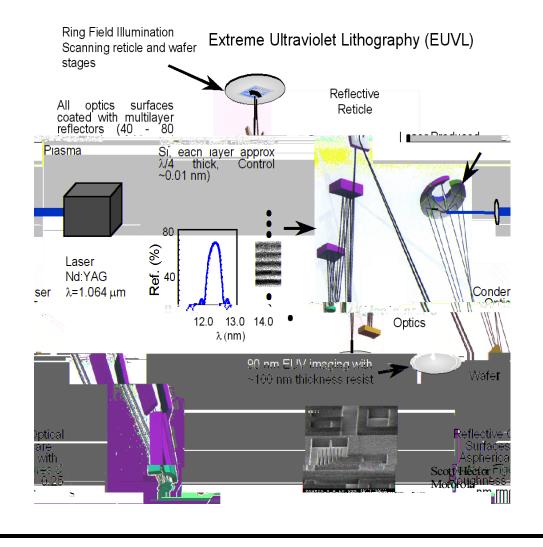

Advanced Lithography Technology

- *Electron Projection Lithography* : Exposes a complex pattern using mask and electron lens as is done in optical lithography.

- *Extreme UV Lithography* : Uses 13 nm wavelength (used to be called soft x-ray lithography).

### Extreme UV Lithography

Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 3-10

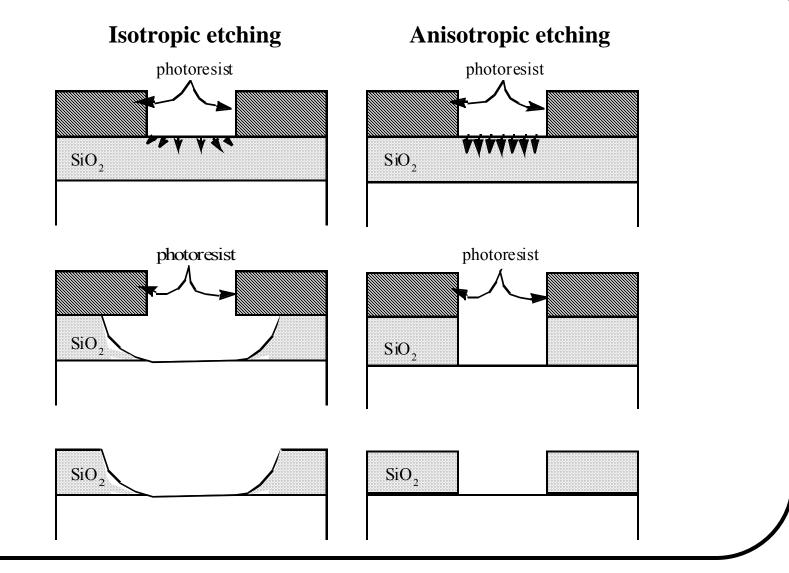

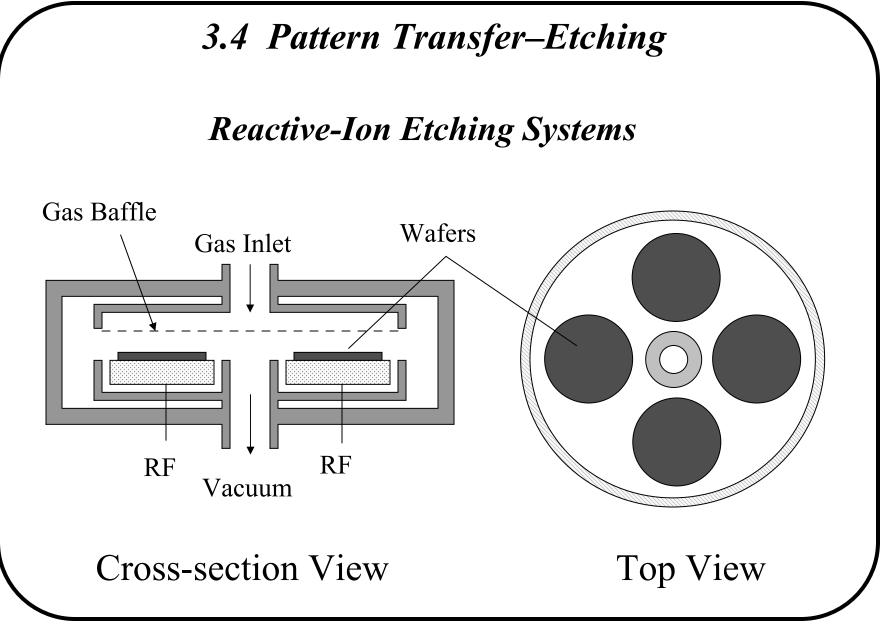

#### 3.4 Pattern Transfer–Etching

Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 3-11

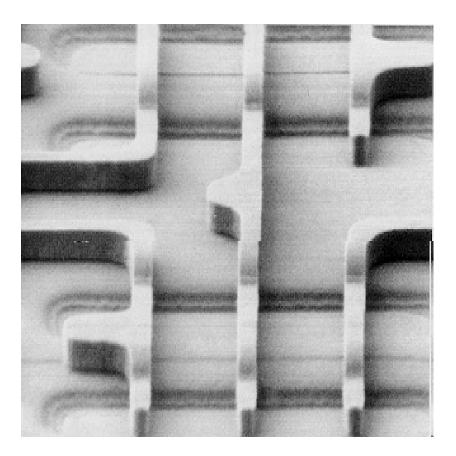

Scanning electron microscope view of a plasma-etched 0.16 µm pattern in polycrystalline silicon film.

Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 3-13

# 3.4 Pattern Transfer–Etching

Dry Etching (also known as Plasma Etching, or Reactive-Ion Etching) is anisotropic.

- Silicon and its compounds can be etched by plasmas containing F.

- Aluminum can be etched by Cl.

- Some concerns :

- Selectivity and End-Point Detection

- Plasma Process-Induced Damage or Wafer Charging Damage and Antenna Effect

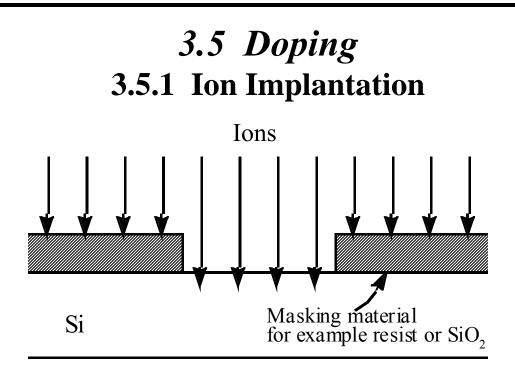

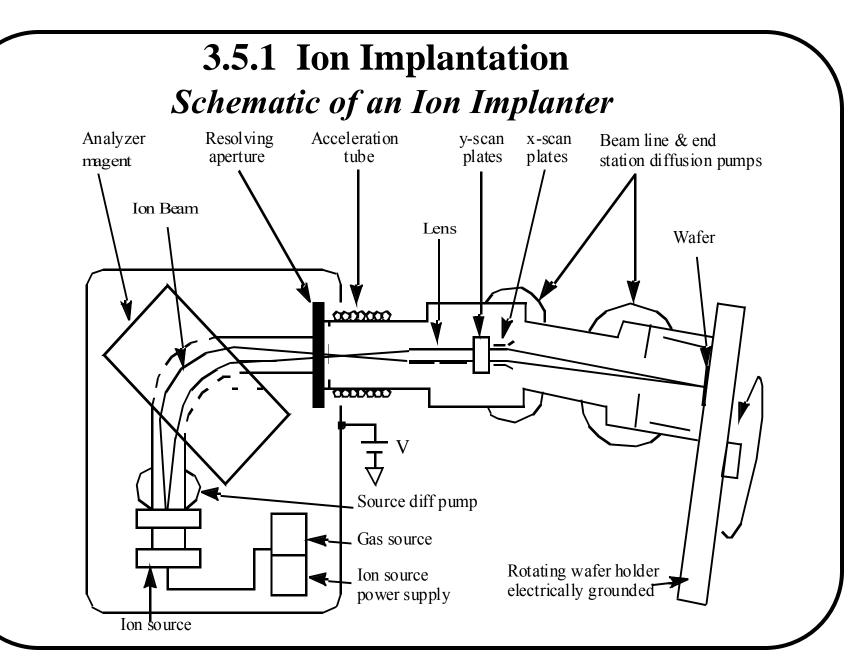

- The dominant doping method

- Excellent control of **dose** (cm<sup>-2</sup>)

- Good control of implant depth with energy (KeV to MeV)

- Repairing crystal damage and dopant activation requires annealing, which can cause dopant diffusion and loss of depth control.

# **3.5.1 Ion implantation**

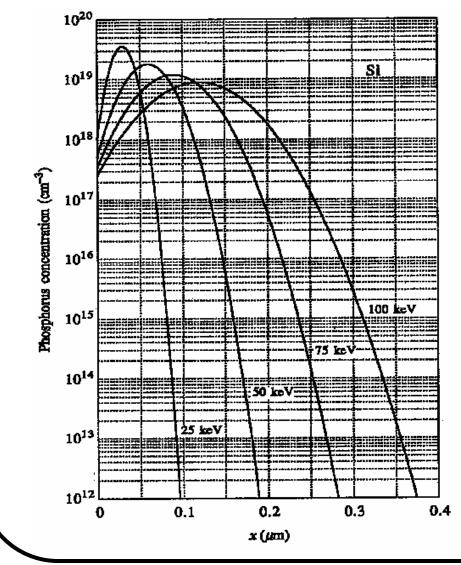

## Phosphorous Density Profile after Implantation

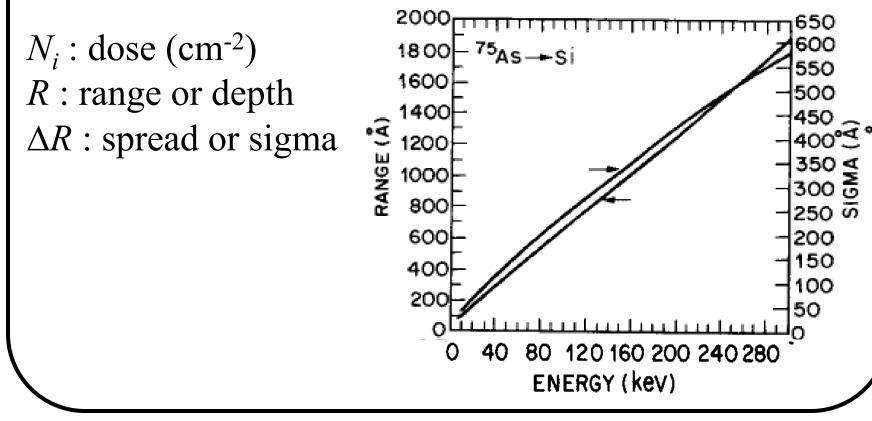

# **3.5.1 Ion Implantation** *Model of Implantation Doping Profile (Gaussian)*

$$N(x) = \frac{N_i}{\sqrt{2\pi} \cdot (\Delta R)} \cdot e^{-(x-R)^2/2\Delta R^2}$$

Slide 3-18

# 3.5 Doping

#### **Other Doping Methods**

- *Gas-Phase Doping* : Used to dope Si with P using  $POCl_3$ .

- *Solid-Source Doping* : Dopant diffuses from a doped solid film (SiGe or oxide) into Si.

- *In-Situ Doping* : Used to dope deposited films during film deposition.

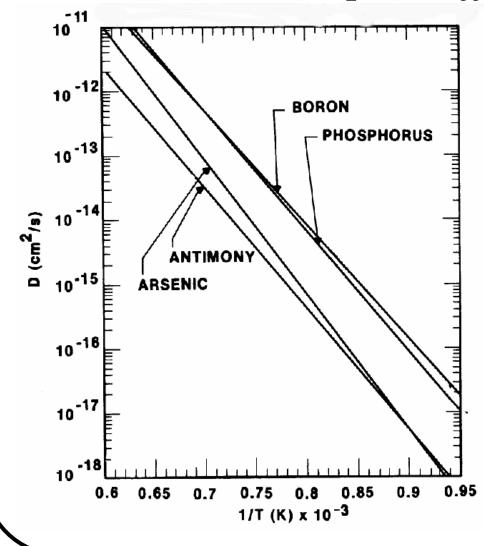

### 3.6 Dopant Diffusion

*D* increases with increasing temperature.

Some applications need very deep junctions (high *T*, long *t*). Others need very shallow junctions (low *T*, short *t*).

Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 3-21

# 3.6 Dopant Diffusion

#### Shallow Junction and Rapid Thermal Annealing

• After ion implantation, thermal annealing is required. Furnace annealing causes too much diffusion of dopant for some applications.

• In rapid thermal annealing (RTA), the wafer is heated to high temperature in seconds by a bank of heat lamps.

Also RTO (oxidation), RTCVD (chemical vapor deposition), RTP (processing).

Slide 3-23

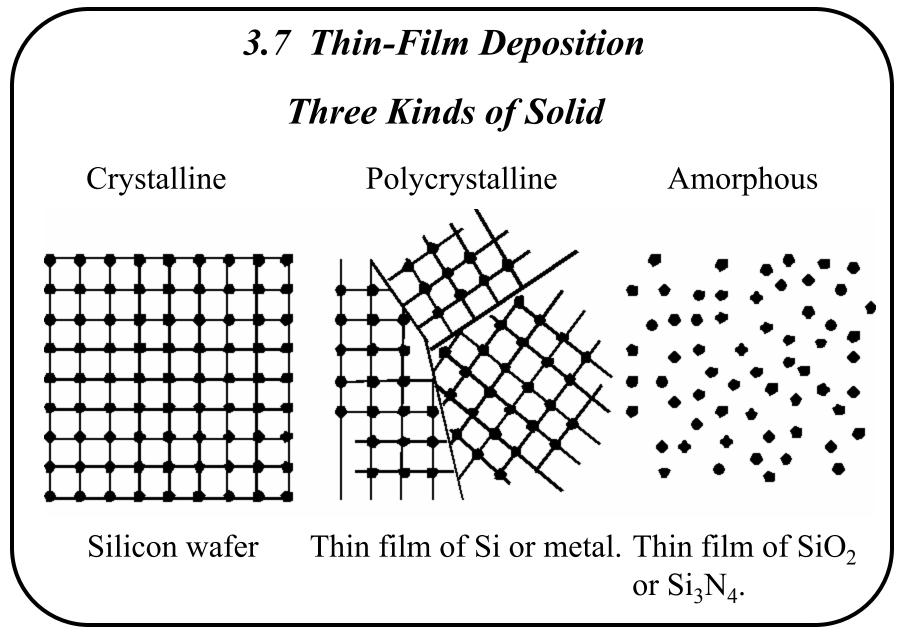

### 3.7 Thin-Film Deposition

- Metal layers for device interconnect

- Inter-metal dielectric

- Poly-Si for transistor gate

- Barrier against interdiffusion

- Encapsulation

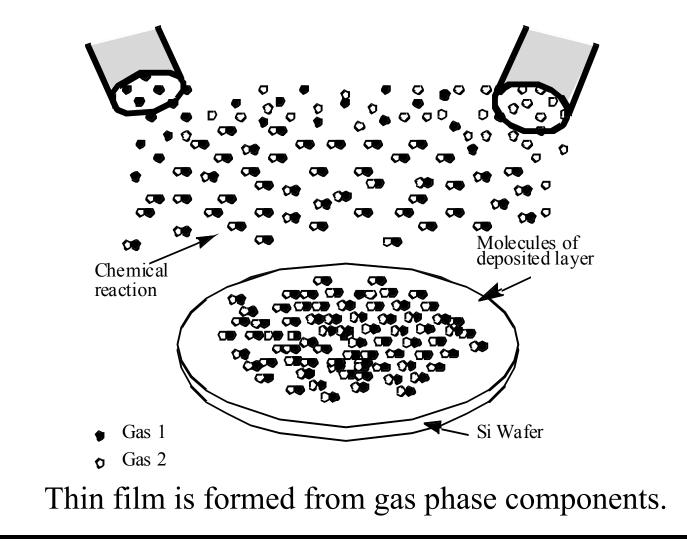

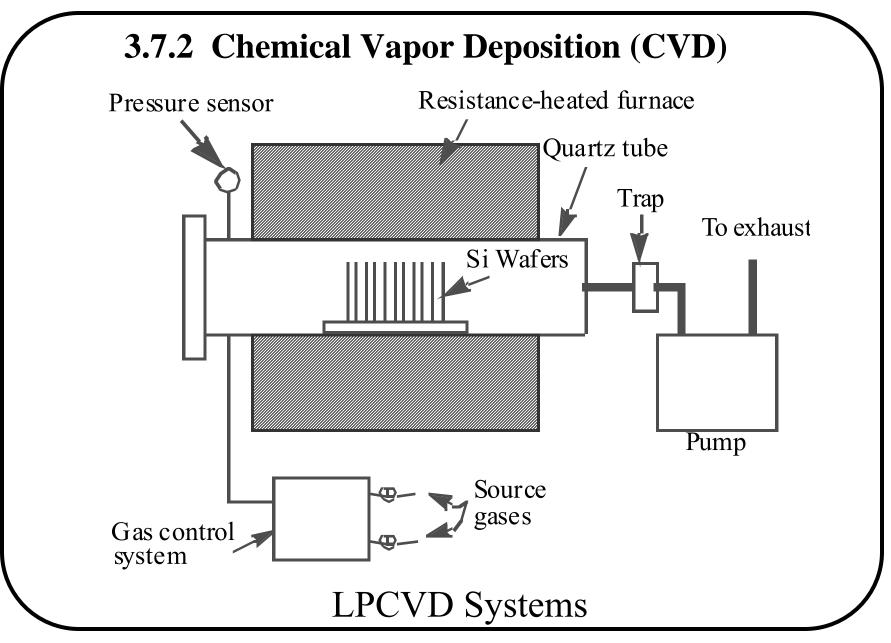

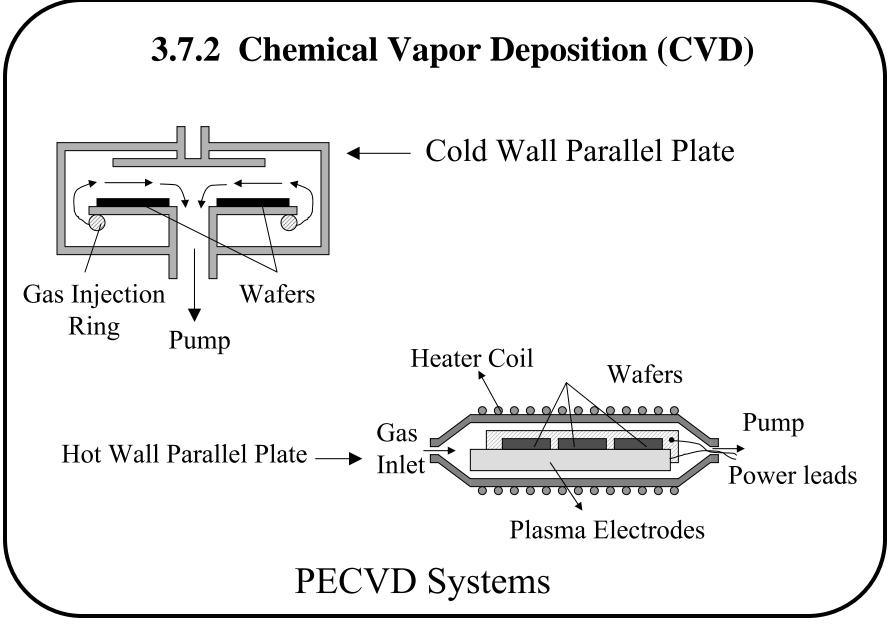

#### **3.7.2** Chemical Vapor Deposition (CVD)

#### **3.7.2** Chemical Vapor Deposition (CVD)

Two types of CVD equipment:

- LPCVD (Low Pressure CVD) : Good uniformity. Used for poly-Si, oxide, nitride.

- **PECVD (Plasma Enhanced CVD)** : Low temperature process and high deposition rate. Used for PE-oxide, PE-nitride, etc.

#### **Chemical Reactions of LPCVD**

- Poly-Si: SiH<sub>4</sub> (g)  $\longrightarrow$  Si (s) + 2H<sub>2</sub> (g)

- Nitride :  $3SiH_2Cl_2(g)+4NH_3(g) \rightarrow Si_3N_4(s)+6HCl(g)+6H_2(g)$

Oxide :

(1) LTO (Low Temperature Oxide) SiH<sub>4</sub> (g) + O<sub>2</sub> (g)  $\longrightarrow$  SiO<sub>2</sub> (s) + 2H<sub>2</sub> (g)

(2) HTO (High Temperature Oxide) SiH<sub>2</sub>Cl<sub>2</sub> (g)+2N<sub>2</sub>O (g)  $\longrightarrow$  SiO<sub>2</sub> (s)+2HCl (g)+2N<sub>2</sub> (g)

Slide 3-31

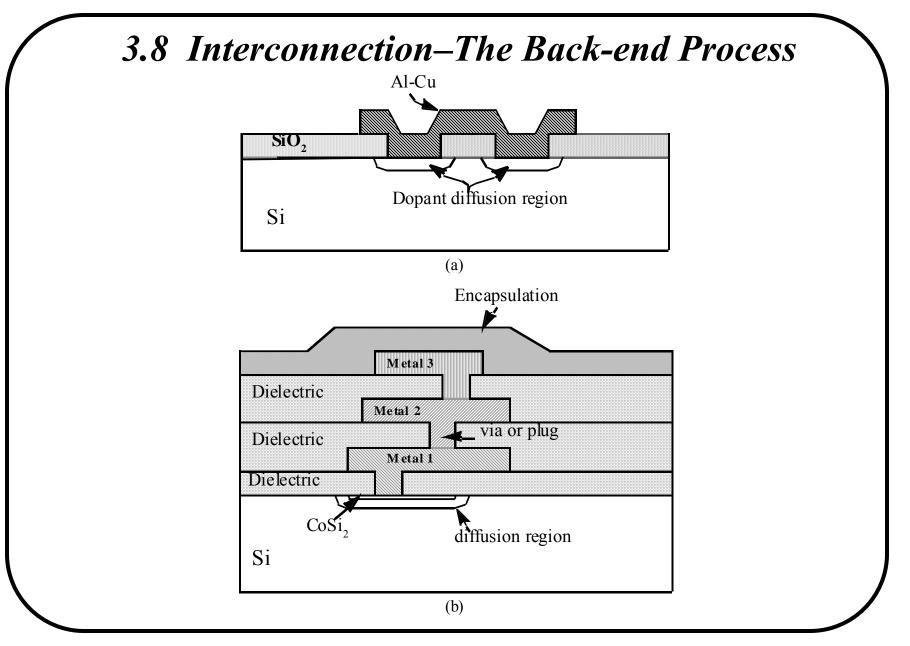

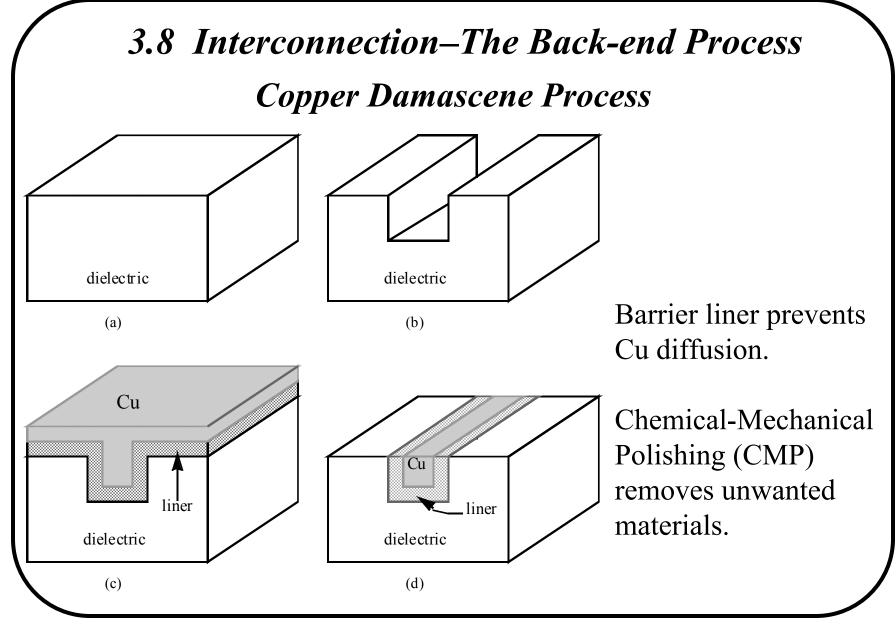

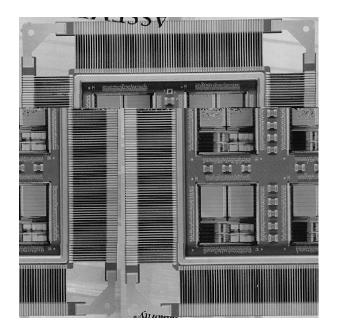

# **3.8 Interconnection–The Back-end Process** *Multi-Level Metallization*

### 3.8 Interconnection–The Back-end Process

# **Copper Interconnect**

- Al interconnect develops voids from electromigration.

- Cu has excellent electromigration reliability and 40% lower resistance than Al.

- Because dry etching of copper is difficult (copper compounds tend to be non-volatile), copper patterns may be defined by a *damascene* process.

Slide 3-35

#### 3.8 Interconnection–The Back-end Process

## Planarization

- A flat surface is highly desirable for subsequent lithography and etching.

- CMP (Chemical-Mechanical Polishing) is used to planarize each layer of dielectric in the interconnect system.

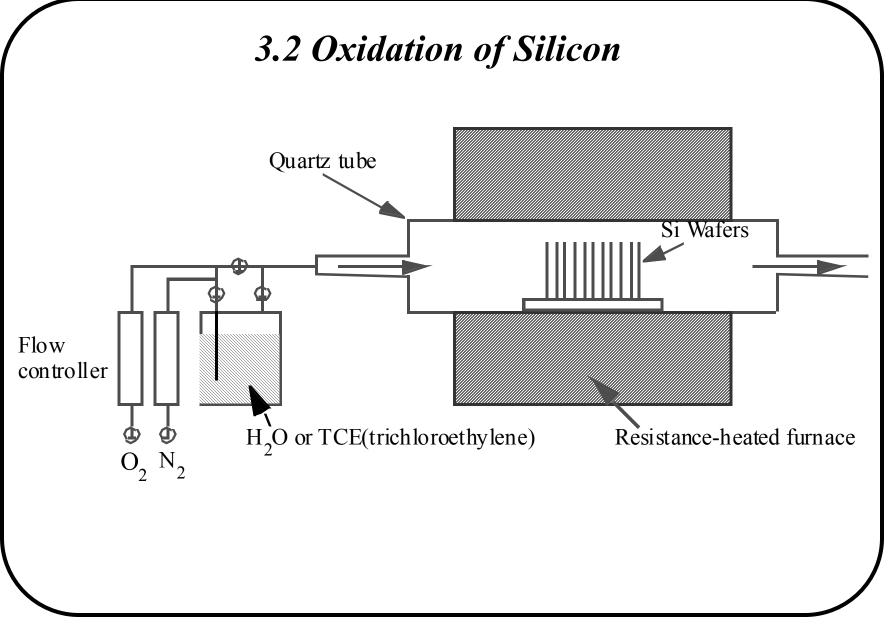

# 3.9 Testing, Assembly, and Qualification

- Wafer acceptance test

- Die sorting

- Wafer sawing or cutting

- Packaging

- Flip-chip solder bump technology

- Multi-chip modules

- Burn-in

- Final test

- Qualification

Slide 3-38