Copyright © 2015 Regents of the University of California

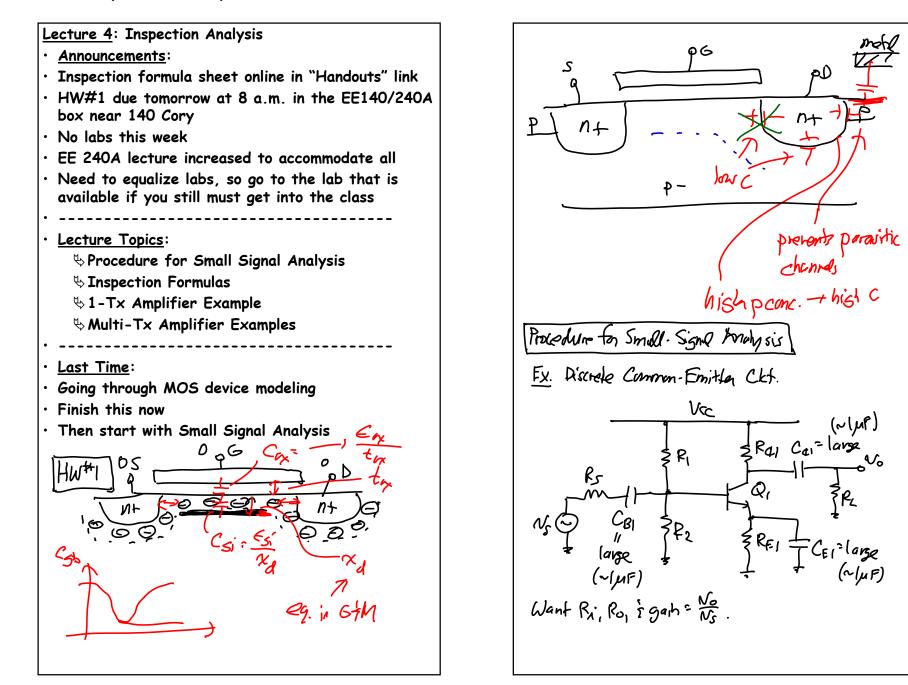

## <u>EE 140/240A</u>: Analog Integrated Circuits <u>Lecture 4w</u>: Inspection Analysis

## Procedure:

- 1. Find the DC operating point

- Get all the voltages & currents at all nodes & branches, respectively

- 2. Determine S.S. parameters for devices in the signal path (e.g.,  $g_m$ ,  $r_\pi$ ,  $r_o$ , ...)

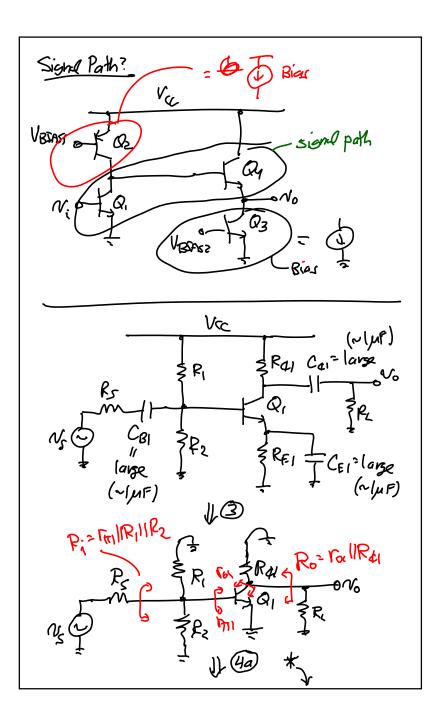

- 3. Convert the full circuit to the S.S. circuit

- Zero out DC sources

- Short out large capacitors (e.g., with values greater than nF's)

- 4. (a) If needed, replace transistor with its S.S.

model (e.g., hybrid-π, T-model, ...)

- This should NOT be needed often!

- When is it needed? → generally in cases where there is feedback

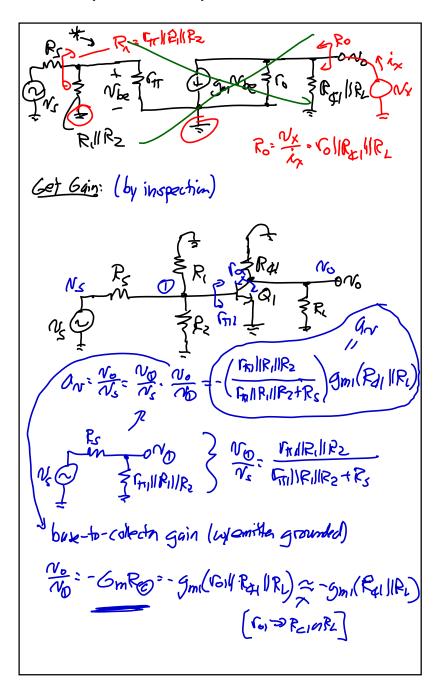

4. (b) Analyze by inspection based on prior S.S. analysis experience! (This should be 99% of the time.)

## <u>EE 140/240A</u>: Analog Integrated Circuits <u>Lecture 4w</u>: Inspection Analysis

CTN 9/8/15

Ex. Common-Collector B= Jnl(GIIPE) ~ Jn)PE N' O  $R_{E} = \frac{V_{0}}{V_{1}} \frac{R_{E}}{CetR_{E}} \frac{(Bt)!}{\Gamma rt}$   $R_{e}^{-1} \Gamma rt (Bt)!R_{E} = \frac{1}{T} \Gamma rt$