## <u>EE 140</u>: Analog Integrated Circuits Lecture 25w: Feedback Configurations

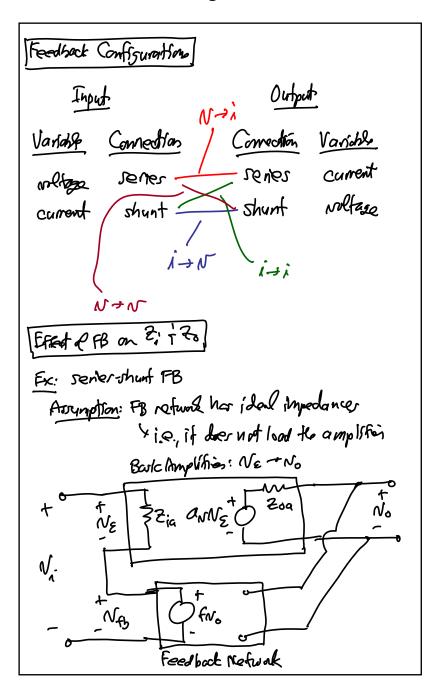

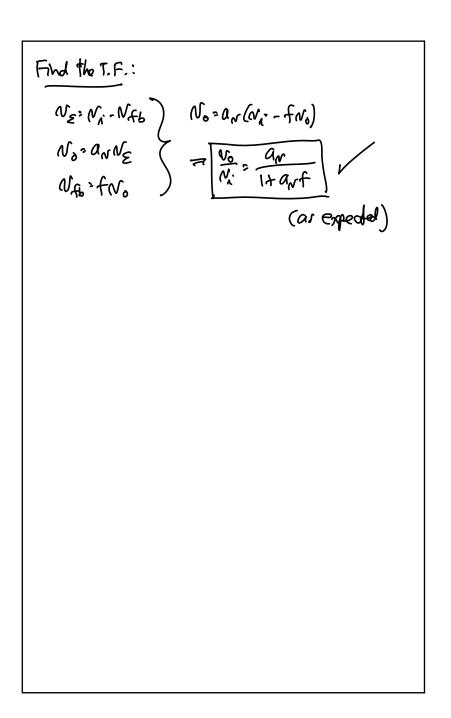

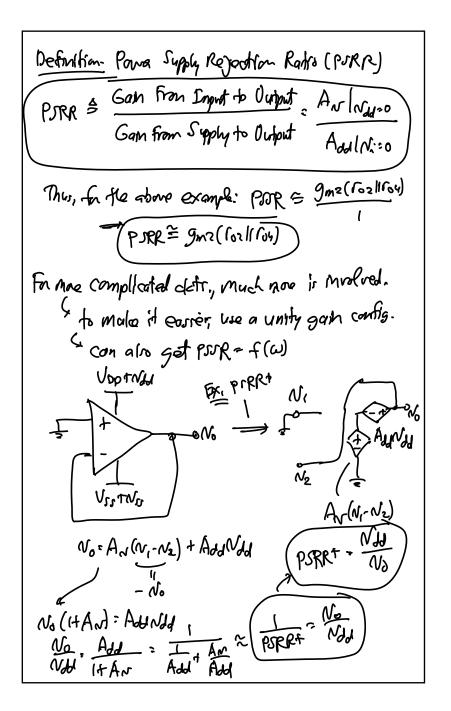

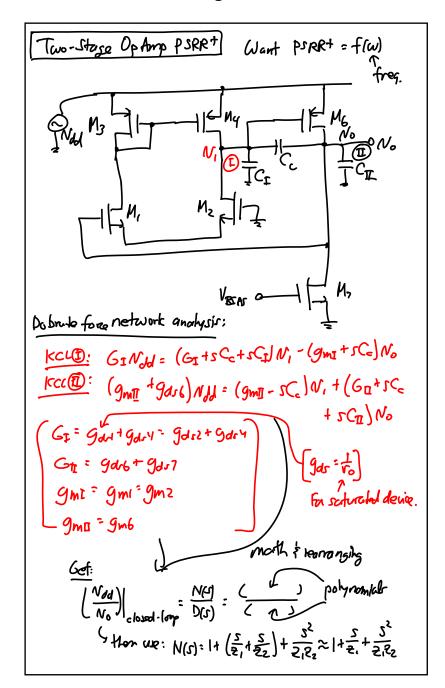

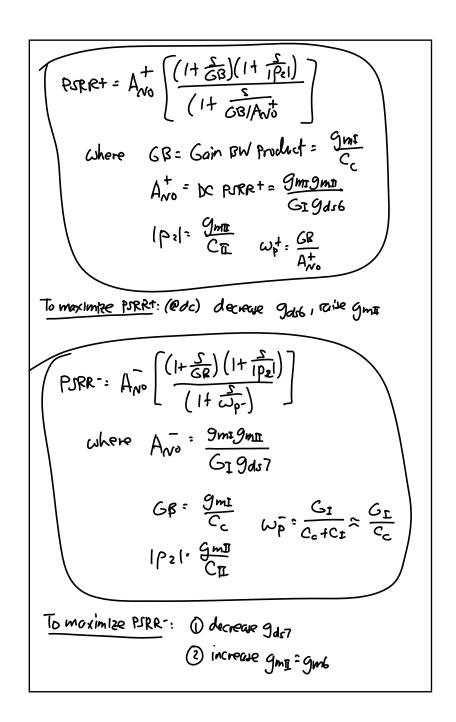

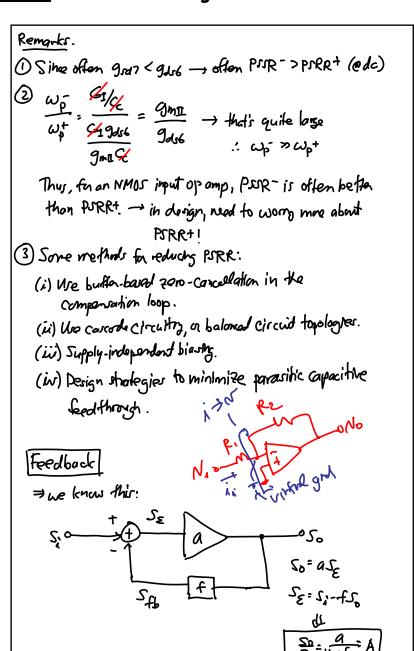

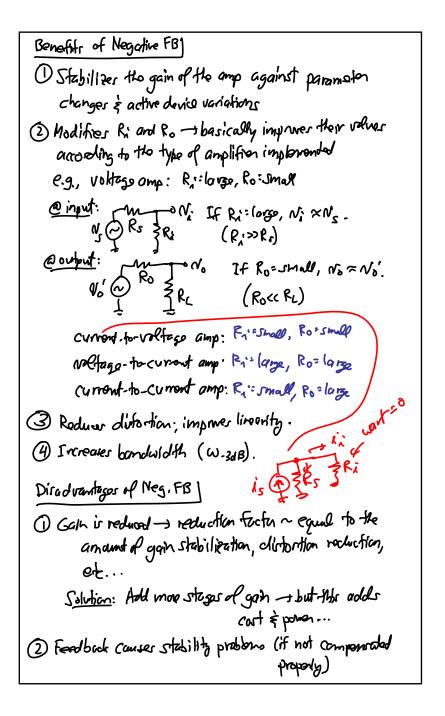

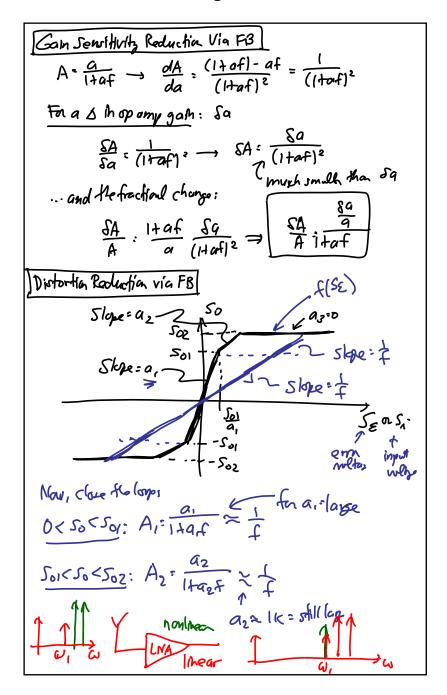

## Lecture 25: Feedback Configurations Announcements: Design Project Checkpoint: ♦ Due Monday, April 25, 11:59 p.m. Send to your TA a spice file for your op amp design that simulates correctly, i.e., that reaches a stable bias point where all transistors are saturated (or linear if an MOS resistor) \$It doesn't need to meet the project specs, but it should simulate correctly Lecture Topics: ♦ Power Supply Rejection Ratio (PSRR) - finish w/ an example ♦ Advantages of Feedback (revisited) $\diamondsuit$ Effect of FB on $Z_i$ and $Z_o$ Last Time: PSRR Ex. CMOS Diff. Input stage of Current Source Local NOD + NOW M3 @ rufnut!

<u>EE 140</u>: Analog Integrated Circuits <u>Lecture 25w</u>: Feedback Configurations

## <u>EE 140</u>: Analog Integrated Circuits Lecture 25w: Feedback Configurations

<u>EE 140</u>: Analog Integrated Circuits <u>Lecture 25w</u>: Feedback Configurations

EE 140: Analog Integrated Circuits

Lecture 25w: Feedback Configurations

EE 140: Analog Integrated Circuits Lecture 25w: Feedback Configurations