#### Assigned Reading

- R.H. Dennard et al, "Design of ion-implanted MOSFET's with very small physical dimensions" IEEE Journal of Solid-State Circuits, April 1974.

Just the scaling principles

- C.G. Sodini, P.-K. Ko, J.L. Moll, "The effect of high fields on MOS device and circuit performance," IEEE Trans. on Electron Devices, vol. 31, no. 10, pp. 1386 - 1393, Oct. 1984.

- K.-Y. Toh, P.-K. Ko, R.G. Meyer, "An engineering model for short-channel MOS devices" IEEE Journal of Solid-State Circuits, vol. 23, no. 4, pp. 950-958, Aug. 1988.

- T. Sakurai, A.R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," IEEE Journal of Solid-State Circuits, vol. 25, no. 2, pp. 584 - 594, April 1990.

### Outline

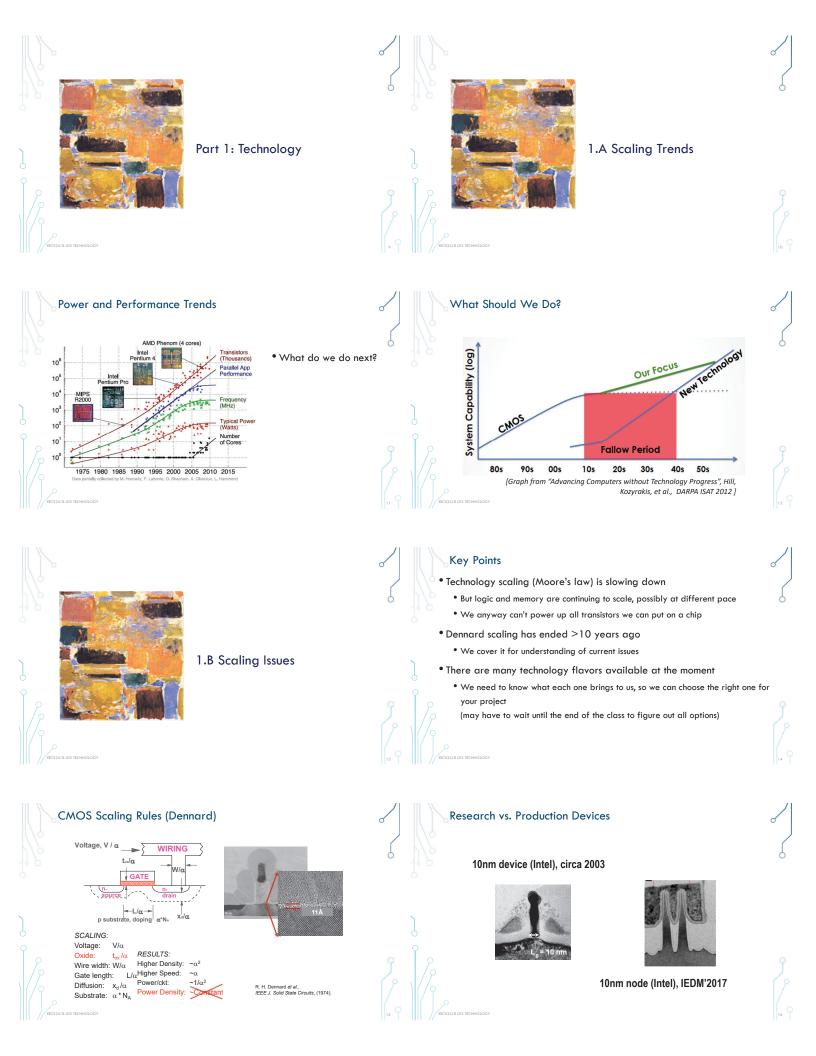

- Scaling issues

- Technology scaling trends

- Features of modern technologies

- Lithography

- Process technologies

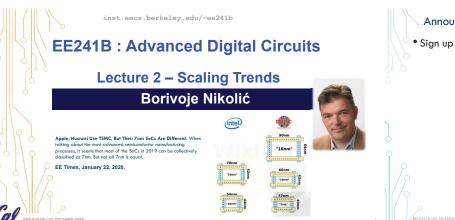

#### Trends and Challenges in Digital Integrated Circuit Design

•We will attempt to dismantle this...

#### Major Roadblocks

- Managing complexity

How to design a 10 billion (100 billion) transistor chip?

And what to use all these transistors for?

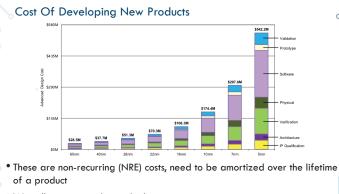

- Cost of integrated circuits is increasing It takes >>\$10M to design a chip Mask costs are many \$M in 16nm technology

- Power as a limiting factor End of frequency scaling Dealing with power, leakages

- 4. Robustness issues

- Variations, SRAM, memory, soft errors, signal integrity

- 5. The interconnect problem

#### Announcements

• Sign up for Piazza if you haven't already

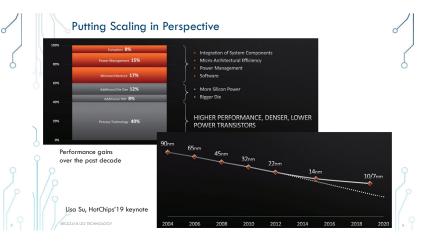

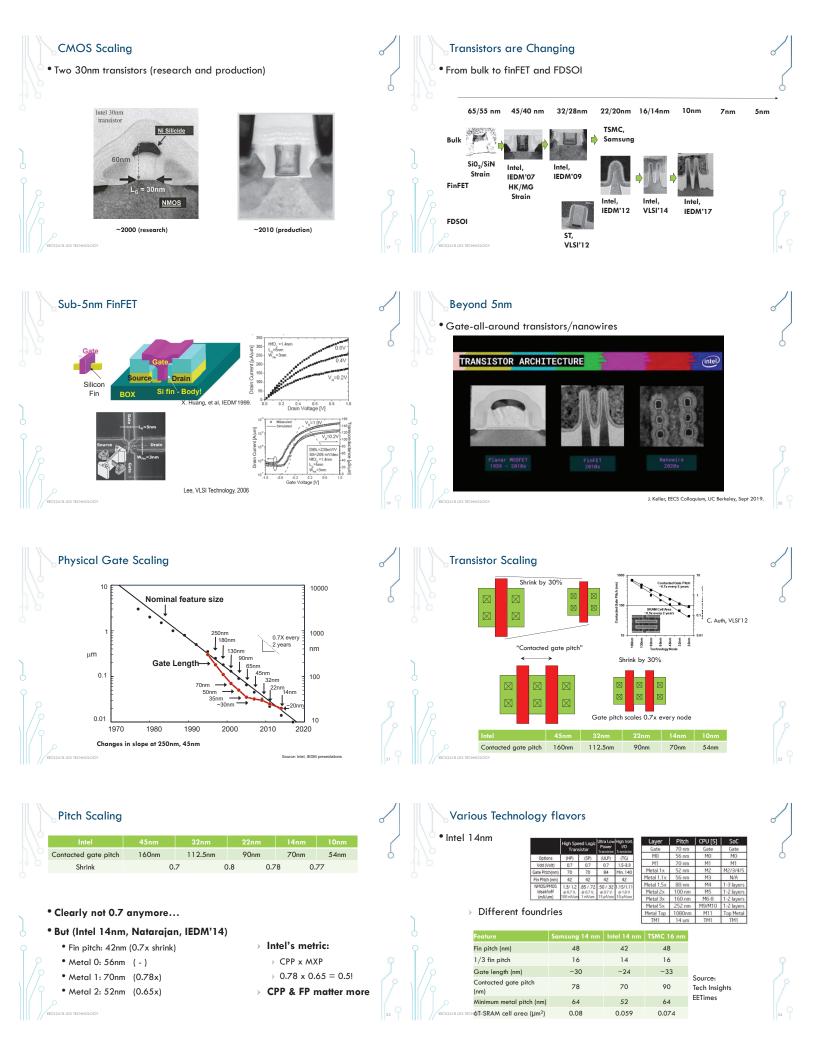

## Not All Technologies are Equal

|      |       | Inte                   | el                | 1        | Sams | ung |    | TS                                                           | MC  |     |    |

|------|-------|------------------------|-------------------|----------|------|-----|----|--------------------------------------------------------------|-----|-----|----|

| Node | СРР   | M×P                    | FP                |          |      |     |    |                                                              |     |     |    |

| 65nm | 230   | 230                    |                   | Node     | СРР  | MxP | FP | Node                                                         | CPP | MxP | FP |

| 45nm | 160   | 160                    |                   | 45nm     | 180  | 140 |    | 45nm                                                         | 190 | 140 |    |

| 32nm | 112.5 | 112.5                  |                   | 32nm     | 130  | 100 |    | 40nm                                                         | 170 | 130 |    |

| 22nm | 90    | 80                     | 60                | 28nm     | 115  | 90  |    | 28nm                                                         | 120 | 90  |    |

| 14nm | 70    | 52                     | 42                | 20LPE    | 90   | 80  | 60 | 20SoC                                                        | 90  | 64  |    |

| 10nm | 54    | 36                     | 34                | 14LPE    | 78   | 64  | 48 | 16FF                                                         | 90  | 64  | 48 |

| 7nm  | 37    | 32                     |                   | 1 OLPE   | 68   | 48  | 42 | 16FFC                                                        | 96  | 64  | 48 |

|      |       |                        |                   | 7LPP     | 54   | 36  | 27 | 10FF                                                         | 66  | 44  | 36 |

|      |       |                        |                   |          |      |     |    | 7FF                                                          | 57  | 40  | 30 |

|      | > C   | PP = Con               | tacted poly       | / pitch  |      |     |    | 5FF                                                          | 50  | 28  |    |

|      |       | xP = Mir<br>P = Fin pi | nimum met<br>itch | al pitch |      |     |    | urce:<br>Wei, Techlnsights<br>M'17, IEDM'19, WikiChip, SemiV |     |     |    |

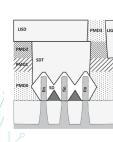

# ASAP7

• Predictive technology kit used in this class

• None of the above processes, but close

| Layer               | Lithography | Width/drawn (nm) | Pitch (nm       |  |  |

|---------------------|-------------|------------------|-----------------|--|--|

| Fin                 | SAQP        | 6.5/7            | 27              |  |  |

| Active (horizontal) | EUV         | 54/16            | 108             |  |  |

| Gate                | SADP        | 21/20            | 54              |  |  |

| SDT/LISD            | EUV         | 25/24            | 54 <sup>b</sup> |  |  |

| LIG                 | EUV         | 16/16            | 54              |  |  |

| VIA0-VIA3           | EUV         | 18/18            | 25*             |  |  |

| M1-M3               | EUV         | 18/18            | 36              |  |  |

| M4 and M5           | SADP        | 24/24            | 48              |  |  |

| VIA4 and VIA5       | LELE        | 24/24            | 34*             |  |  |

| M6 and M7           | SADP        | 32/32            | 64              |  |  |

| VIA6 and VIA7       | LELE        | 32/32            | 45*             |  |  |

| M8 and M9           | SE          | 40/40            | 80              |  |  |

| VIA8                | SE          | 40/40            | 57ª             |  |  |

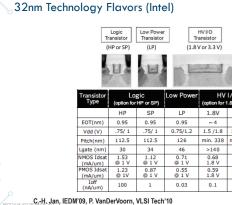

Ideal vs. Real Scaling

$\bullet$  Leakage slows down V\_{Th\prime} V\_DD scaling

With scaling L, need to scale up doping - scale junction depth (control leakage) – S/D resistance goes up

• External resistance limits current  $I_{D} \approx V_{\rm DS} \ / \left( R_{\rm channel} + R_{\rm ext} \right)$

Lg, R, C scaling

• LP keeps drain leakage constant

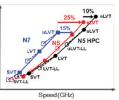

Fig.3 The 5nm also offers a set of critical HPC features. Extremely LVT (eLVT) for 25% faster peak speed over 7nm, and HPC 3-fin standard cell for additional 10% performance.

TSMC, IEDM'19

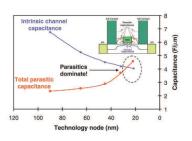

Parasitic Capacitance Scaling