# **EE241B: Advanced Digital Circuits**

# Lecture 22 - Reducing Leakage

# **Borivoje Nikolić**

Sweetfarm.org/goat-2-meeting: Invite a goat or a llama to a zoom meeting

https://www.sweetfarm.org/goat-2-meetin

#### Announcements

- Assignment 4 due next Friday.

- Reading

- Rabaey, LPDE, Chapter 8

#### Outline

- Module 5

- Clock gating

- Leakage reduction during design time and runtime

5.G Reducing Switching Activity Through Logic Design

#### Power / Energy Optimization Space

|         | Constant Throughpu                                                                  | ut/Latency | Variable Th                                | roughput/Latency           |

|---------|-------------------------------------------------------------------------------------|------------|--------------------------------------------|----------------------------|

| Energy  | Design Time                                                                         | Slee       | o Mode                                     | Run Time                   |

| Active  | Logic design<br>Scaled V <sub>DD</sub><br>Trans. sizing<br>Multi-V <sub>DD</sub>    | Clock      | c gating                                   | DFS, DVS                   |

| Leakage | Stack effects<br>Trans sizing<br>Scaling V <sub>DD</sub><br>+ Multi-V <sub>Th</sub> |            | ep T's<br>Variable V <sub>Th</sub><br>trol | + Variable V <sub>Th</sub> |

#### Basic Idea

- E ~ αCV

- ullet Reduce switching activity,  $\alpha$ , through logic and architectural transformations

- Many options

- Switching activity lower with deeper logic

- Pipelining has significant effect

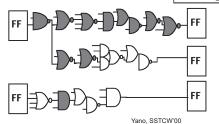

- ${}^{\bullet}$  Reduce the number of clocked devices in a flip-flop

- e.g. group generation of clk\_b

- A few logic ideas follow

EECS241B L22 LEAKAGE

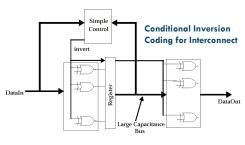

## Circuit-Level Activity Encoding

from [Stan94] (1994 International Workshop on Low-power Design)

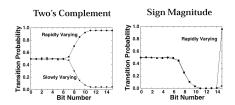

# Number Representation

• Input signals are noise most of the time

• Sign-extension activity significantly reduced using sign-magnitude representation

5.H Clock Gating

#### Power / Energy Optimization Space Constant Throughput/Latency Variable Throughput/Latency Energy Design Time Sleep Mode Run Time Logic design Scaled V<sub>DD</sub> DFS, DVS Active Clock gating Trans. sizing Multi-V<sub>DD</sub> Stack effects Trans sizing Sleep T's DVS, Leakage Scaling V<sub>DD</sub> $\mathbf{Multi\text{-}V_{DD}} \ \mathbf{Variable} \ \mathbf{V_{Th}}$ Variable V<sub>Th</sub> + Multi-V<sub>Th</sub> + Input control

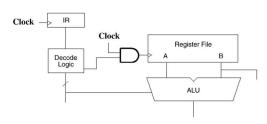

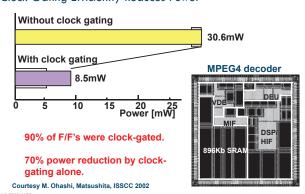

# Clock Gating

Requires a bit more complex gate ... Well handled in today's EDA tools

# Clock Gating

Enabling clock needs to be synchronized

#### Clock Gating

ARM Cortex-A9 Technical Reference Manual:

#### Dynamic high level clock gating activity

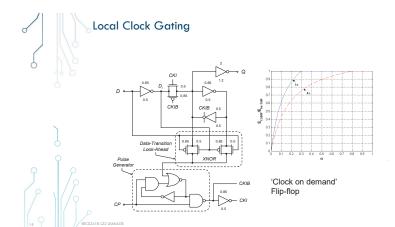

# Local Clock Gating

# Complex Designs Clock System . Variable Architecture Supply Fixed Supply CVD Gater 1/1 CVD Gater 1/N SLCB

Phase Aligner

Fischer, ISSCC'05

# Power / Energy Optimization Space

|         | Constant Throughpu                                                               | ut/Latency | Variable Th                                | roughput/Latency                 |

|---------|----------------------------------------------------------------------------------|------------|--------------------------------------------|----------------------------------|

| Energy  | Design Time                                                                      | Slee       | p Mode                                     | Run Time                         |

| Active  | Logic design<br>Scaled V <sub>DD</sub><br>Trans. sizing<br>Multi-V <sub>DD</sub> | Clock      | c gating                                   | DFS, DVS                         |

| Leakage | Stack effects Trans sizing Scaling V <sub>DD</sub> + Multi-V <sub>Th</sub>       |            | ep T's<br>Variable V <sub>Th</sub><br>trol | DVS,<br>Variable V <sub>Th</sub> |

#### Plan For the Rest of the Semester

- 4 more lectures:

- Finish low power (2 lectures)

- Supplies, clocks and their interaction

- Homework 4 due on April 24th

- Quiz 4 on April 28th

- Final on April 30<sup>th</sup>

- 80 minutes, open everything

- Final presentations, May 4

- Final reports due on May 4

5.I Lowering Leakage During Design: Multiple Thresholds

### Power / Energy Optimization Space

|         | Constant Throughpu                                                               | ıt/Latency   | Variable Th                                                      | roughput/Latency                 |

|---------|----------------------------------------------------------------------------------|--------------|------------------------------------------------------------------|----------------------------------|

| Energy  | Design Time                                                                      | Sleep        | o Mode                                                           | Run Time                         |

| Active  | Logic design<br>Scaled V <sub>DD</sub><br>Trans. sizing<br>Multi-V <sub>DD</sub> | Clock        | c gating                                                         | DFS, DVS                         |

| Leakage | Stack effects Trans sizing Scaling V <sub>DD</sub> + Multi-V <sub>Th</sub>       | Mul<br>Varia | ep T's<br>ti-V <sub>DD</sub><br>ble V <sub>Th</sub><br>t control | DVS,<br>Variable V <sub>Th</sub> |

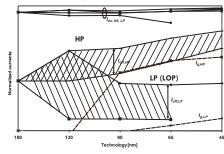

## Technology Options

• Multiple thresholds, each spaced 50-100mV apart (5-10x less leakage)

# Using Multiple Thresholds

- Cell-by-cell  $\mathbf{V}_{\mathsf{T}}$  assignment (not block level) Allows us to minimize leakage

- Achieves all-low-V performance

# Typical Technologies

- 2-3 Thresholds

- To choose from 4-6 in a node

- In bulk and finfet, but not in FDSOI (unless doped)

- Threshold voltage diff ~5-10x in leakage

5.I Lowering Leakage During Design: Longer Channels

# Power /Energy Optimization Space

|         | Constant Throughpu                                                               | ıt/Latency  | Variable Th                                                        | roughput/Latency                 |

|---------|----------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------|----------------------------------|

| Energy  | Design Time                                                                      | Slee        | p Mode                                                             | Run Time                         |

| Active  | Logic design<br>Scaled V <sub>DD</sub><br>Trans. sizing<br>Multi-V <sub>DD</sub> | Clock       | k gating                                                           | DFS, DVS                         |

| Leakage | Stack effects Trans sizing Scaling V <sub>DD</sub> + Multi-V <sub>Th</sub>       | Mu<br>Varia | ep T's<br>lti-V <sub>DD</sub><br>ıble V <sub>Th</sub><br>t control | DVS,<br>Variable V <sub>Th</sub> |

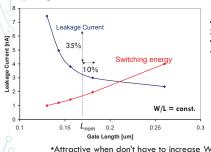

- •10% longer gates reduce leakage by 35% (in 130nm)

- with W/L = const.

- $\bullet$  Increases switching energy by 21%

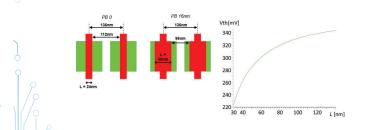

# Poly Bias • 28FDSOI example

- •Attractive when don't have to increase W (memory)

- •Doubling L reduces leakage by 3x (in 0.13um)

- •Much stronger effect in 28nm!

- •Effect improves with shorter channel devices

# Longer Channels

5.J Lowering Leakage During Design: Transistor Stacking

# Power / Energy Optimization Space

|         | Constant Throughpu                                                               | ıt/Latency                                                                        | Variable T | hroughput/Latency          |

|---------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------|----------------------------|

| Energy  | Design Time                                                                      | Slee                                                                              | o Mode     | Run Time                   |

| Active  | Logic design<br>Scaled V <sub>DD</sub><br>Trans. sizing<br>Multi-V <sub>DD</sub> | Clock                                                                             | gating     | DFS, DVS                   |

| Leakage | Stack effects Trans sizing Scaling V <sub>DD</sub> + Multi-V <sub>Th</sub>       | Sleep T's<br>Multi-V <sub>DD</sub><br>Variable V <sub>Th</sub><br>+ Input control |            | + Variable V <sub>Th</sub> |

Narendra, ISLPED'01

| Reduction | (in | 0.13µ): |

|-----------|-----|---------|

|           |     |         |

|        | High $V_t$ | Low V |

|--------|------------|-------|

| 2 NMOS | 10.7X      | 9.96X |

| 3 NMOS | 21.1X      | 18.8X |

| 4 NMOS | 31.5X      | 26.7X |

| 2 PMOS | 8.6X       | 7.9X  |

| 3 PMOS | 16.1X      | 13.7X |

| 4 PMOS | 23.1X      | 18.7X |

- Tradeoffs: W/2 1/3 of drive current, same loading 1.5W 3x loading, same drive current

Narendra, ISLPED'01

# Next Lecture

- Low-power design

- Power gating

- Dynamic thresholds

- Optimal supplies and thresholds