inst.eecs.berkeley.edu/~ee241b

# **EE241B : Advanced Digital Circuits**

# Lecture 25 – Power Supply **Borivoje Nikolić**

### Time for course surveys!

### **Course Evaluations: Best Practices for Faculty**

### Reserve time in-class.

Give students time during class to complete the online course survey. Anecdotally, this is more effective when the time set aside is at the **start** of class.

### Inform students about the purpose of evaluations.

Give students examples of useful feedback you have received in the past and how the course has changed or benefited.

### Offer students incentives (e.g. extra credit).

To encourage broad, representative responses, instructors may choose to offer incentives to complete evaluations. An effective strategy has been to offer all students extra credit if a minimum percentage of students (e.g. 85%) respond.

S241B L25 SUPPLY

### Announcements

• Quiz today!

- Final on Thursday, April 30, 9:30-11am

- Project presentations on Monday, May 4

- Course surveys:

- <u>https://drive.google.com/file/d/1saRVPwUtLIRBApUzZ0Y9XAAG9vAhFkdV/view</u>

## Outline

- Module 6

- Supply distribution

EECS241B L25 SUPPLY

$\cap$

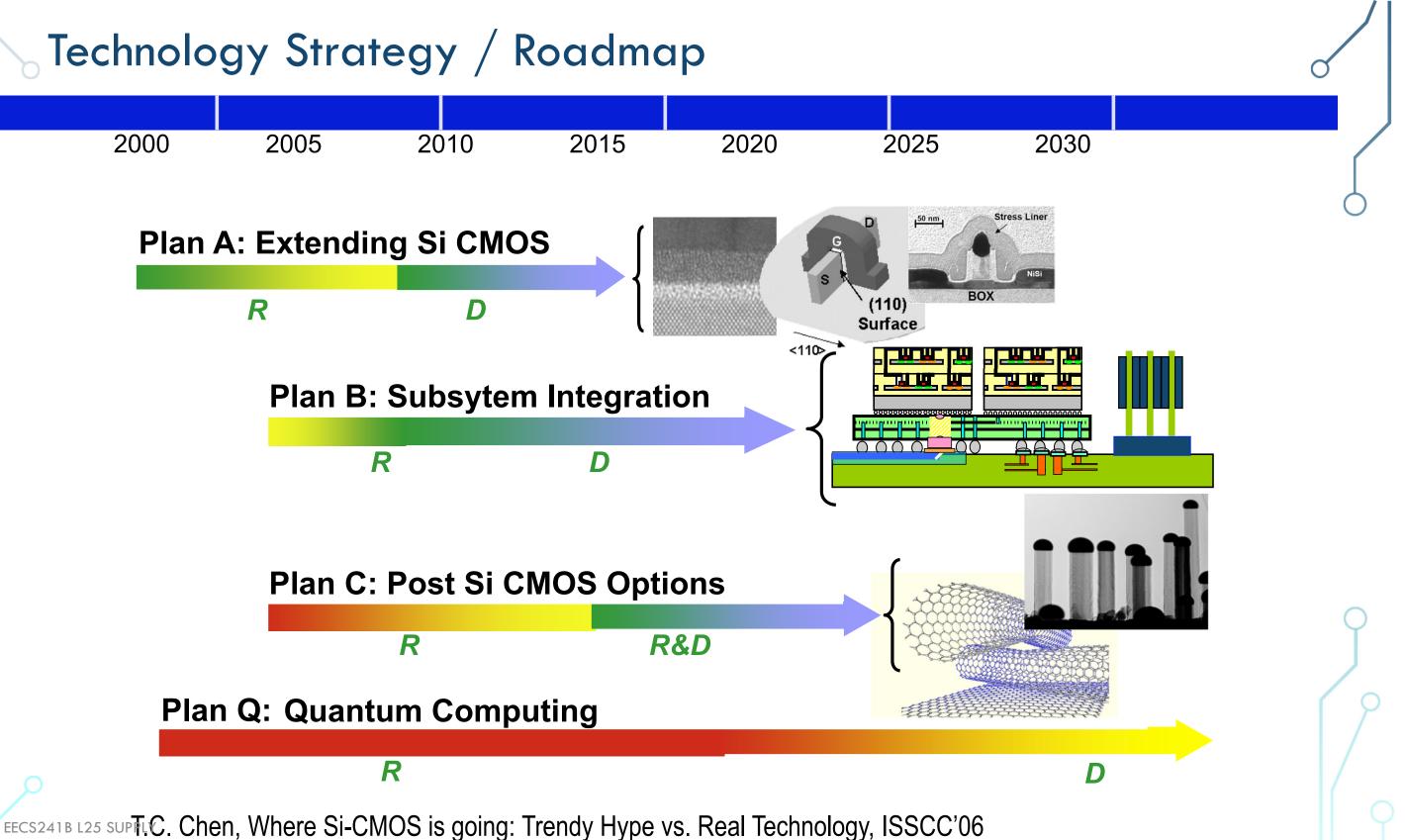

## 6.C Clock Generation: PLLs

EECS241B L25 SUPPLY

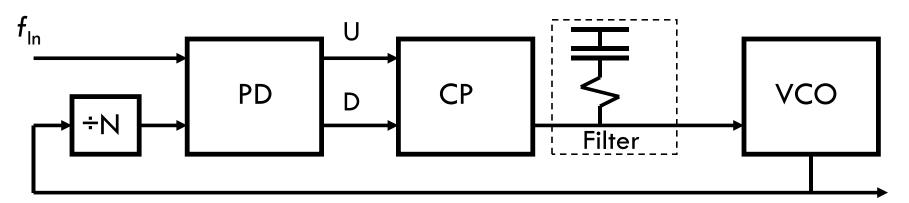

### Phase-Locked Loop

- PLL is locked when the phase difference is zero

- Second/third order loop

- ÷N for frequency synthesis (and x M)

- Filters input jitter

FFCS241B

• Accumulates phase error

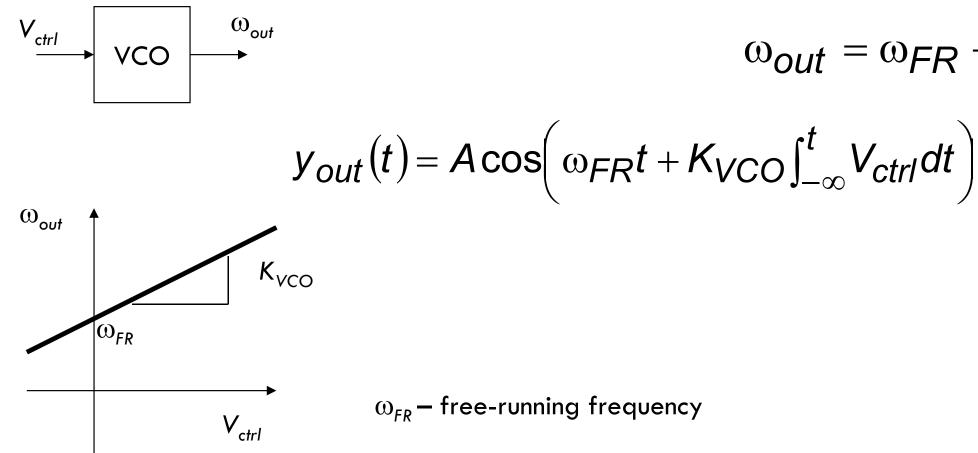

### Voltage-Controlled Oscillator

Oscillation frequency controlled by voltage

### $\omega_{out} = \omega_{FR} + K_{VCO}V_{ctrl}$

### Example VCO

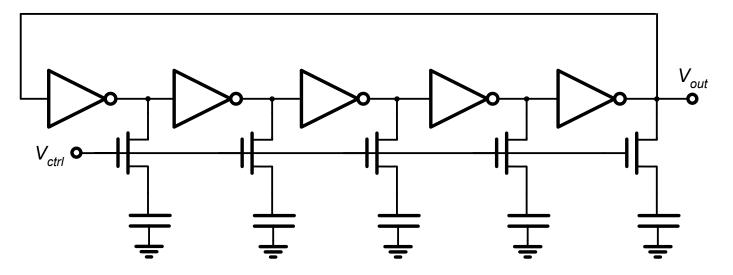

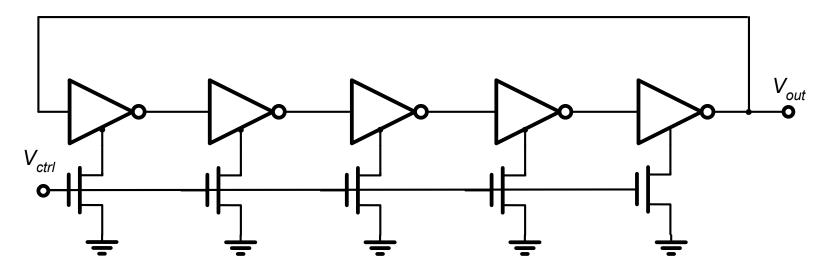

• Ring-oscillator-based VCO: RC loaded

Ring-oscillator-based VCO: Current-starved

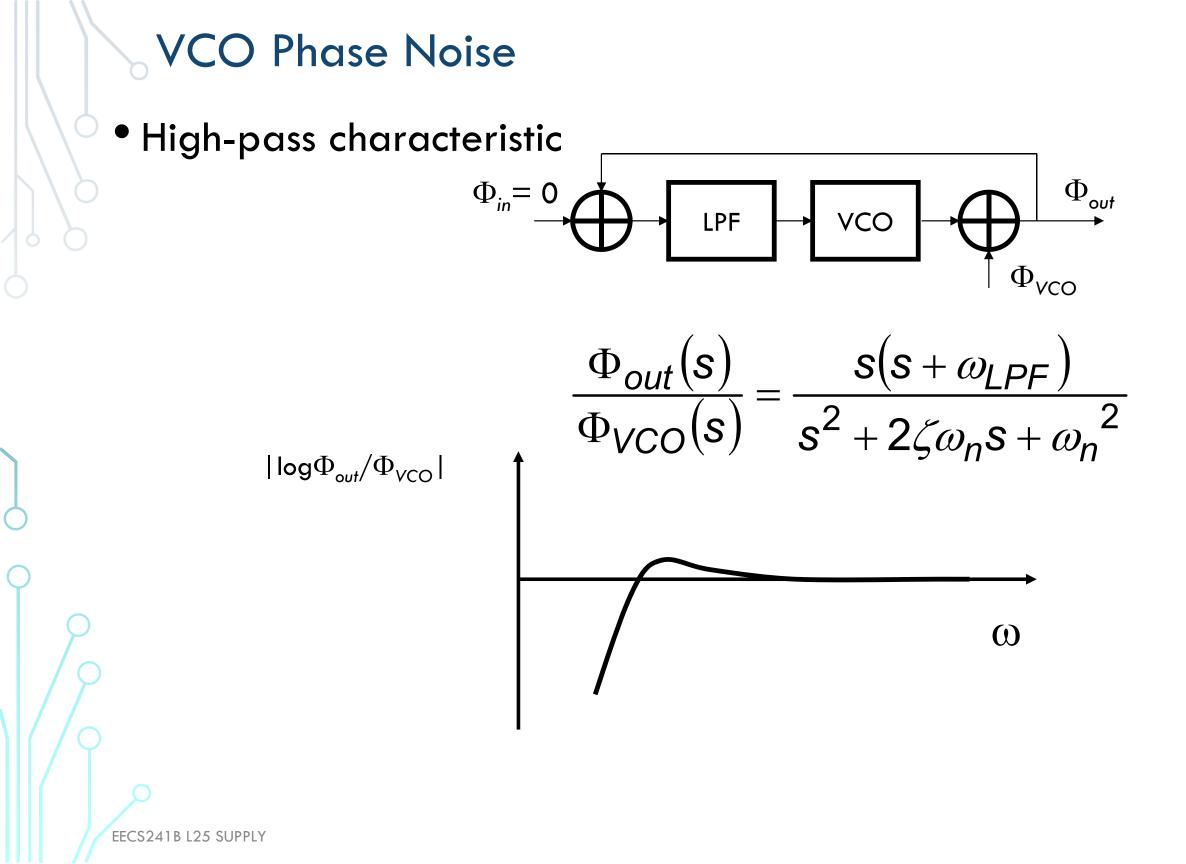

### PLL vs. DLL Dynamics

- The key difference is in the VCDL vs. VCO transfer characteristics

- VCO integrates (accumulates) phase

$H_{\rm VCO}(s) = K_{\rm VCO}/s$

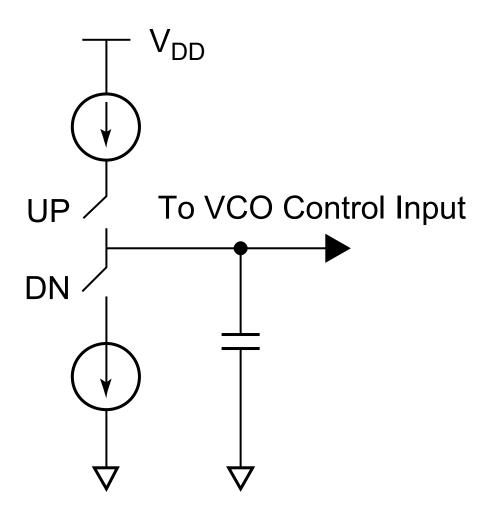

### Charge Pump

• Push/pull current source operation

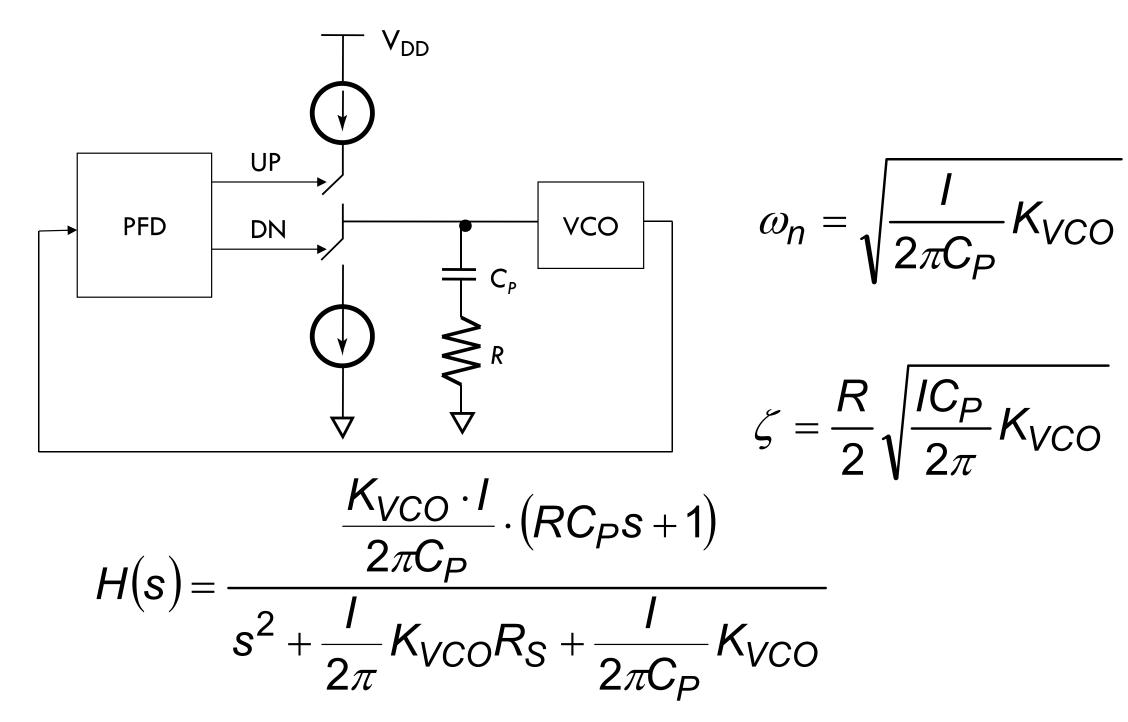

## Charge-Pump PLL $V_{DD}$ UP VCO PFD DN $C_{P}$ $\overline{\mathbf{\nabla}}$ Phase transfer function $H(s) = \frac{\frac{K_{PFD}}{s} \cdot \frac{K_{VCO}}{s}}{1 + \frac{K_{PFD}}{s} \cdot \frac{K_{VCO}}{s}} = \frac{K_{PFD}K_{VCO}}{s^2 + K_{PFD}K_{VCO}}$ S S EECS241B L25 SUPPLY

- Charge pump PLL has a stability problem

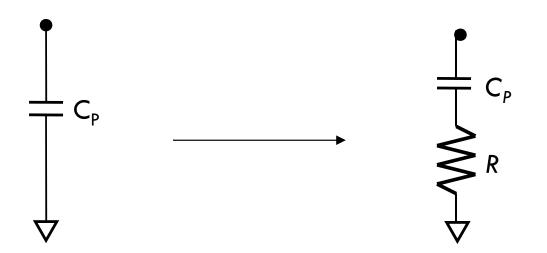

- Compensation by adding a zero

### Charge Pump PLL with a Zero

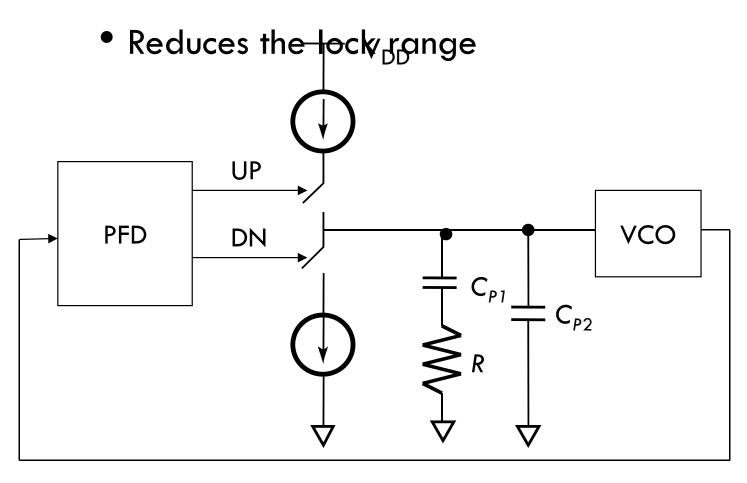

### Higher Order Loops

- Another pole naturally exists

- Filters the control voltage  $V_{CTRL}$

- Lowers phase margin

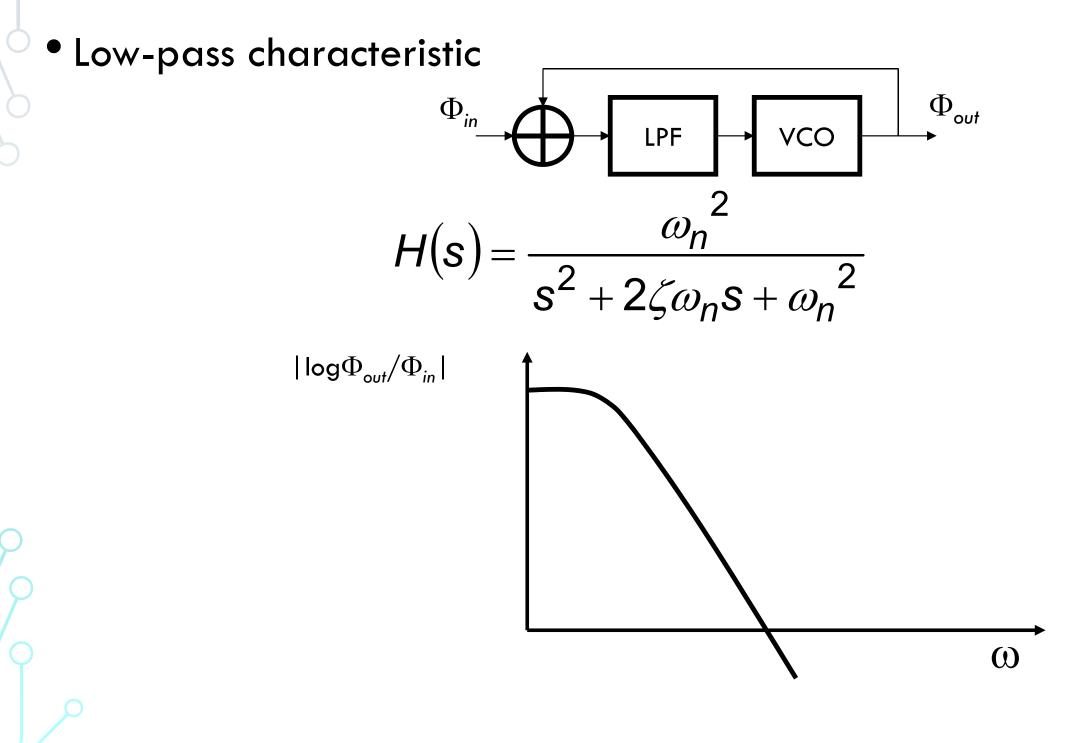

### Phase Noise at the PLL Input

EECS241B L25 SUPPLY

## 6.D Interaction with Supply

EECS241B L25 SUPPLY

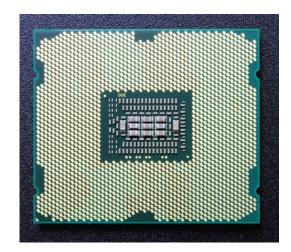

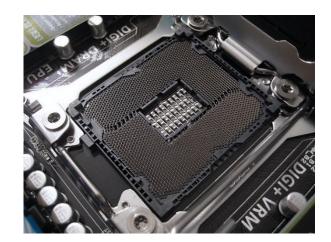

### Power Delivery

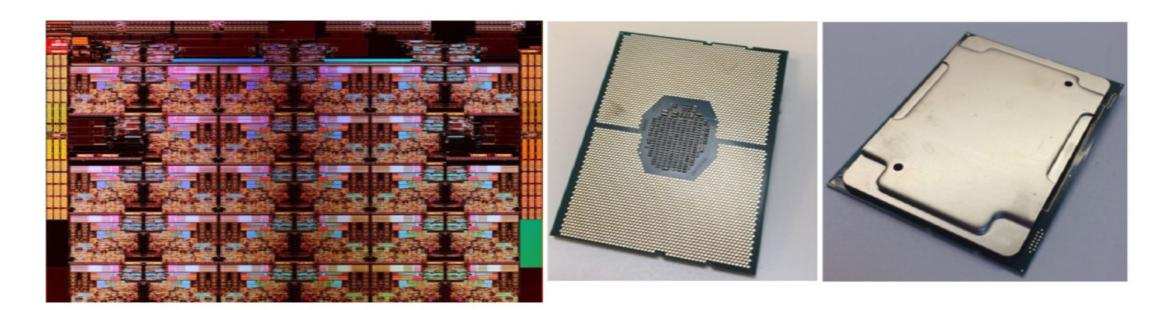

### • Decoupling in Core i7

Andreas Hopf/Flickr

### Skylake-SP, ISSCC'18

Decoupling in Skylake-SP

EECS241B L25 SUPPLY

0

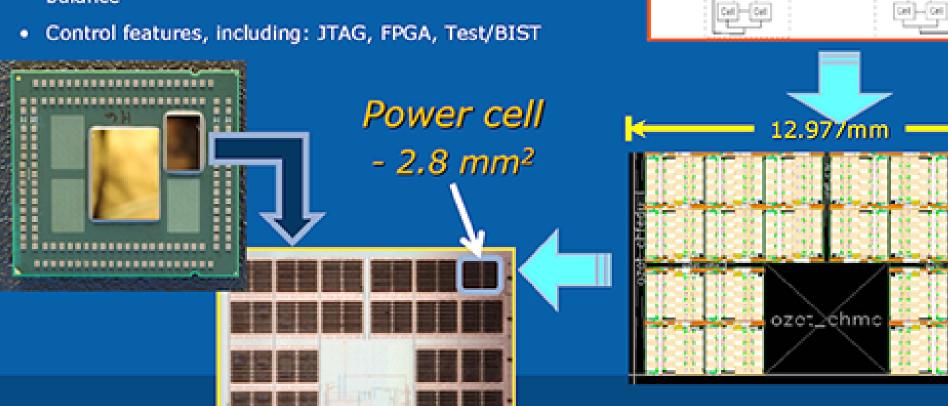

### Inside Haswell

### Integrated VR Technology

- 'Common Cell' Architecture 20 cells

- Architecture supports flat efficiency curve

- Fine grain power management

- · Allows for multiple voltage rails

- Telemetry and Margining features

- Active Voltage Positioning for current sharing and balance

- Control features, including: JTAG, FPGA, Test/BIST

intel

Gell --

Cel --- Cel

Coll\_Col

68 64

K. polyti

Cell-Cell

Waster Corbole

Waterwise)

density in

### Inside Haswell

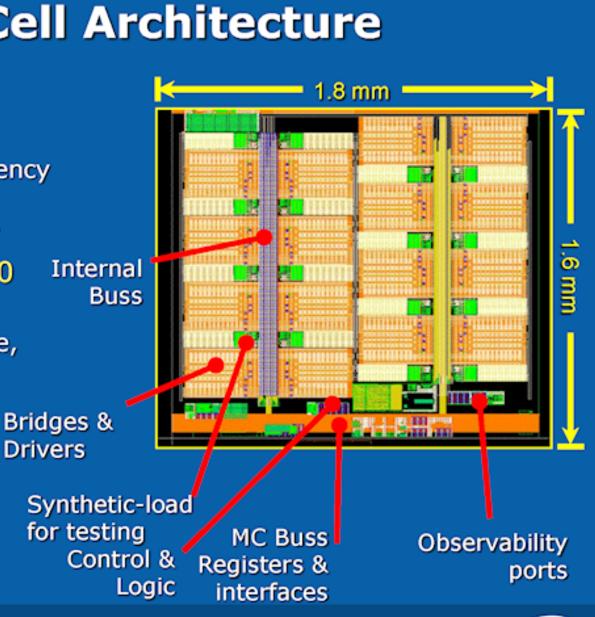

### **Review: Power Cell Architecture**

Each Power cell = Mini VR

- Up to 25A rating\* tested

- Programmable switching frequency 30MHz to 140MHz

- Ring coupled inductor topology

- 16 phases per power cell, 320 phases per chip

- High phase count reduces noise, ripple

- High granularity

- Cell shedding

- Bridge shedding

### BIST

Self-load and characterization system.

\* Thermally constrained

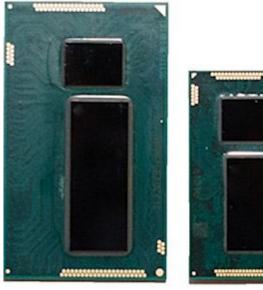

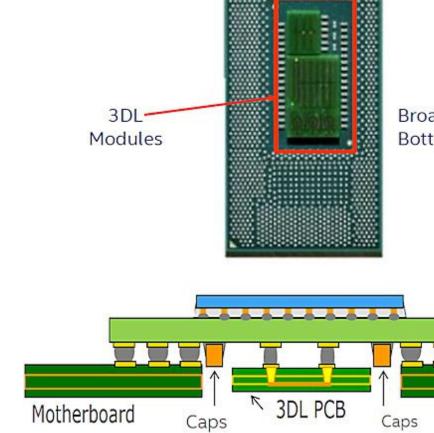

### Intel Broadwell

### • Inductors moved to a small PCB

HSW U/Y 40x24x1.5mm

BDW-Y 30x16.5x1.04mm

EECS241B L25

### Broadwell-Y Bottom Side

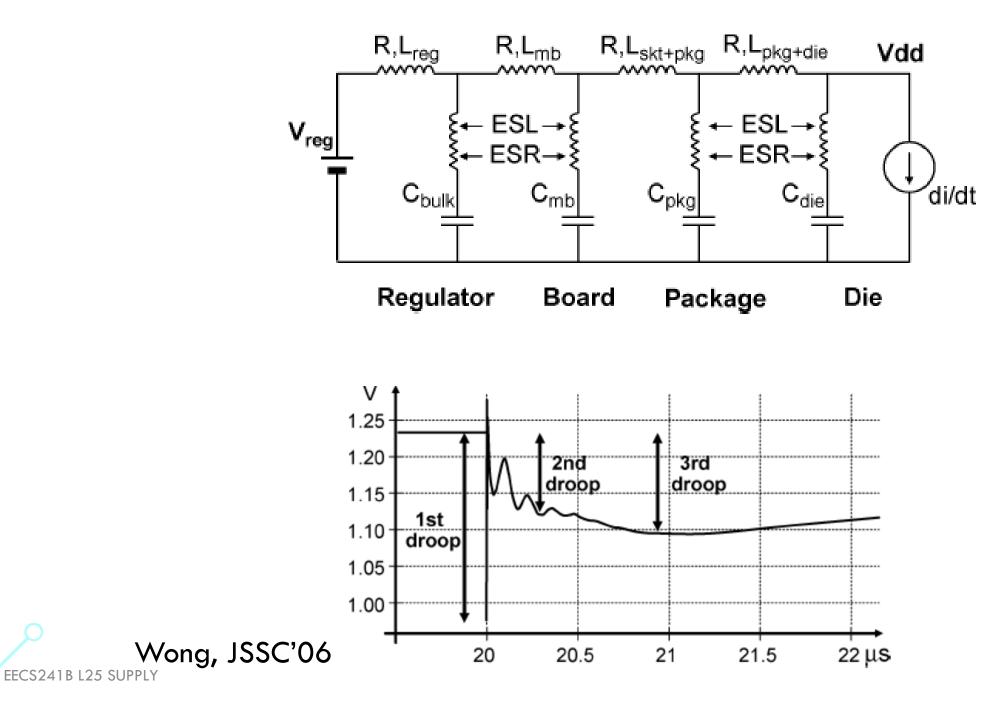

### Power Delivery

• Typical model

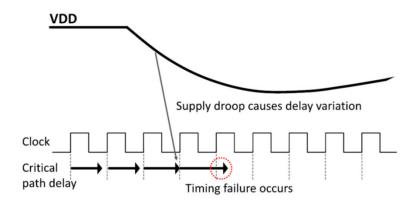

## Supply Resonances

- First droop

- Package L + on-die C

- Second droop

- Motherboard + package decoupling

- Third droop

- Board capacitors

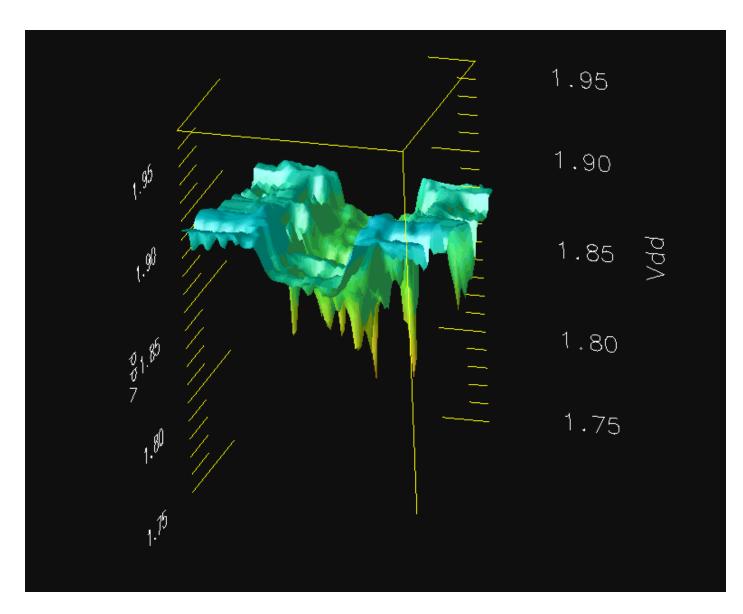

### What happens with supply?

http://www.research.ibm.com/people/r/restle/Animations/DAC01top.html

EECS241B L25 SUPPhillip Restle, IBM

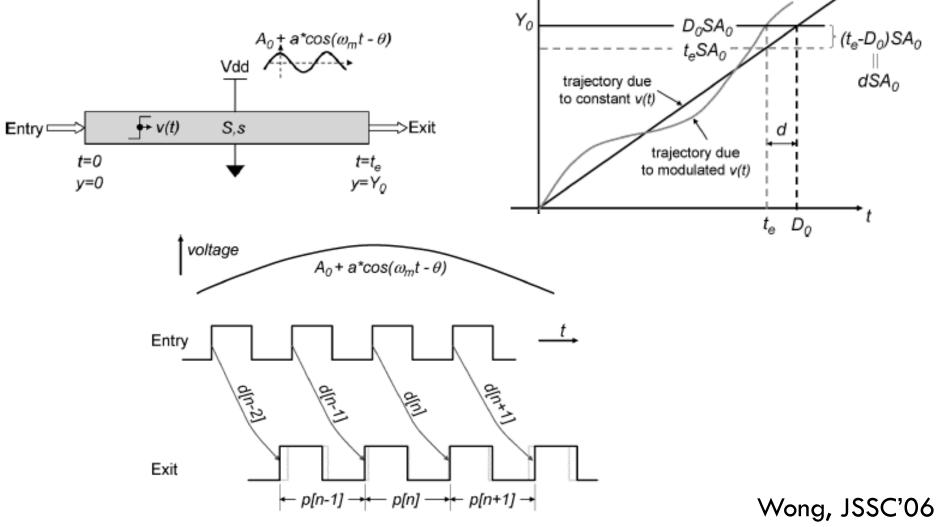

### How to model

Abstracted delay line

У

Period modulation from successive modulated delays

EECS241B L25 SUPPLY

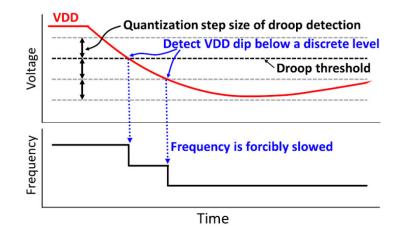

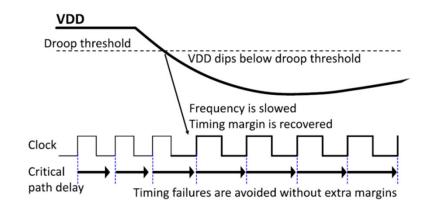

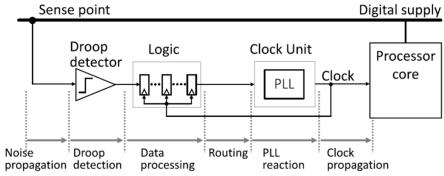

### **Droop Detection**

• Hashimoto, JSSC 4/18

## This Class

- Put design choices in technology perspective

- The design constraints have changed and will be changing

- Cost, energy, (power, leakage, ...), performance

- Focused on variability, power-performance tradeoffs, power management

- Did not cover arithmetic, domino, I/O, supply generation, packaging, ...

### This Field

- Moore's law will end sometime during your (my?) career

- 5nm in 2020 scales to 0.1nm by 2050 with 2-yr cycles (or to 1nm with 4-yr cycles)

- Physics will stop CMOS somewhere  $\sim$  3nm (?)

- Will we see a different CMOS device in the meantime

- Economics will likely stop it somewhere while still in single digits

- And the nodes will be stretched out

- We will see multi-chip/packaging solutions

- Don't worry: Creativity is unlimited!

- What can you build with 10B/100B/1 trillion transistors?

- Even filling 10B-transistor chips with SRAM is not trivial!

### This Field

- Focus on principles

- Watch out for opportunities

- Stay current!