# **EE241B: Advanced Digital Circuits**

# **Lecture 25 – Power Supply**

# **Borivoje Nikolić**

Time for course surveys!

#### Announcements

- Quiz today!

- Final on Thursday, April 30, 9:30-11am

- Project presentations on Monday, May 4

- Course surveys:

- $\bullet \ \, \underline{https://drive.google.com/file/d/1saRVPwUtLIRBApUzZOY9XAAG9vAhFkdV/view}\\$

## Outline

- Module 6

- Supply distribution

6.C Clock Generation: PLLs

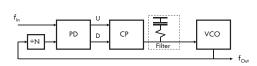

#### Phase-Locked Loop

- PLL is locked when the phase difference is zero

- Second/third order loop

- $\bullet$  ÷N for frequency synthesis (and x M)

- Filters input jitter

- Accumulates phase error

# Voltage-Controlled Oscillator

Oscillation frequency controlled by voltage

$\omega_{out} = \omega_{FR} + K_{VCO}V_{ctrl}$

$$y_{out}(t) = A\cos\left(\omega_{FR}t + K_{VCO}\int_{-\infty}^{t} V_{ctrl}dt\right)$$

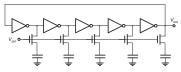

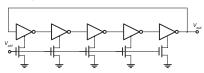

# Example VCO

• Ring-oscillator-based VCO: RC loaded

> Ring-oscillator-based VCO: Current-starved

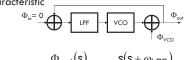

# PLL vs. DLL Dynamics

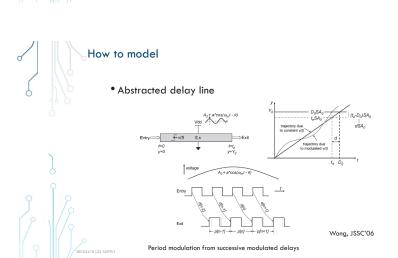

- The key difference is in the VCDL vs. VCO transfer characteristics

- VCO integrates (accumulates) phase

$$H_{VCO}(s) = K_{VCO}/s$$

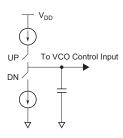

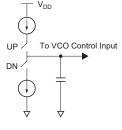

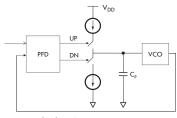

# Charge Pump

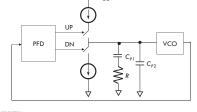

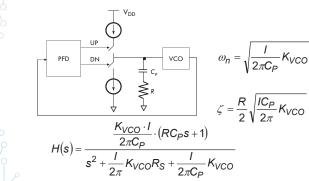

# Charge Pump PLL with a Zero

- Charge pump PLL has a stability problem

- Compensation by adding a zero

# Higher Order Loops

- Another pole naturally exists

- ullet Filters the control voltage  $V_{\it CTRL}$

- Lowers phase margin

- Reduces the lock gange

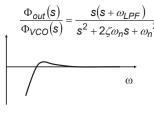

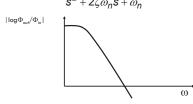

### VCO Phase Noise

• High-pass characteristic

# Charge-Pump PLL

Phase transfer function

$$H(s) = \frac{\frac{K_{PFD}}{s} \cdot \frac{K_{VCO}}{s}}{1 + \frac{K_{PFD}}{s} \cdot \frac{K_{VCO}}{s}} = \frac{K_{PFD}K_{VCO}}{s^2 + K_{PFD}K_{VCO}}$$

# Charge Pump PLL with a Zero

# Phase Noise at the PLL Input

• Low-pass characteristic

# 6.D Interaction with Supply

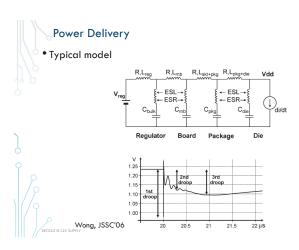

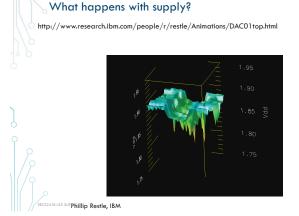

Supply Resonances

• Package L + on-die C

• Board capacitors

• Motherboard + package decoupling

• First droop

Second droop

• Third droop

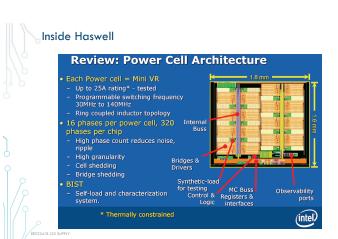

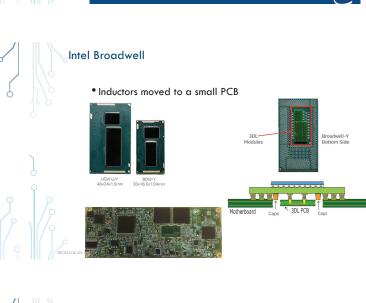

**Integrated VR Technology**

Inside Haswell

## **Droop Detection**

• Hashimoto, JSSC 4/18

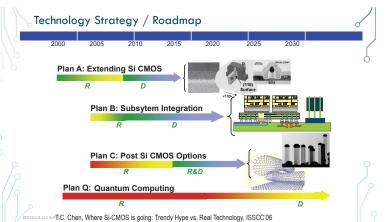

#### This Class

- Put design choices in technology perspective

- The design constraints have changed and will be changing

- Cost, energy, (power, leakage, ...), performance

- Focused on variability, power-performance tradeoffs, power management

- $^{ullet}$  Did not cover arithmetic, domino, I/O, supply generation, packaging,  $\dots$

#### This Field

- Moore's law will end sometime during your (my?) career

- 5nm in 2020 scales to 0.1nm by 2050 with 2-yr cycles (or to 1nm with 4-yr cycles)

- Physics will stop CMOS somewhere ~3nm (?)

- Will we see a different CMOS device in the meantime

- Economics will likely stop it somewhere while still in single digits

- And the nodes will be stretched out

- We will see multi-chip/packaging solutions

- Don't worry: Creativity is unlimited!

- What can you build with 10B/100B/1 trillion transistors?

- Even filling 10B-transistor chips with SRAM is not trivial!

#### This Field

- Focus on principles

- Watch out for opportunities

- Stay current!