# **Assigned Reading**

- R.H. Dennard et al, "Design of ion-implanted MOSFET's with very small physical dimensions" IEEE Journal of Solid-State Circuits, April 1974. • Just the scaling principles

- C.G. Sodini, P.-K. Ko, J.L. Moll, "The effect of high fields on MOS device and circuit performance," IEEE Trans. on Electron Devices, vol. 31, no. 10, pp. 1386 - 1393, Oct. 1984.

- K.-Y. Toh, P.-K. Ko, R.G. Meyer, "An engineering model for short-channel MOS devices" IEEE Journal of Solid-State Circuits, vol. 23, no. 4, pp. 950-958, Aug. 1988.

- T. Sakurai, A.R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," IEEE Journal of Solid-State Circuits, vol. 25, no. 2, pp. 584 - 594, April 1990.

1.C Features of Modern

Technologies

#### Outline

- Scaling issues

- Technology scaling trends

- Features of modern technologies

- Lithography

- Process technologies

### **Technology Features**

- Lithography implications (this lecture)

- Restrictions on design

- Models

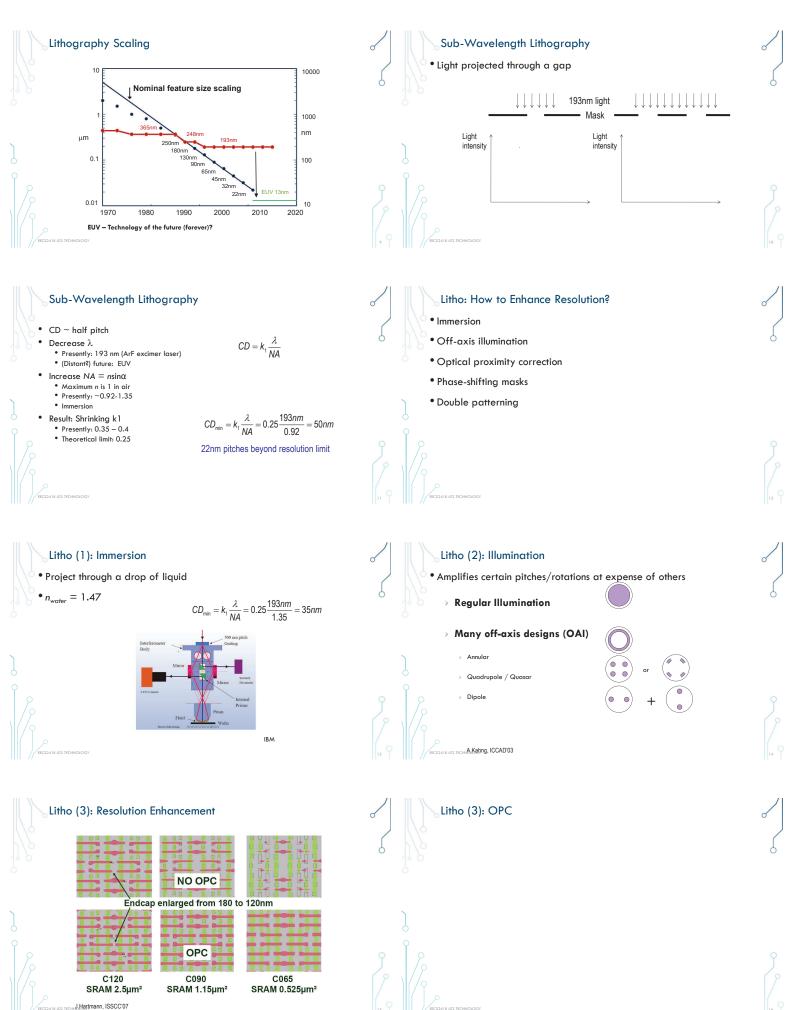

- Lithography Key Points

- Current lithography restricts features in design, affects variability

- This is change with EUV (expected next year in volume) • But that 'next year' has been taking a while to arrive

STEP

- Implications on design variability

- FEOL features (next lecture)

## Pitch-Split Double Exposure

Self-Aligned Double Patterning (SADP)

Also called litho-etch-litho-etch (LELE)

# Litho: Design Implications

- Forbidden directions

- Depends on illumination type

- Poly lines in other directions can exist but need to be thicker

- Forbidden pitches

- Nulls in the interference pattern

- Multiple patterning

- Forbidden shapes in PSM, multiple-patterning

- Assist features

- If a transistor doesn't have a neighbor, let's add a dummy

wafer cost adde

2.5

3.5

4

Multiple patterning

SADP: Double patterning –

SAQP: Quadruple patterning

Two litho-defined lines to form four fins

- NA ~ 1.2-1.35

- EUV lithography

- $\lambda = 13.5$ nm

Normalized

SE LELE

LELELE

SADP

SAQP

EUV SE

EUV SADP

Cost adder reduced with increased power/throughput of EUV

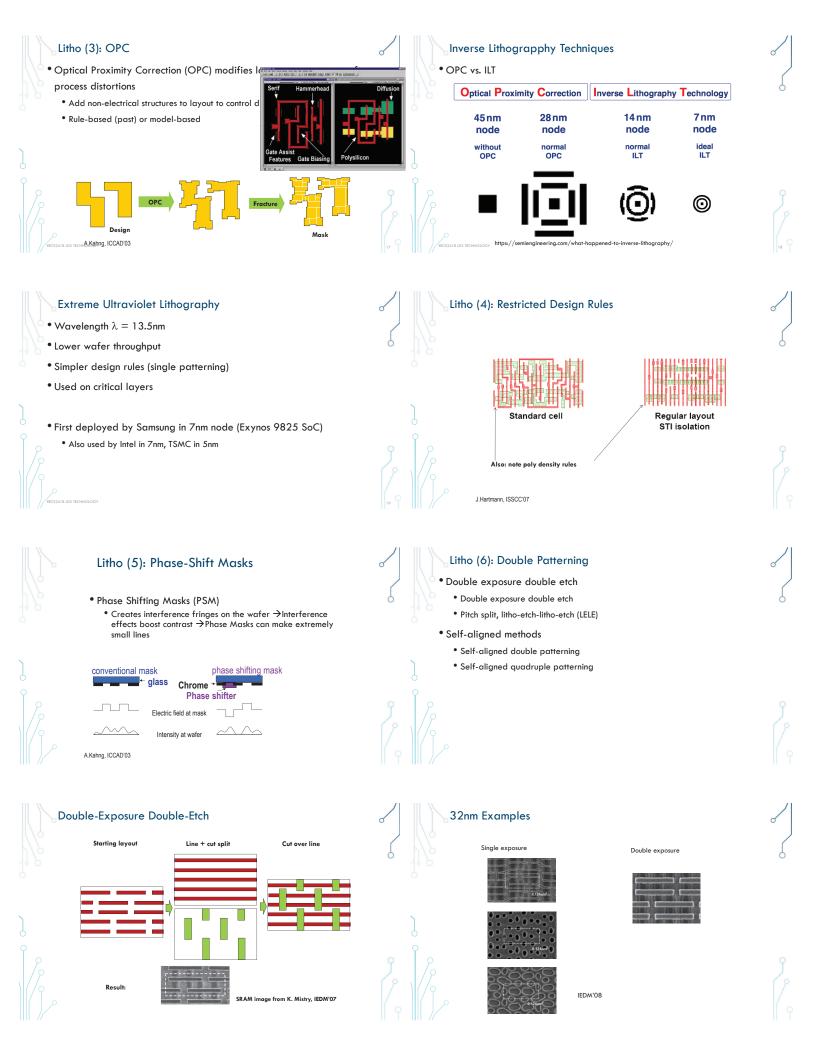

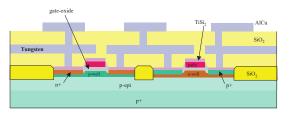

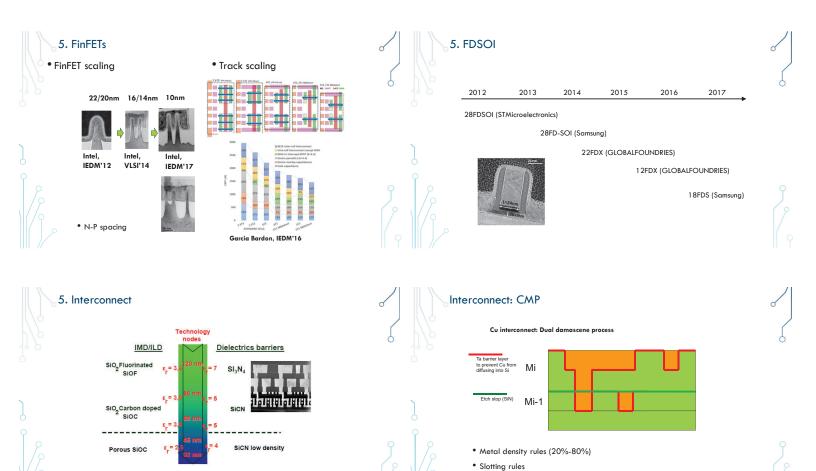

Some of the Process Features 1. Shallow-trench isolation

- 2. High-k/Metal-gate technology

- 3. Strained silicon

- 4. Thin-body devices (28nm, and beyond)

- 5. Copper interconnects with low-k dielectrics

1.D Modern Bulk/finFET/FDSOI processes

1. Shallow Trench Isolation

• Less space needed for isolation

• Some impact on stress

S. Natarajan, IEDM'08

Intel

Compressive channel strain

Tensile channel strain

30% drive current increase

10% drive current increase

in 90nm CMOS

in 90nm CMOS

Intel's Strained Si Numbers

Performance gains:

|       | 90 nm |      | 65 nm |      |

|-------|-------|------|-------|------|

|       | NMOS  | PMOS | NMOS  | PMOS |

| μ     | 20%   | 55%  | 35%   | 90%  |

| IDSAT | 10%   | 30%  | 18%   | 50%  |

| IDLIN | 10%   | 55%  | 18%   | 80%  |

Strained Si

5. Thin-Body Devices • 28nm FDSOI

N. Planes, VLSI'2012

• Also: Antenna rules

• 22/14nm finFET

C. Auth, VLSI'2012

J. Hartmann, ISSCC'07

• Transistor models