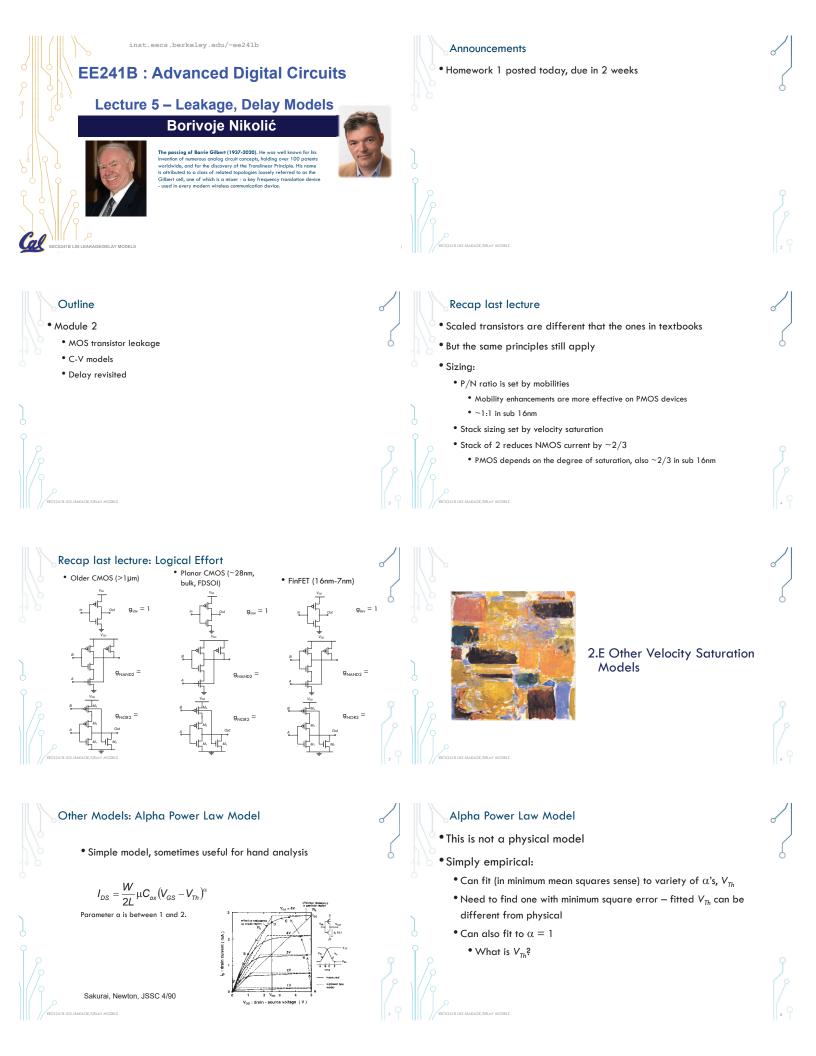

Leakage Components

#### Gate 0 $I_7 I_8$ Source Drain 0-Ð $I_2$ $I_3$ $I_6$ $I_5$ p-well $I_{4}$ Well Q Courtesy of IEEE Press, New York. © 2000

### Leakage Components (250nm)

- pn junction reverse bias current 1.

- 2. Weak inversion

- 3. Drain-induced barrier lowering (DIBL)

- Gate-induced drain leakage (GIDL)

- 5. Punchthrough

4.

- Narrow width effect 6.

- Gate oxide tunneling 7.

- 8 Hot carrier injection

| 1E-7            |                                                                                                                                                                                          |                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1E-7<br>1E-8    | weak inversion + p-njunction + DIBL + GIDL<br>( $@V_D = 3.9V$<br>weak inversion + p-n junction + DIBL<br>( $@V_D = 2.7V$<br>weak inversion + p-n junction<br>(80 mV/dec & $V_D = 0.1V$ ) |                                                                                      |

| 1E-9            |                                                                                                                                                                                          |                                                                                      |

| 1E-10           |                                                                                                                                                                                          |                                                                                      |

| 1E-10-<br>1E-11 |                                                                                                                                                                                          |                                                                                      |

| 1E-12           |                                                                                                                                                                                          |                                                                                      |

| 1E-12<br>1E-13  | p-njunction                                                                                                                                                                              |                                                                                      |

|                 | F) Current in Amps                                                                                                                                                                       | <ol> <li>Nopunchthrough</li> <li>No width effect</li> <li>No gate leakage</li> </ol> |

#### Leakage Components

- Drain-induced barrier lowering (DIBL)

- Voltage at the drain lowers the source potential barrier

- Lowers  $V_{Th}$ , no change on S

- Gate-induced drain leakage (GIDL)

- High field between gate and drain increases injection of carriers into substrate -> leakage (band-to-band leakage)

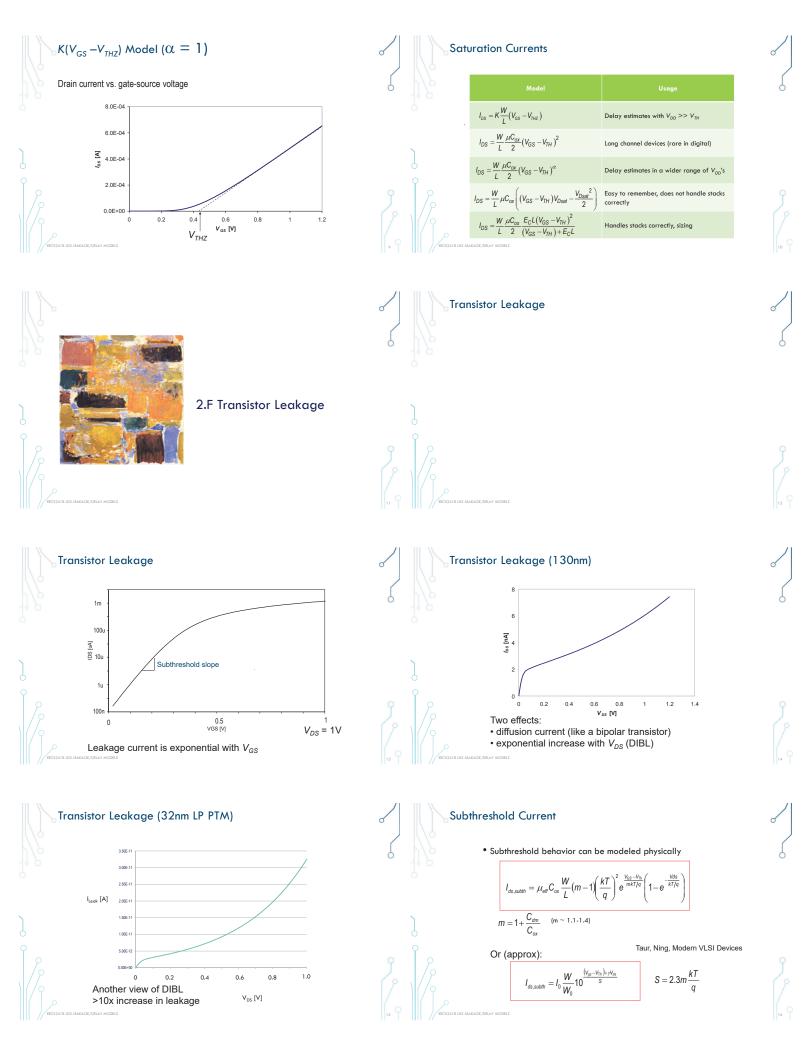

**MOS** Capacitances

• Non-linear channel capacitance

• Linear overlap, fringing capacitances

• Non-linear drain diffusion capacitance

• Miller effect on overlap, fringing capacitance

• Gate capacitance

• PN junction • Wiring capacitances

• Linear

2.H Transistor C-V

#### MOS Transistor as a Switch

Discharging a capacitor

· Can solve:  $i_{DS} = i_{DS} (v_{DS})$  $i_{DS} = C (v_{DS}) \frac{dv_{DS}}{dt}$

Prefer using equivalent resistances  $t_{pHL} = \int \frac{C(v_{DS}) \mathrm{d}v_{DS}}{i_{DS} \left( v_{GS}, v_{DS} \right)}$ Find t<sub>pHL</sub>

Find equivalent C, R

## Gate and Drain Capacitances

Gate capacitance

Gate Capacitances

#### Gate Capacitances

- Gate capacitance is non-linear

- First order approximation with  $C_{ox}WL$  ( $C_{ox}L = 2fF/\mu m$ )

- Need to find the actual equivalent capacitance by simulating it

- Since this is a linear approximation of non-linear function, it is valid only over the certain range

- Different capacitances for HL, LH transitions and power computation

- Drain capacitance non-linearity compensates • But this changes with fanout

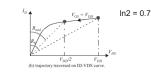

MOS Transistor as a Switch (EECS251A)

$\approx \frac{1}{2}(R_{on}(t_1) + R_{on}(t_2))$

2.1 Delay Revisited

MOS Transistor as a Switch (EE241A)

Solving the integral:

$$R_{eq} = \frac{1}{-V_{DD}/2} \int_{V_{DD}}^{V_{DD}/2} \frac{V}{I_{DSAT}(1+\lambda V)} dV \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left(1 - \frac{7}{9} \lambda V_{DD}\right)$$

with appropriately calculated  $I_{dsat}$

Averaging resistances:

$$R_{eq} = \frac{1}{2} \left( \frac{V_{DD}}{I_{DSAT}(1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT}(1 + \lambda V_{DD}/2)} \right) = \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left( 1 - \frac{5}{6} \lambda V_{DD} \right)$$

Propagation delay:  $t_{pHL} = (\ln 2)R_{eqn}C_L$   $t_{pLH} = (\ln 2)R_{eqp}C_L$

$= \operatorname{average}_{t = t_1 \dots t_2} (R_{on}(t)) = \frac{1}{t_2 - t_1} \int_{t_1}^{t_2} R_{on}(t) dt = \frac{1}{t_2 - t_1} \int_{t_1}^{t_2} \frac{V_{DS}(t)}{I_D(t)} dt$

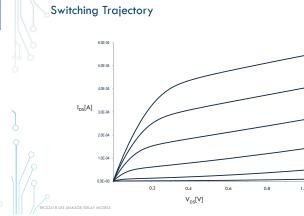

Traversed path

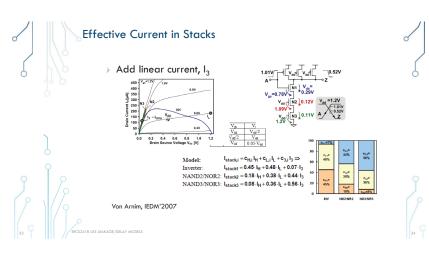

$V_{DD}$

•  $I_{on}(V_{DD})$  is never reached

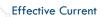

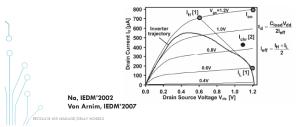

- Define  $I_{eff} = (I_H + I_L)/2$

- $I_{L} = I_{DS}(V_{GS} = V_{DD}/2, V_{DS} = V_{DD}); I_{H} = I_{DS}(V_{GS} = V_{DD}, V_{DS} = V_{DD}/2),$

# • Standard Cells

ECS2418 LOS LEMARCH/DELAY MODELS

35 9

d