## **EE241B: Advanced Digital Circuits**

## Lecture 5 – Leakage, Delay Models

## Borivoje Nikolić

The passing of Barrie Gilbert (1937-2020). He was well known for his invention of numerous analog circuit concepts, holding over 100 patents worldwide, and for the discovery of the Translinear Principle. His name is attributed to a class of related topologies loosely referred to as the Gilbert cell, one of which is a mixer - a key frequency translation device - used in every modern wireless communication device.

## Announcements

Homework 1 posted today, due in 2 weeks

## Outline

- Module 2

- MOS transistor leakage

- C-V models

- Delay revisited

#### Recap last lecture

- Scaled transistors are different that the ones in textbooks

- But the same principles still apply

- Sizing:

- P/N ratio is set by mobilities

- Mobility enhancements are more effective on PMOS devices

- ~1:1 in sub 16nm \; 6.9

- Stack sizing set by velocity saturation

- Stack of 2 reduces NMOS current by  $\sim 2/3$

- $^{ullet}$  PMOS depends on the degree of saturation, also  $\sim\!2/3$  in sub 16nm

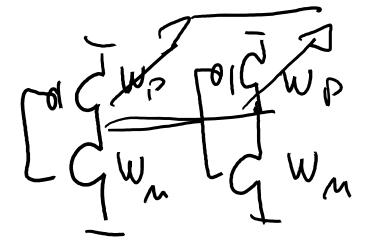

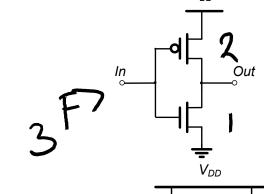

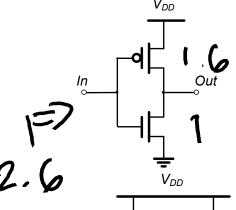

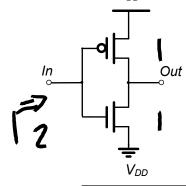

## Recap last lecture: Logical Effort

• Older CMOS (>1µm)

Planar CMOS (~28nm, bulk, FDSOI)

• FinFET (16nm-7nm)

$$g_{inv} = 1$$

$$g_{inv} = 1$$

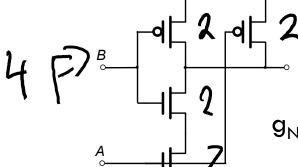

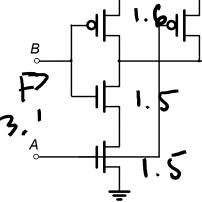

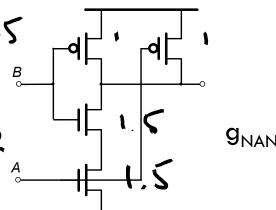

$$_{NAND2} = \frac{4}{3} = 1.37$$

$$g_{NAND2} = \frac{3!}{2!6!}$$

$$g_{NAND2} = \frac{2.5}{2} = 1.25$$

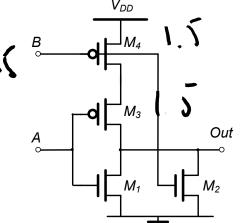

$$g_{NOR2} = \frac{1}{3}$$

$$A = \frac{1}{3}$$

$$M_1 = \frac{1}{3}$$

$$M_2 = \frac{1}{3}$$

$$\begin{array}{c|c}

& V_{DD} \\

\hline

& M_4 \\

\hline

& M_2 \\

\hline

& M_2

\end{array}$$

$$g_{NOR2} = \frac{2.5}{7} = 1.25$$

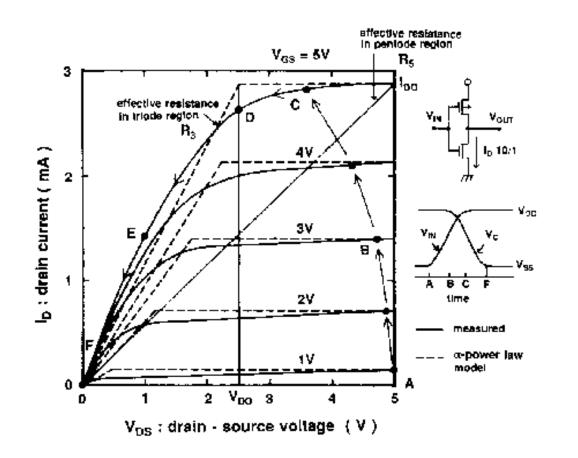

# 2.E Other Velocity Saturation Models

## Other Models: Alpha Power Law Model

Simple model, sometimes useful for hand analysis

$$I_{DS} = \frac{W}{2L} \mu C_{ox} (V_{GS} - V_{Th})^{\alpha}$$

Parameter a is between 1 and 2.

Sakurai, Newton, JSSC 4/90

## Alpha Power Law Model

- This is not a physical model

- Simply empirical:

- $^{\bullet}$  Can fit (in minimum mean squares sense) to variety of  $\alpha$  's,  $V_{\textit{Th}}$

- Need to find one with minimum square error fitted  $V_{Th}$  can be different from physical

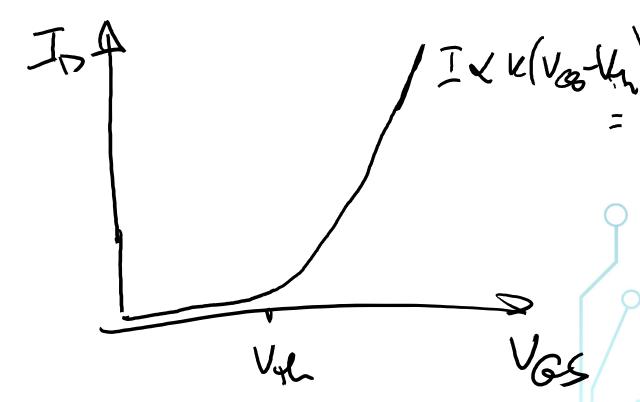

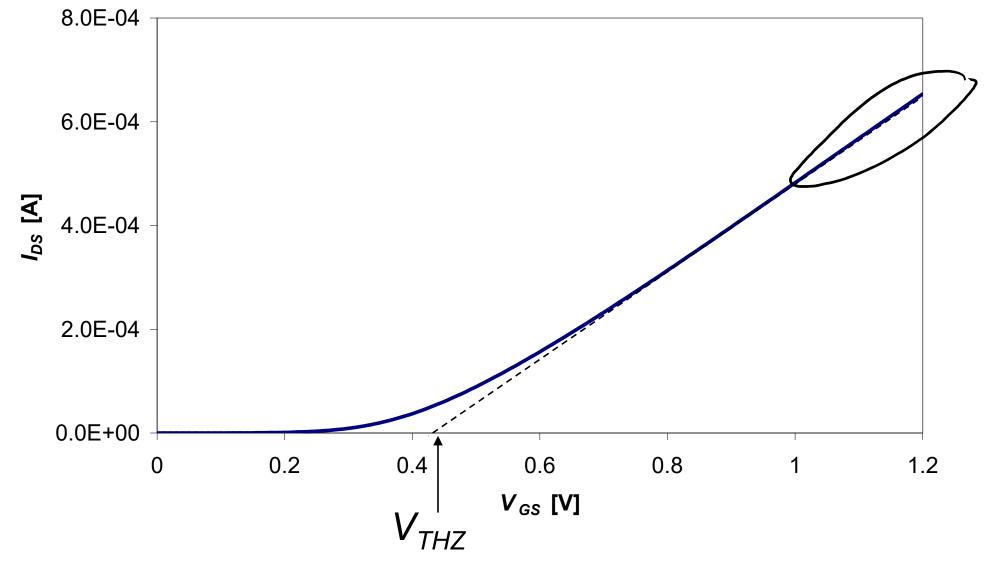

- $\bullet$  Can also fit to  $\alpha = 1$

- What is  $V_{Th}$ ?

$\int_{-\infty}^{\infty} K(V_{GS} - V_{THZ}) \text{ Model } (\alpha = 1)$

Drain current vs. gate-source voltage (28 )

## Saturation Currents

| Model                                                                                                   | Usage                                              |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| $I_{DS} = K \frac{W}{L} (V_{GS} - V_{THZ})$                                                             | Delay estimates with $V_{DD} >> V_{TH}$            |

| $I_{DS} = \frac{W}{L} \frac{\mu C_{OX}}{2} (V_{GS} - V_{TH})^2$                                         | Long channel devices (rare in digital)             |

| $I_{DS} = \frac{W}{L} \frac{\mu C_{ox}}{2} (V_{GS} - V_{TH})^{\alpha}$                                  | Delay estimates in a wider range of $V_{DD}$ 's    |

| $I_{DS} = \frac{W}{L} \mu C_{ox} \left( (V_{GS} - V_{TH}) V_{Dsat} - \frac{V_{Dsat}^2}{2} \right)$      | Easy to remember, does not handle stacks correctly |

| $I_{DS} = \frac{W}{L} \frac{\mu C_{ox}}{2} \frac{E_C L (V_{GS} - V_{TH})^2}{(V_{GS} - V_{TH}) + E_C L}$ | Handles stacks correctly, sizing                   |

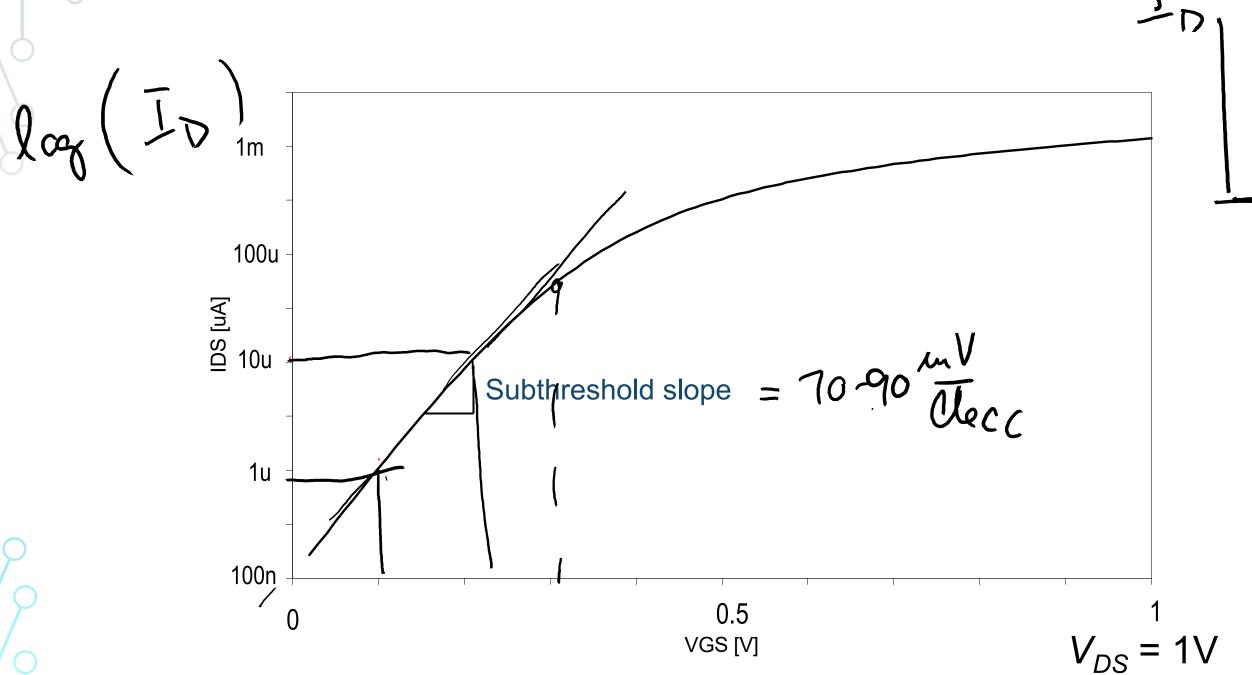

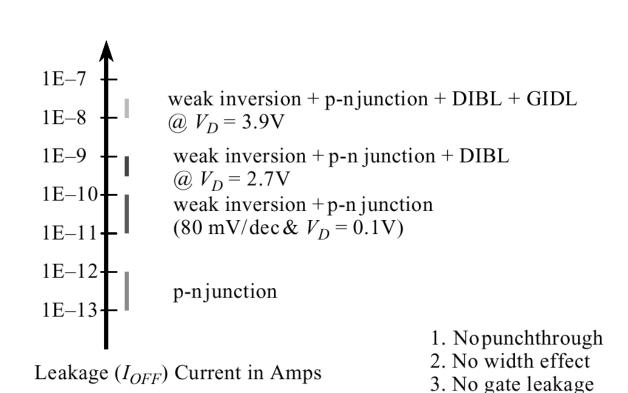

## 2.F Transistor Leakage

ideal S = 60mV/dec proectica buk proectica S = 90-95

Leakage current is exponential with  $V_{GS}$

Two effects:

- diffusion current (like a bipolar transistor)

- exponential increase with  $V_{DS}$  (DIBL)

## Transistor Leakage (32nm LP PTM)

EECS241B LO5 LEAKAGE/DELAY MODELS

15

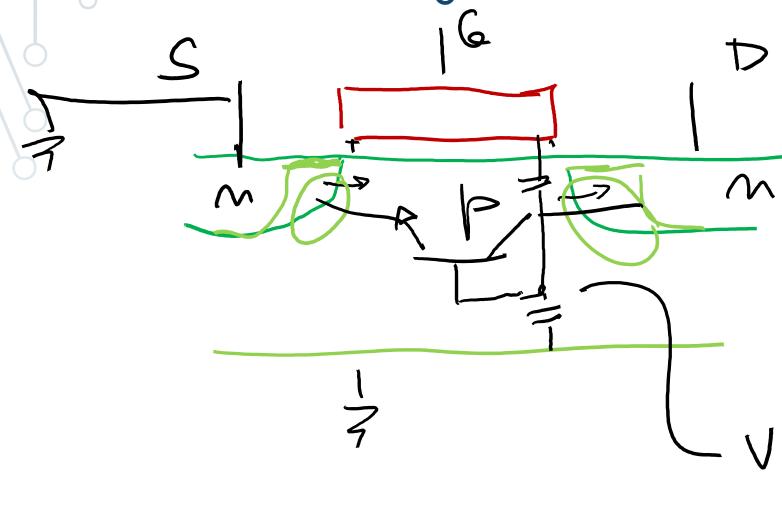

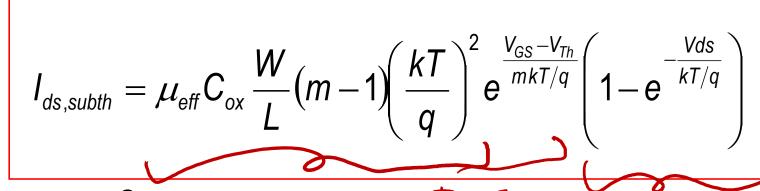

#### Subthreshold Current

$$m = 1 + \frac{C_{dm}}{C_{ox}} \quad (m \sim 1.1-1.4)$$

$$Taur Ning Modern$$

Or (approx):

$$I_{ds,subth} = I_0 \frac{W}{W_0} 10^{\frac{(V_{gs} - V_{Th}) + \gamma V_{ds}}{S}}$$

Taur, Ning, Modern VLSI Devices

$$S = 2.3m \frac{kI}{q}$$

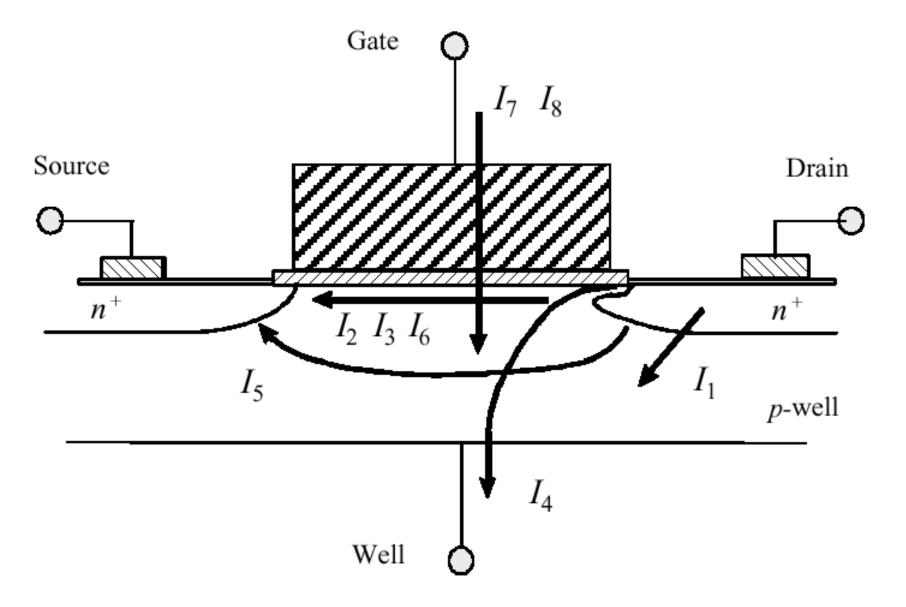

## Leakage Components

Courtesy of IEEE Press, New York. © 2000

## Leakage Components (250nm)

- 1. pn junction reverse bias current

- 2. Weak inversion

- 3. Drain-induced barrier lowering (DIBL)

- 4. Gate-induced drain leakage (GIDL)

- 5. Punchthrough

- 6. Narrow width effect

- 7. Gate oxide tunneling

- 8. Hot carrier injection

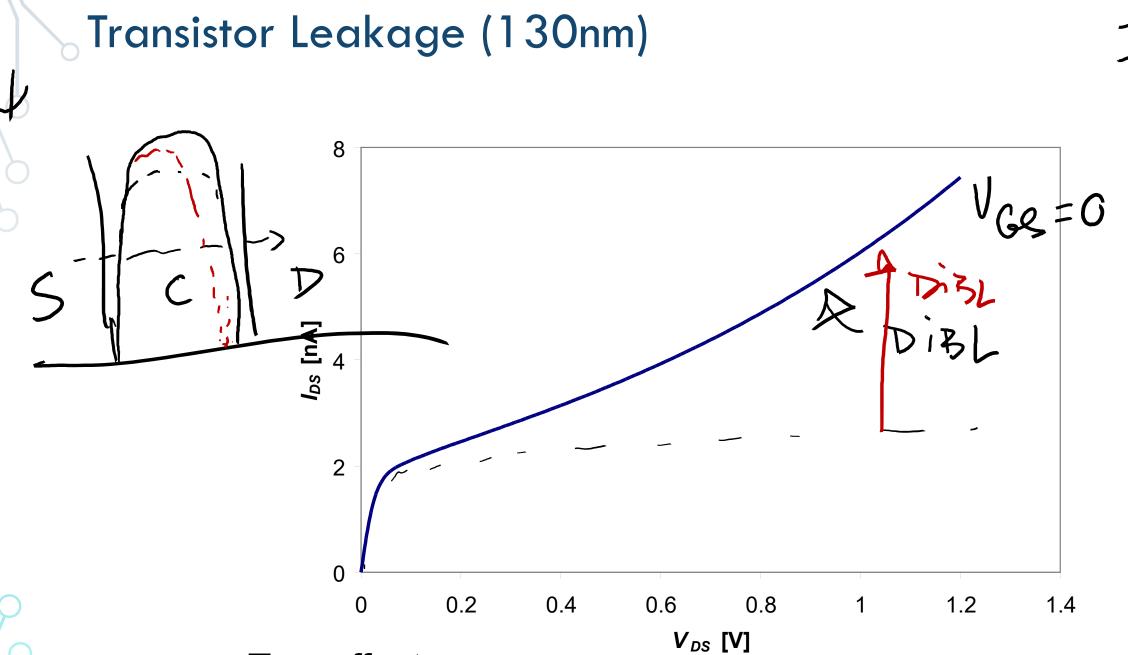

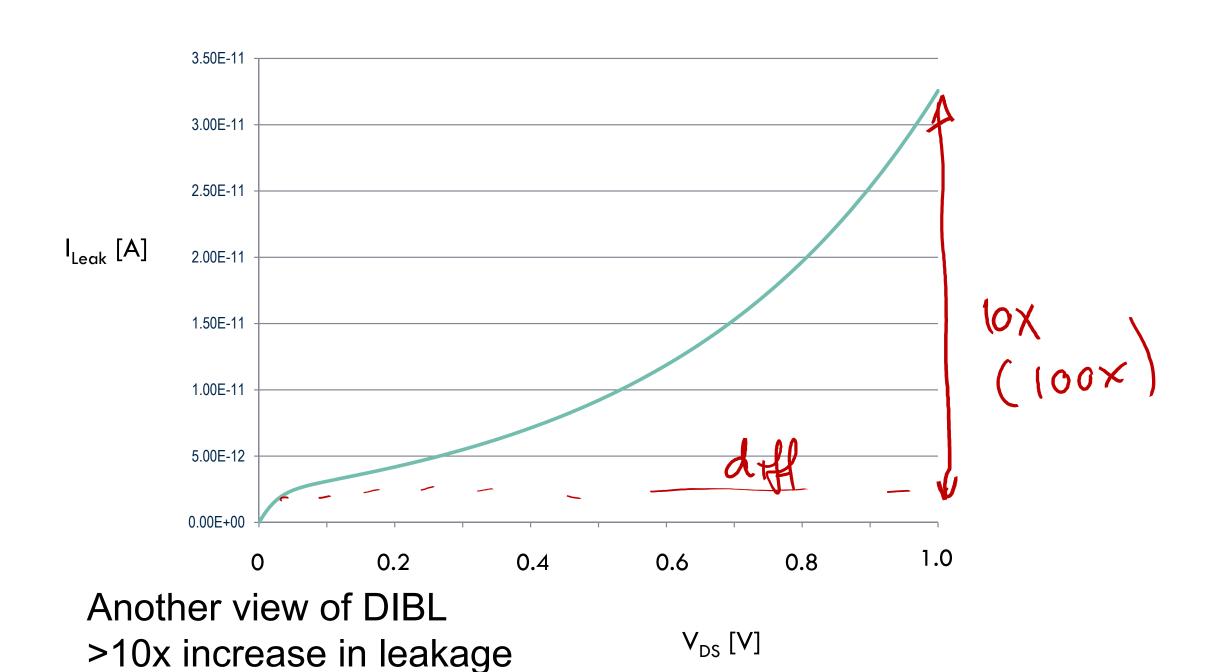

#### Leakage Components

- Drain-induced barrier lowering (DIBL)

- Voltage at the drain lowers the source potential barrier

- Lowers  $V_{Th}$ , no change on S

- Gate-induced drain leakage (GIDL)

- High field between gate and drain increases injection of carriers into substrate -> leakage

(band-to-band leakage)

substitute bios

V68 40

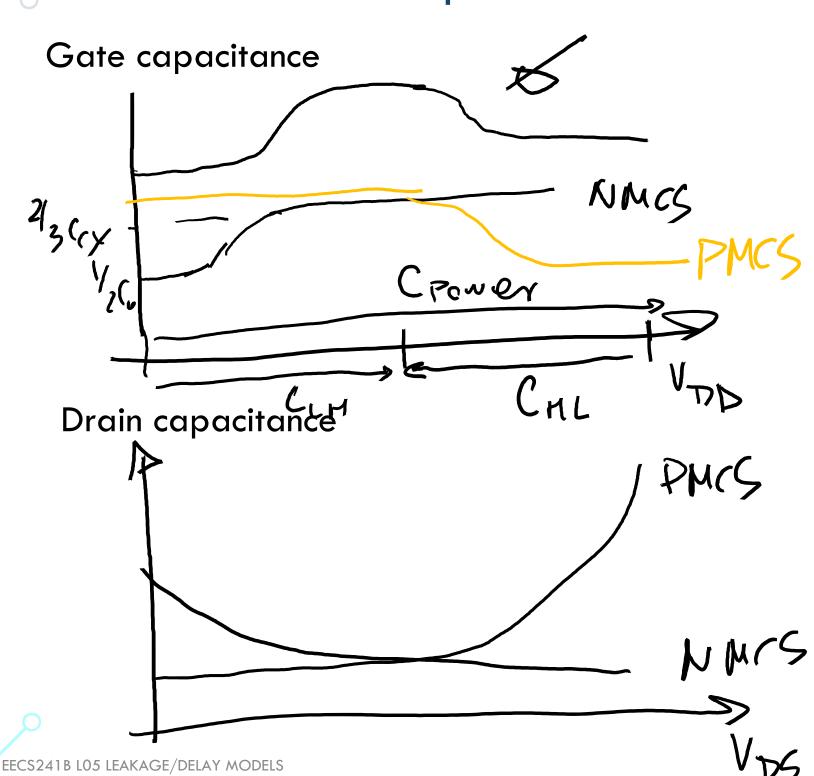

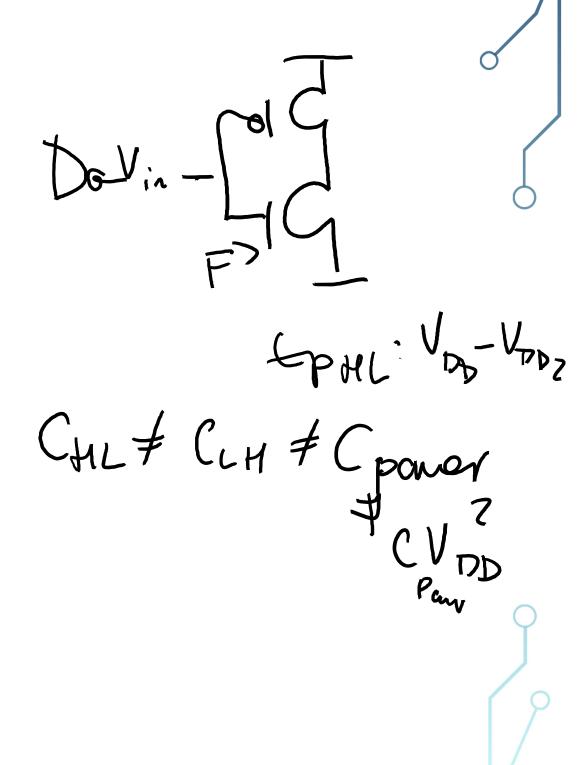

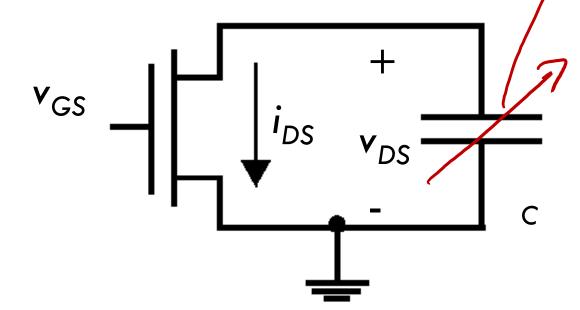

## 2.H Transistor C-V

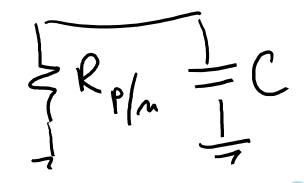

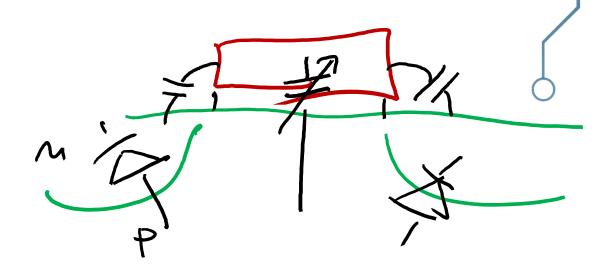

#### MOS Transistor as a Switch

gdes + wires

Discharging a capacitor

• Can solve:

$$i_{DS} = i_{DS} (v_{DS})$$

$$i_{DS} = C(v_{DS}) \frac{dv_{DS}}{dt}$$

- Prefer using equivalent resistances

- Find  $t_{pHL}$

- Find equivalent C, R

$$t_{pHL} = \int \frac{C(v_{DS}) dv_{DS}}{i_{DS} (v_{GS}, v_{DS})}$$

## **MOS** Capacitances

- Gate capacitance

- Non-linear channel capacitance

- Linear overlap, fringing capacitances

- Miller effect on overlap, fringing capacitance

- Non-linear drain diffusion capacitance

- PN junction

- Wiring capacitances

- Linear

## Gate and Drain Capacitances