inst.eecs.berkeley.edu/~ee241b

# **EE241B : Advanced Digital Circuits**

# Lecture 8 – Technology Variability Borivoje Nikolić

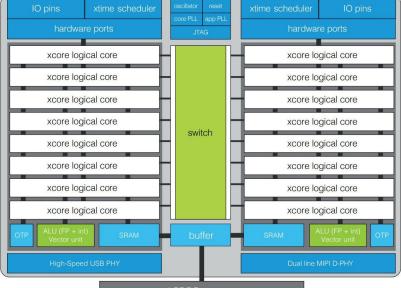

February 2, 2020, EETimes: XMOS adapts Xcore into AloT 'crossover processor'

The new chip targets Al-powered voice interfaces in IoT devices — "the most important AI workload at the endpoint.".

ECS241B L08 TECHNOLOGY VARIABILITY

LPDDR memory

## Announcements

- Homework 1 due on February 17

- No class on February 18 (ISSCC)

- Project abstracts due on February 20

- Teams of 2

- Title

- One paragraph

- 5 relevant references

- Can also combine with CS252 or EE290 projects

## Outline

- Module 2

- Technology variability

# 2.N Static Timing

## Static Timing Analysis

- Computing critical (longest) and shortest path delay

- Longest path algorithm on DAG [Kirkpatrick, IBM Jo. R&D, 1966]

- Used in most ASIC designs today

- Limitations

- False paths

- Simultaneous arrival times

- Derate

## **False Paths**

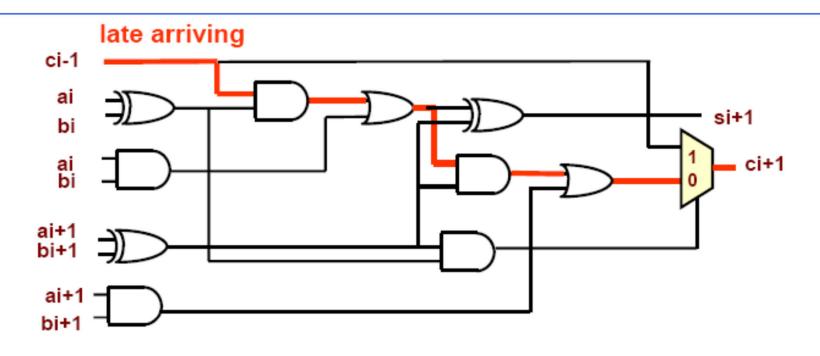

## Inside Carry Bypass Adder - 1

Longest graphical/topological path runs along carry chain from stage to stage

Longest path analysis would identify red path as critical

## Static Timing - Summary

- Enables design of complex systems

- Simpler, less accurate models are used during design

- More accurate models are used for 'signoff'

- See more in labs!

# 2.0 Design Variability Sources and Impact on Design

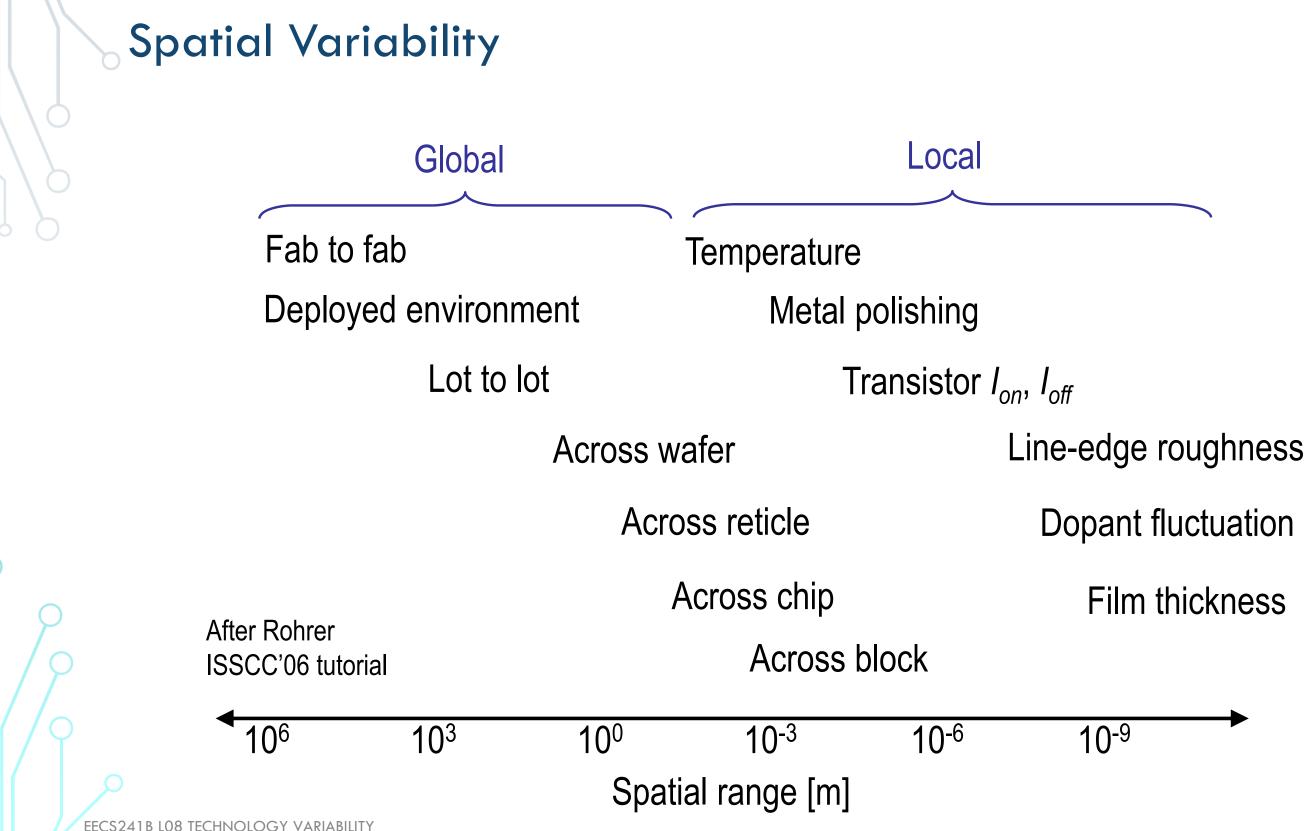

## Variability Classification

- Nature of process variability

- Within-die (WID), Die-to-die (D2D), Wafer-to-wafer (W2W), Lot-to-lot (L2L)

- Systematic vs. random

- Correlated vs. non-correlated

- Spatial variability/correlation

- Device parameters (CD,  $t_{ox}$ , ...)

- Supply voltage, temperature

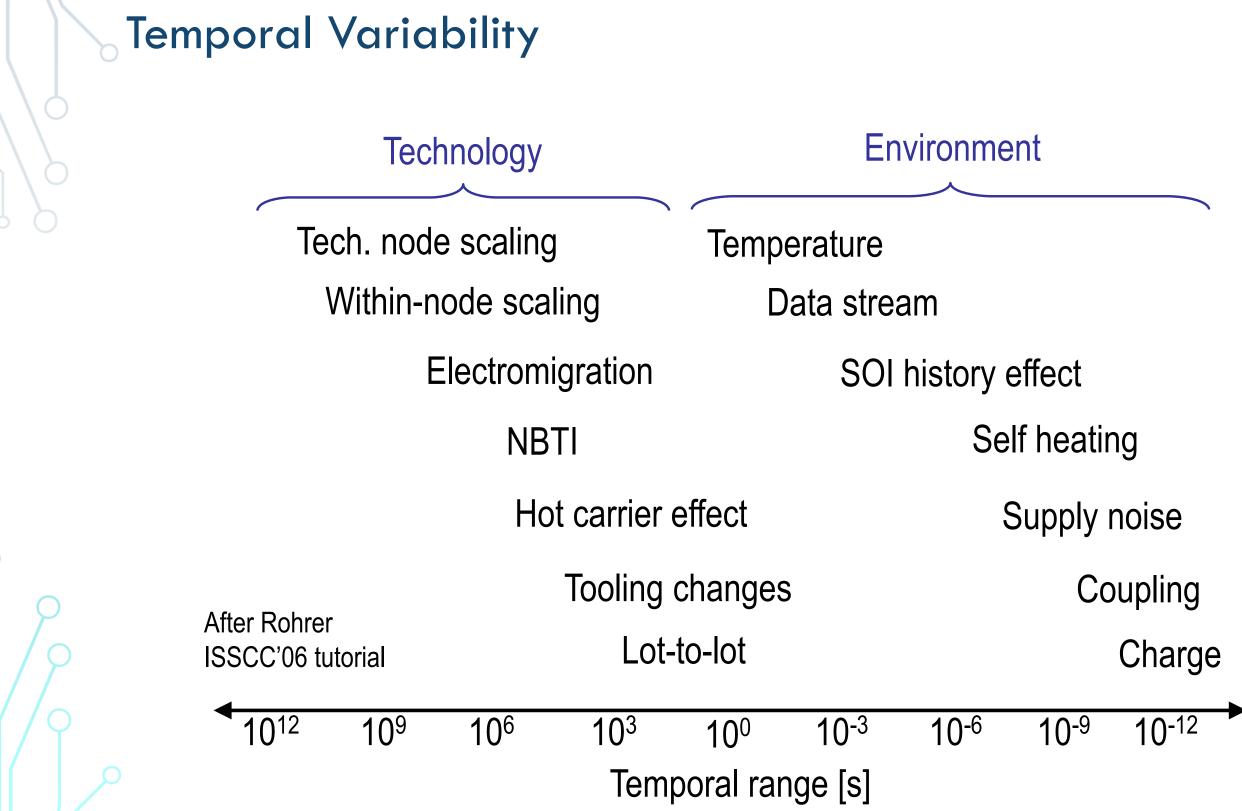

- Temporal variability/correlation

- Within-node scaling, Electromigration, Hot-electron effect, NBTI, self-heating, temperature, SOI history effect, supply voltage, crosstalk [Bernstein, IBM J. R&D, July/Sept 2006]

- Known vs. unknown

- Goal of model-to-hw correlation is to reduce the unknowns

## Sources of Variability

- Technology

- Front-end (Devices)

- Systematic and random variations in lon, loff, C, ...

- Back-end (Interconnect)

- Systematic and random variations in R, C

- Environment

- Supply (IR drop, noise)

- Temperature

Film thickness

hnology variability

## Systematic vs. Random Variations

- Systematic

- A systematic pattern can be traced down to lot-to-lot, wafer-to-wafer, within reticle, within die, from layout to layout,...

- Within-die: usually spatially correlated

- Random

- Random mismatch (dopant fluctuations, line edge roughness,...)

- Things that are systematic, but e.g. change with a very short time constant (for us to do anything about it). Or we don't unedrstand it well enough to model it as systematic. Or we don't know it in advance ("How random is a coin toss?").

- Unknown

## Systematic and Random Device Variations

| Parameter                                             | Random                                                                                | Systematic                                                                                       |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Channel Dopant<br>Concentration Nch                   | Affects σ <sub>VT</sub> <sup>[1]</sup>                                                | Non uniformity in the process of dopant implantation, dosage, diffusion                          |

| Gate Oxide Thickness<br>Tox                           | Si/SiO <sub>2</sub> & SiO <sub>2</sub> /Poly-Si<br>interface roughness <sup>[2]</sup> | Non uniformity in the process of oxide growth                                                    |

| Threshold Voltage V <sub>T</sub><br>(non Nch related) | Random anneal temperature and strain effects                                          | Non-uniform annealing temperature <sup>[5]</sup><br>(metal coverage over gate)<br>Biaxial strain |

| Mobility $\mu$                                        | Random strain distributions                                                           | Systematic variation of strain in the S to STI, S/D area, contacts, gate dens                    |

| Gate Length L                                         | Line edge roughness (LER) <sup>[3]</sup>                                              | Lithography and etching:<br>Proximity effects, orientation <sup>[4]</sup>                        |

| Fin geometry/<br>film thickness<br>variations         | Rounding, etc, $6_{VT}$ , mobility.                                                   | Systematic fin thickness<br>Systematic Si film/BOX variations                                    |

[1] D. Frank et al, VLSI Symposium, Jun. 1999 . [2] A. Asenov et al, IEEE Trans on Electron Devices, Jan. 2002.

EECS241B LOB TEST P. Oldiges et al, SISPAD 2000, Sept. 2000. [4] M. Orshansky et al, IEEE Trans on CAD, May 2002. [5] Tuinhout et al, IEDM, Dec 1996

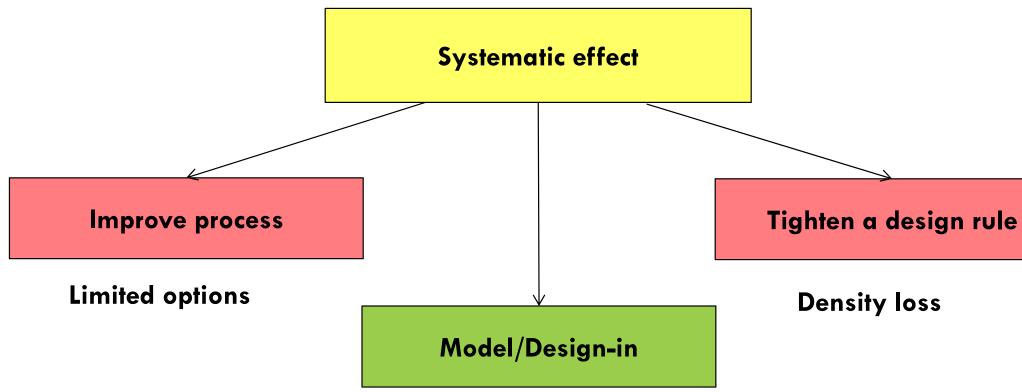

## **Dealing with Systematic Variations**

Model-to-hardware correlation classifies unknown sources

Extraction/Compact modeling/Design techniques

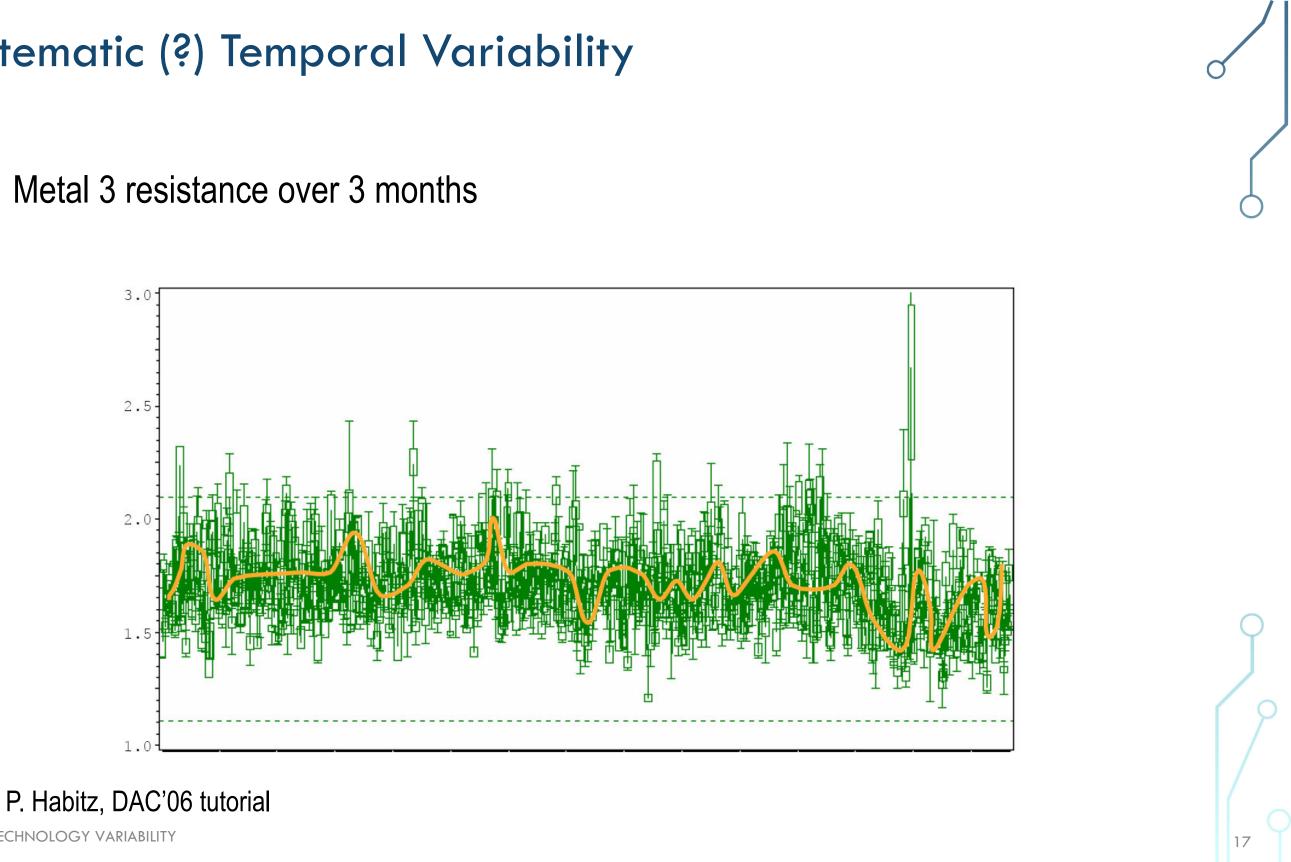

## Systematic (?) Temporal Variability

Metal 3 resistance over 3 months

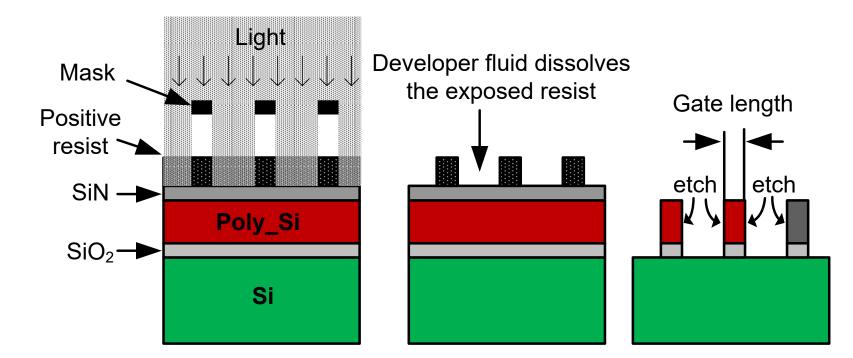

# 2.P Design Variability Some Systematic Effects

Layout: Poly Proximity Effects

Gate CD is a function of its neighborhood

## Gate length depends on

- Light intensity profile falling on the resist

- Resist: application of developer fluid<sup>[1]</sup>, post exposure bake (PEB) temperature<sup>[2]</sup>

- Dry etching: microscopic loading effects<sup>[3]</sup>

- [1] J.Cain, M.S. Thesis, UC Berkeley

- [2] D. Steele et al, SPIE, vol.4689, July 2002.

- [3] J. D. Plummer, M.D. Deal, P.B. Griffin, Silicon VLSI Technology, Prentice-Hall, 2000.

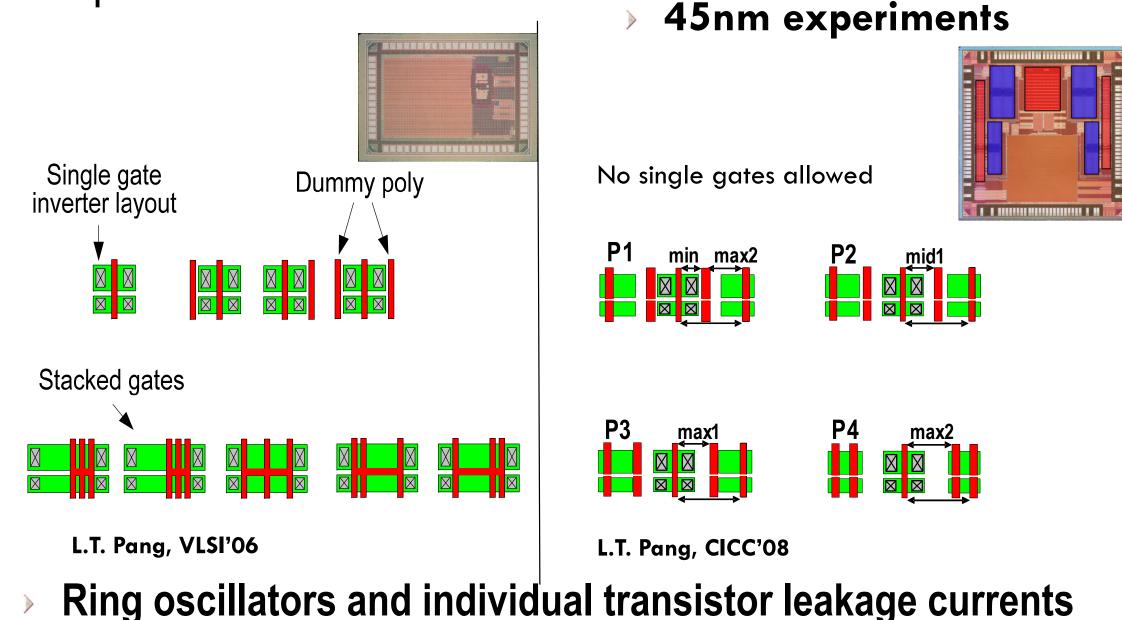

Layout: Proximity Test Structures

• 90nm experiments

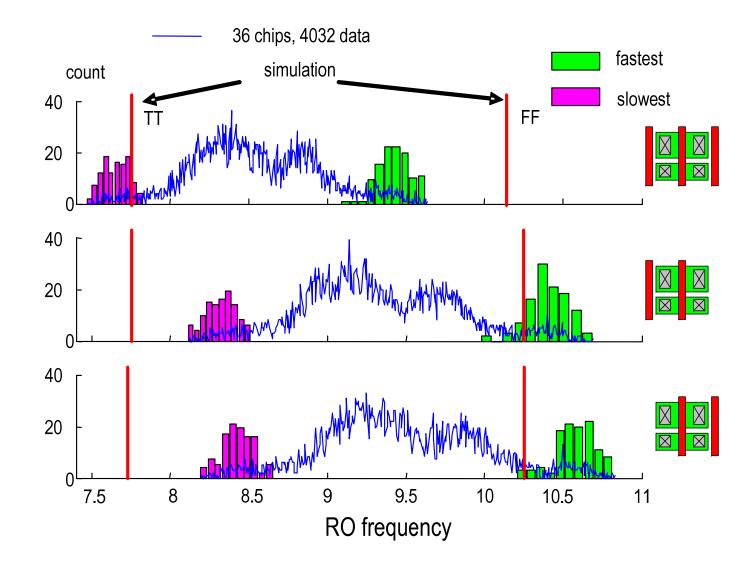

## Results: Single Gates in 90nm

- Max  $\Delta F$  between layouts > 10%

- Within-die  $3\sigma/\mu \sim 3.5\%$ , weak dependency on density

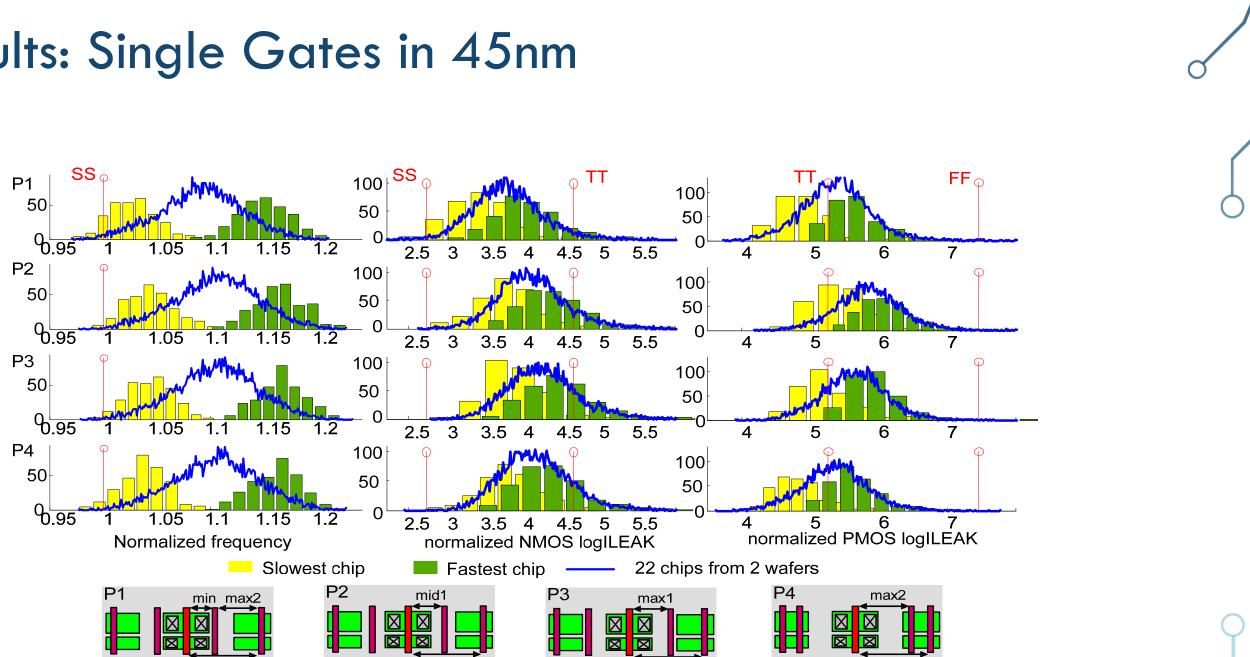

## Results: Single Gates in 45nm

- Weak effect on performance.  $\Delta F \sim 2\%$

- Small shifts in NMOS leakage and bigger shifts in PMOS leakage

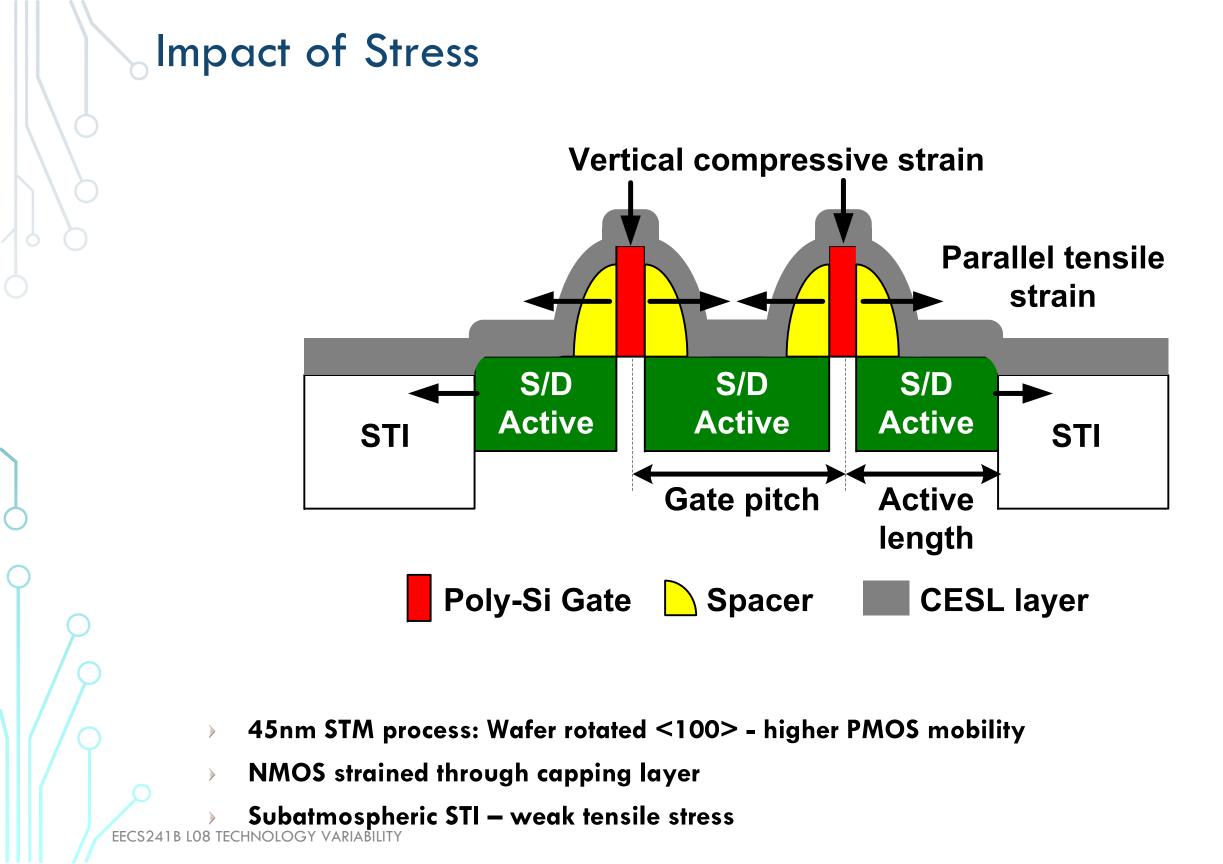

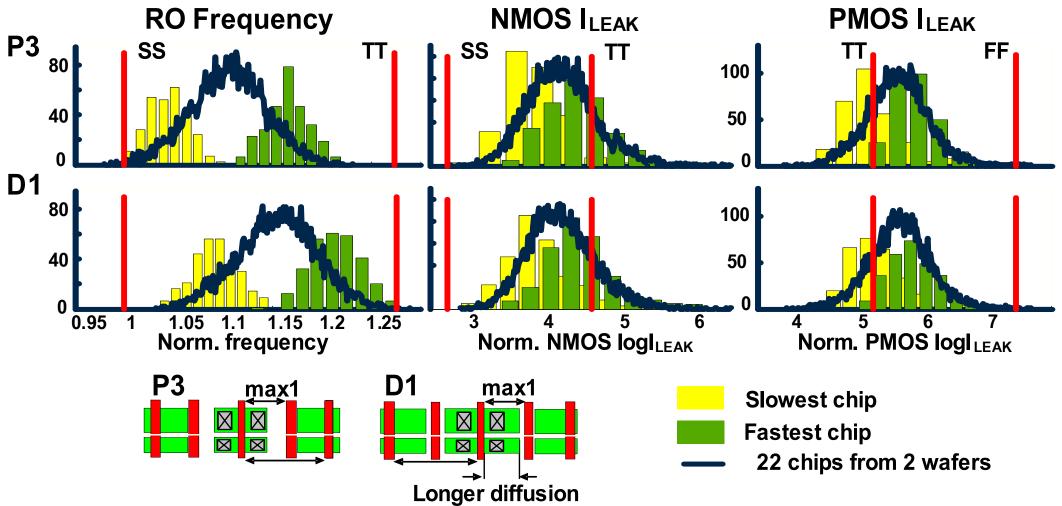

## Impact of Longer Diffusion in 45nm

- Strongest effect measured in 45nm,  $\Delta F \sim 5\%$ •

- No significant shift in I<sub>LEAK</sub> ۲

24

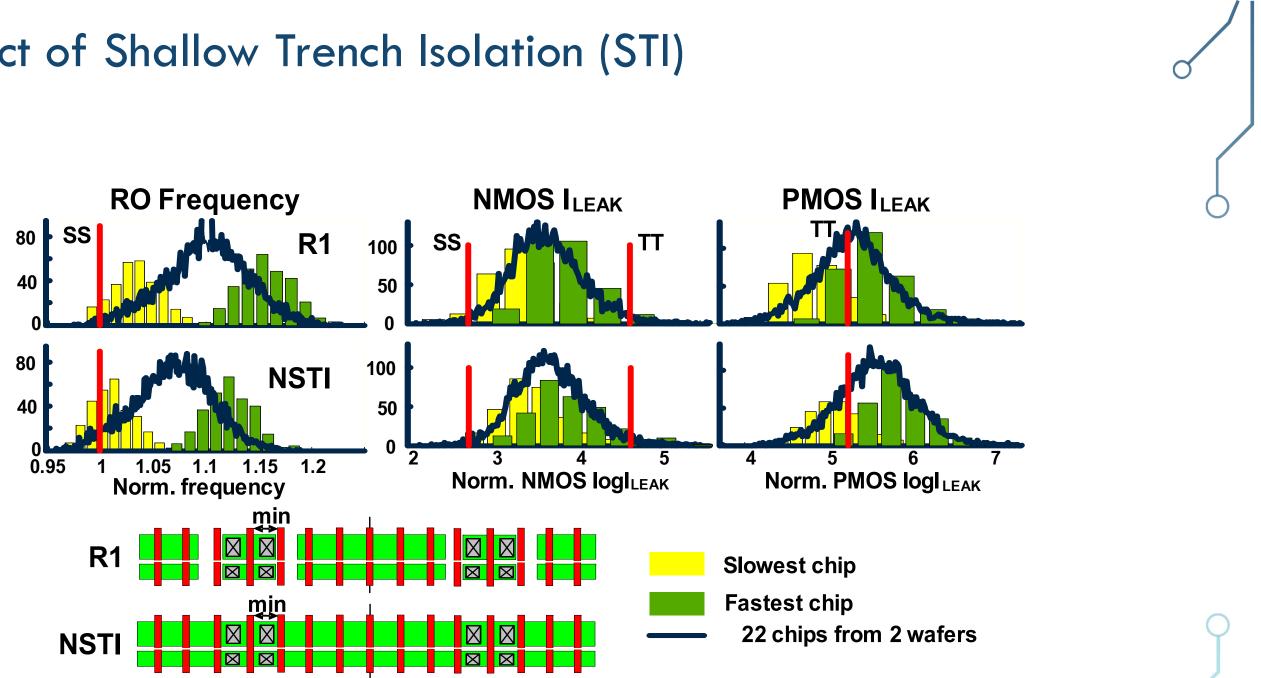

## Impact of Shallow Trench Isolation (STI)

- $\Delta F \sim 3\%$ , small changes in  $I_{LEAK}$ •

- Due to STI-induced stress •

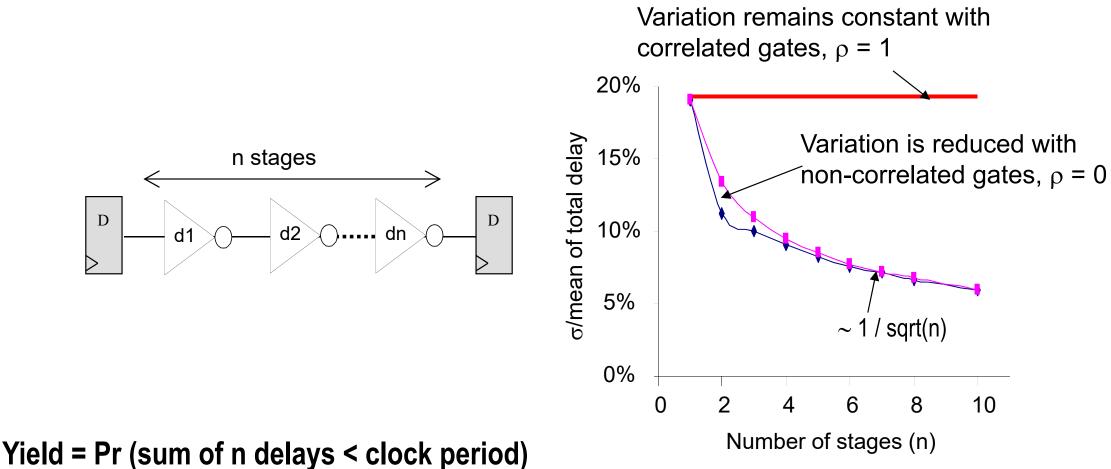

## Chip Yield Depends on Inter-Gate Correlation

$\rho$  = 0 gives highest yield through averaging

Non-correlated gates in a path reduce impact of variation

Bowman et al, JSSC, Feb 2002.

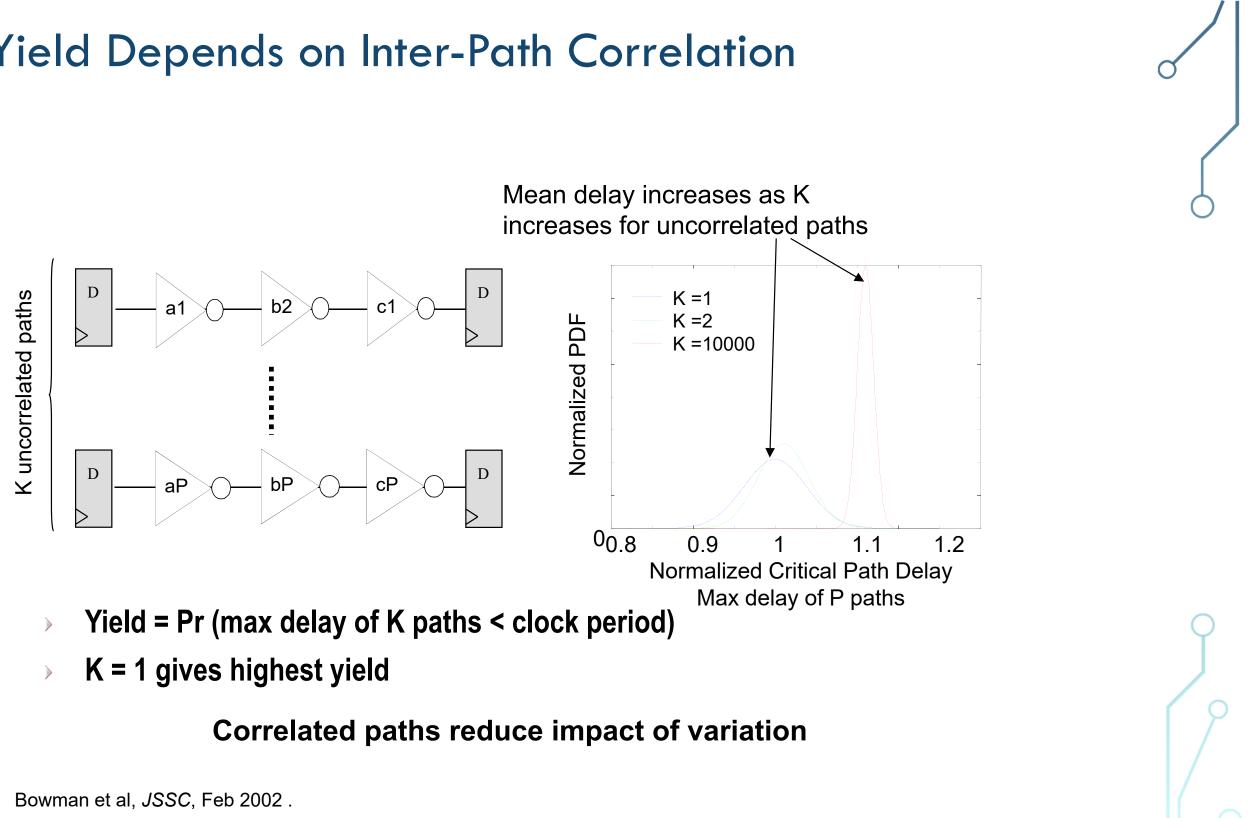

## Chip Yield Depends on Inter-Path Correlation

28

# 2.P Design Variability Some Random Effects

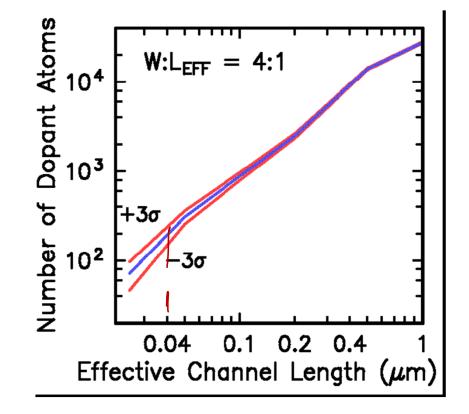

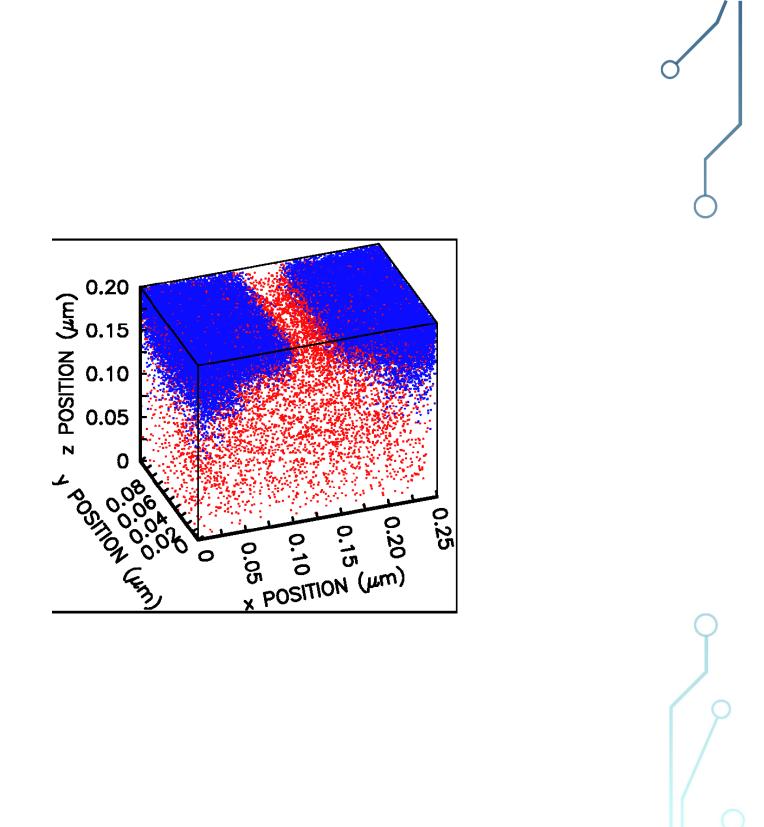

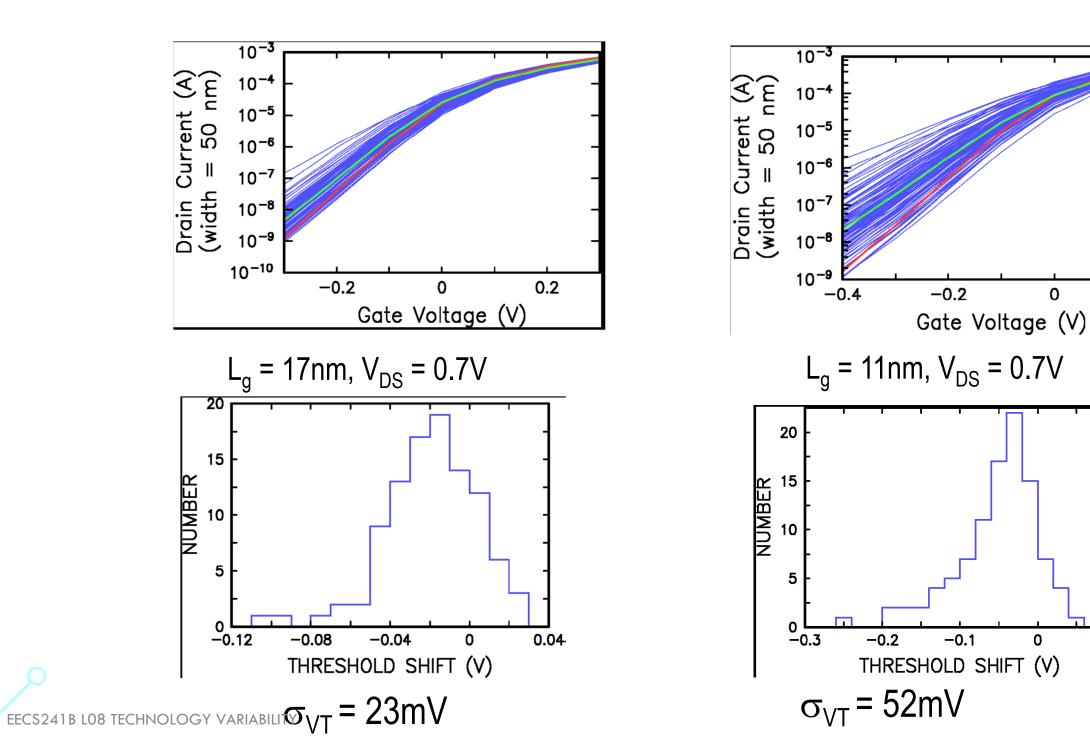

## **Random Dopant Fluctuations**

• Number of dopants is finite

30

## **Random Dopant Fluctuations**

31

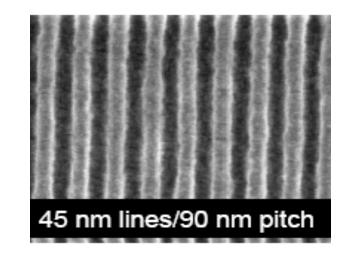

## Processing: Line-Edge Roughness

•Sources of line-edge roughness:

- Fluctuations in the total dose due to quantization

- Resist composition

- Absorption positions Effect:

- Variation (random) in leakage and power

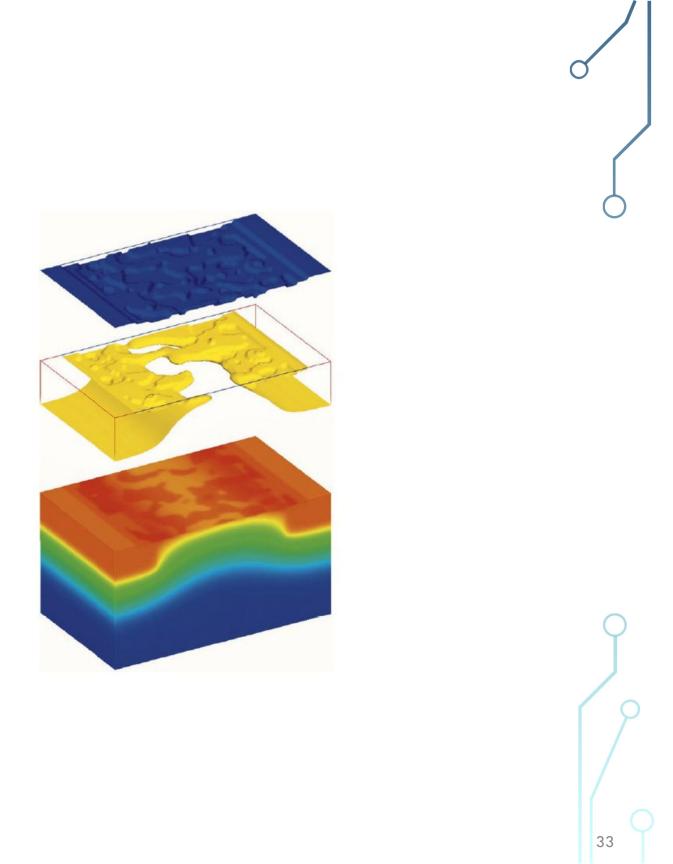

## **Oxide Thickness**

- Systematic variations +

- Roughness in the Si./SiO2 interface

- Smaller effect than RDF

## Asenov, TED'2002

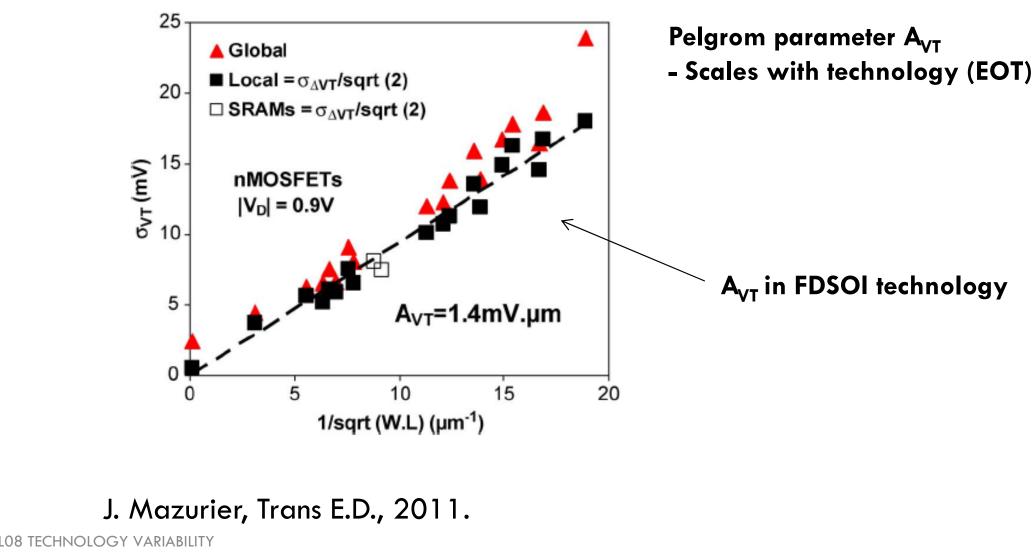

**Transistor Matching**

EECS241B

V<sub>Th</sub> matching of geometrically identical transistors varies with size  $\sim \sqrt{WL}$  and distance

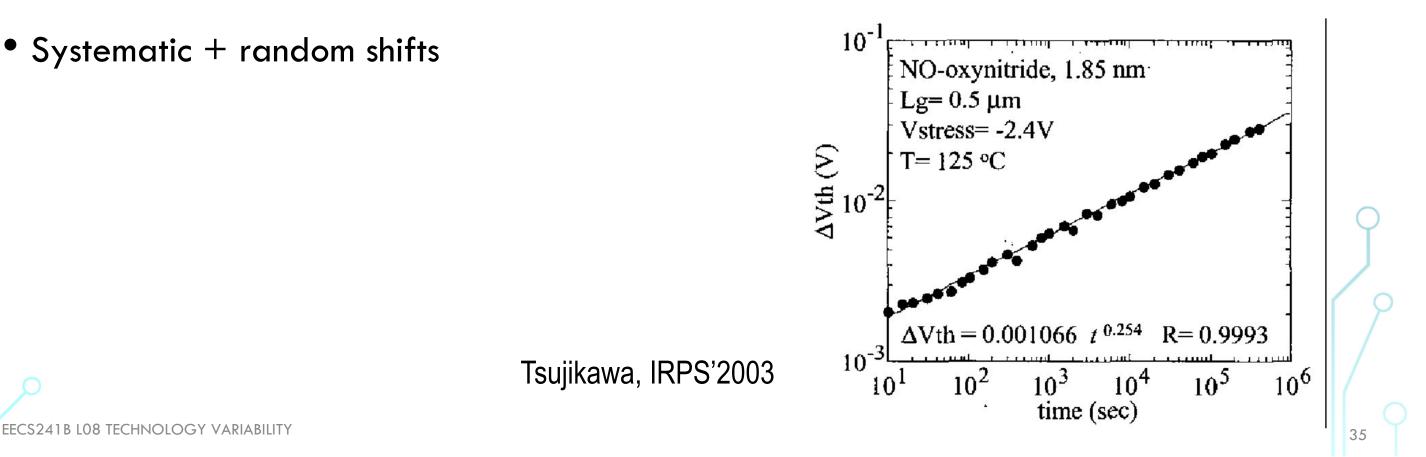

## Negative Bias Temperature Instability

- PFET  $V_{Th}$ 's shift in time, at high negative bias and elevated temperatures

- The mechanism is thought to be the breaking of hydrogen-silicon bonds at the Si/SiO2 interface, creating surface traps and injecting positive hydrogen-related species into the oxide.

- Also other charge trapping and hot-carrier defect generation

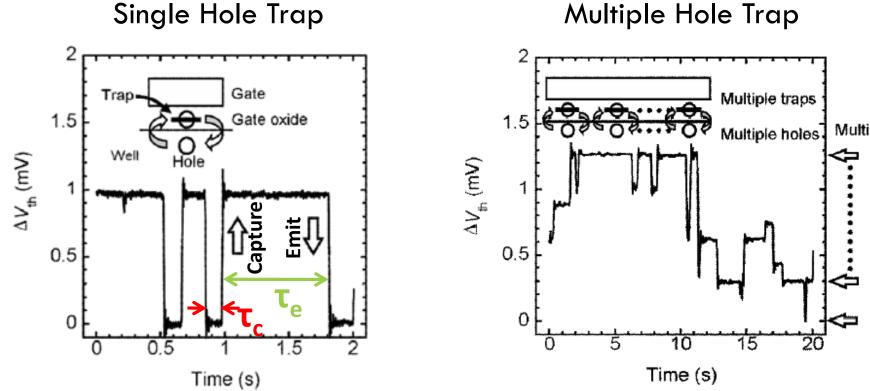

## Random Telegraph Signal (RTS)

• Trapping of a carrier in oxide traps modulates  $V_{th}$  or  $I_{ds}$

•  $\tau_e$  and  $\tau_c$  are random and follow exponential distributions

EECS241B LOONTECHEROLOCYALARABIET 2008.

Multiple states

RTS and Technology Scaling

• RTS exceeds RDF at 3 sigma with 20nm gates

1

Tega et. al, VLSI Tech. 09

∆Vth (mV)

## Next Lecture

- Timing and design for performance

- After ISSCC