# EE C245 - ME C218 Introduction to MEMS Design Fall 2008

Prof. Clark T.-C. Nguyen

Dept. of Electrical Engineering & Computer Sciences

University of California at Berkeley

Berkeley, CA 94720

Lecture 27: Noise & Integration

#### Lecture Outline

- \* Reading: Senturia, Chpt. 16

- Lecture Topics:

- ♦ Noise

- **MEMS/Transistor Integration**

- ∜ Wrap Up

- Final Exam

- ◆ Next Week

#### Noise

EE C245: Introduction to MEMS Design

## UC Berkeley

#### Noise

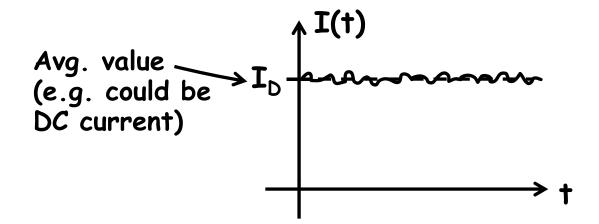

- Noise: Random fluctuation of a given parameter I(t)

- In addition, a noise waveform has a zero average value

- We can't handle noise at instantaneous times

- But we can handle some of the averaged effects of random fluctuations by giving noise a power spectral density representation

- Thus, represent noise by its mean-square value:

Let

$$i(t) = I(t) - I_D$$

Then

$$\overline{i^2} = \overline{(I - I_D)^2} = \lim_{T \to \infty} \frac{1}{T} \int_0^T |I - I_D|^2 dt$$

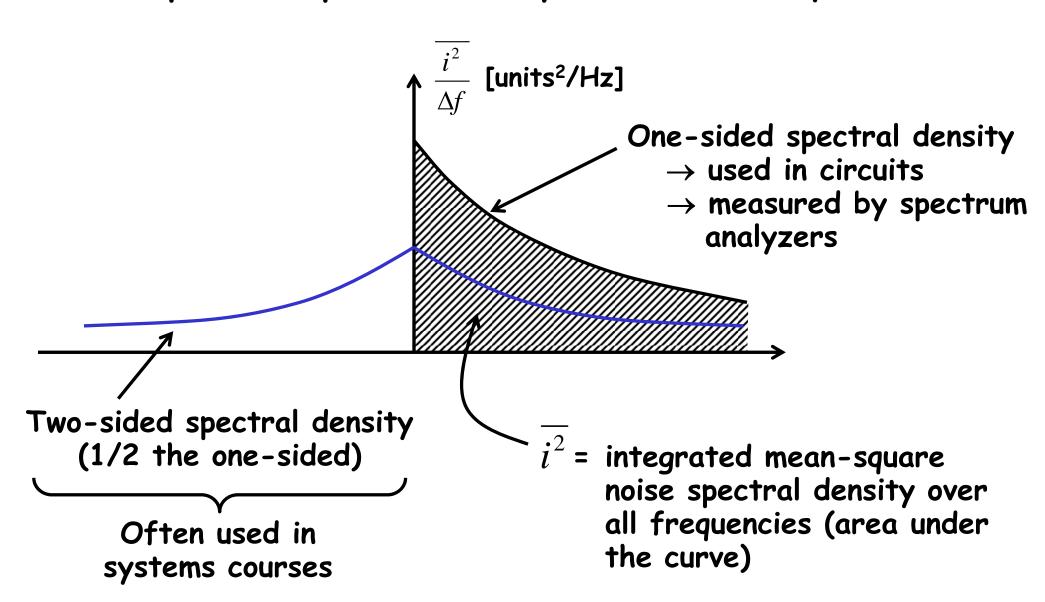

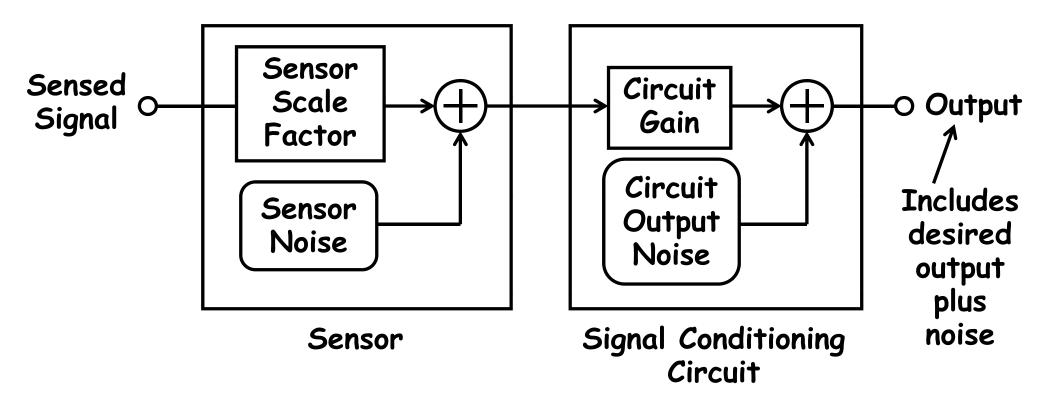

#### Noise Spectral Density

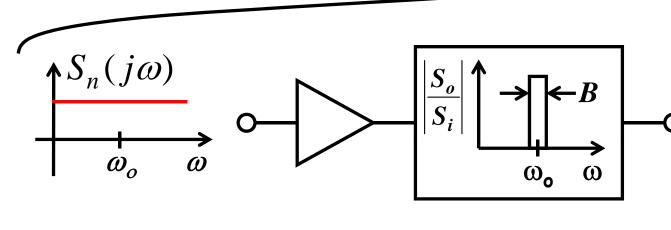

• We can plot the spectral density of this mean-square value:

#### Circuit Noise Calculations

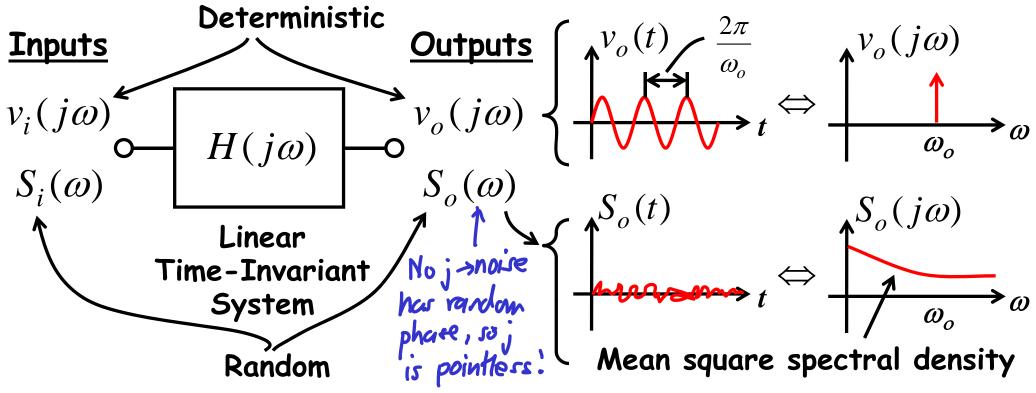

- Deterministic:  $v_o(j\omega) = H(j\omega)v_i(j\omega)$

- Random:  $S_o(\omega) = \left[H(j\omega)H^*(j\omega)\right]S_i(\omega) = \left|H(j\omega)\right|^2S_i(\omega)$   $\sqrt{S_o(\omega)} = \left|H(j\omega)\right|\sqrt{S_i(\omega)} \longrightarrow \text{How is it we can do this?}$  Root mean square amplitudes

### Handling Noise Deterministically

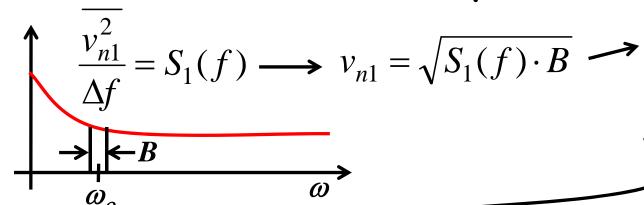

\* Can do this for noise in a tiny bandwidth (e.g., 1 Hz)

Can approximate this by a sinusoidal voltage generator (especially for small B, say 1 Hz)

[This is actually the principle by which oscillators work → oscillators are just noise going through a tiny bandwidth filter]

Why? Neither the amplitude nor the phase of a signal can change appreciably within a time period 1/B.

### Systematic Noise Calculation Procedure

General Circuit With Several Noise Sources  $\begin{array}{c|c} & H_2(j\omega) & H_5(j\omega) \\ \hline \hline v_{n2}^2 & \overline{v_{n3}^2} & \overline{v_{n5}^2} & \overline{v_{n6}^2} \\ \hline v_{n2}^2 & \overline{v_{n4}^2} & \overline{v_{n6}^2} & \overline{v_{n6}^2} \\ \hline & \overline{v_{n6}^2} & \overline{v_{n6}^2} & \overline{v_{n6}^2} \\ \hline \end{array}$

- Assume noise sources are uncorrelated

- 1. For  $i_{n1}^2$ , replace w/ a deterministic source of value

$$i_{n1} = \sqrt{\frac{\overline{i_{n1}^2}}{\Delta f}} \cdot (1 \text{ Hz})$$

### Systematic Noise Calculation Procedure

- 2. Calculate  $v_{on1}(\omega)=i_{n1}(\omega)H(j\omega)$  (treating it like a deterministic signal)

- 3. Determine  $v_{on1}^2 = i_{n1}^2 \cdot \left| H(j\omega) \right|^2$  \_\_\_\_\_\_

- 4. Repeat for each noise source:  $i_{n1}^2$ ,  $v_{n2}^2$ ,  $\overline{v_{n3}^2}$

- 5. Add noise power (mean square values)

$$\overline{v_{onTOT}^2} = \overline{v_{on1}^2} + \overline{v_{on2}^2} + \overline{v_{on3}^2} + \overline{v_{on4}^2} + \cdots$$

$$v_{onTOT} = \sqrt{\overline{v_{on1}^2 + \overline{v_{on2}^2 + \overline{v_{on3}^2 + \overline{v_{on4}^2 + \cdots}}}} + \cdots$$

Total rms value

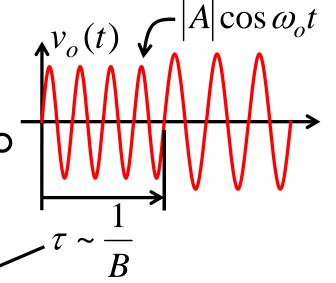

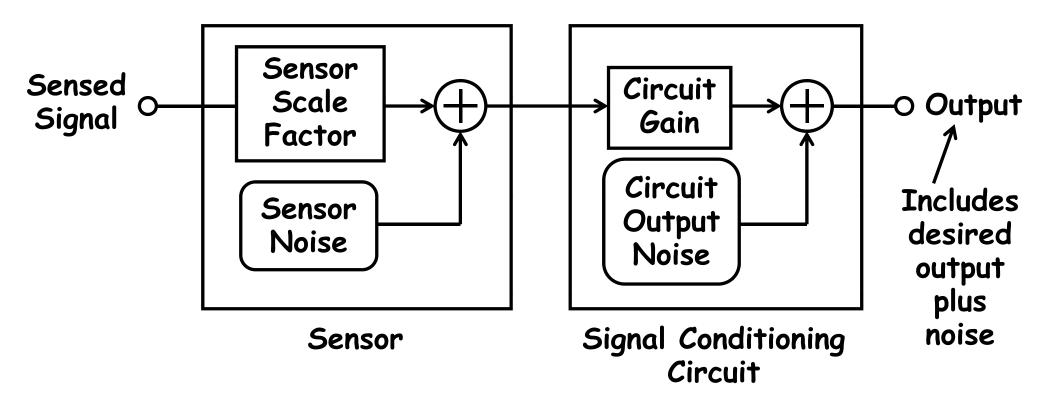

#### Minimum Detectable Signal (MDS)

Minimum Detectable Signal (MDS): Input signal level when the signal-to-noise ratio (SNR) is equal to unity

- \* The sensor scale factor is governed by the sensor type

- The effect of noise is best determined via analysis of the equivalent circuit for the system

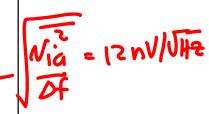

#### LF356 Op Amp Data Sheet

## LF155/LF156/LF256/LF257/LF355/LF356/LF357 JFET Input Operational Amplifiers

#### **General Description**

These are the first monolithic JFET input operational amplifiers to incorporate well matched, high voltage JFETs on the same chip with standard bipolar transistors (BI-FET™ Technology). These amplifiers feature low input bias and offset currents/low offset voltage and offset voltage drift, coupled with offset adjust which does not degrade drift or common-mode rejection. The devices are also designed for high slew rate, wide bandwidth, extremely fast settling time, low voltage and current noise and a low 1/f noise corner.

#### **Features**

#### Advantages

- Replace expensive hybrid and module FET op amps

- Rugged JFETs allow blow-out free handling compared with MOSFET input devices

- Excellent for low noise applications using either high or low source impedance—very low 1/f corner

- Offset adjust does not degrade drift or common-mode rejection as in most monolithic amplifiers

- New output stage allows use of large capacitive loads (5,000 pF) without stability problems

- Internal compensation and large differential input voltage capability

#### **Applications**

- Precision high speed integrators

- Fast D/A and A/D converters

- High impedance buffers

- Wideband, low noise, low drift amplifiers

- Logarithmic amplifiers

- Photocell amplifiers

- Sample and Hold circuits

#### **Common Features**

- Low input bias current: 30pA

- Low Input Offset Current: 3pA

- High input impedance: 10<sup>12</sup>O

- Low input noise current: 0.01 pA/√Hz

- High common-mode rejection ratio. 100 dB

- Large dc voltage gain: 106 dB

#### **Uncommon Features**

|                                       | LF155/<br>LF355 | LF156/<br>LF256/<br>LF356 | LF257/<br>LF357<br>(A <sub>V</sub> =5) | Units  |

|---------------------------------------|-----------------|---------------------------|----------------------------------------|--------|

| Extremely fast settling time to 0.01% | 4               | 1.5                       | 1.5                                    | μs     |

| ■ Fast slew rate                      | 5               | 12                        | 50                                     | V/µs   |

| ■ Wide gain<br>bandwidth              | 2.5             | 5                         | 20                                     | MHz    |

| ■ Low input                           | 20              | 12                        | 12                                     | nV/√Hz |

= 0.01 pA/VHZ

voltage

#### Minimum Detectable Signal (MDS)

Minimum Detectable Signal (MDS): Input signal level when the signal-to-noise ratio (SNR) is equal to unity

- \* The sensor scale factor is governed by the sensor type

- The effect of noise is best determined via analysis of the equivalent circuit for the system

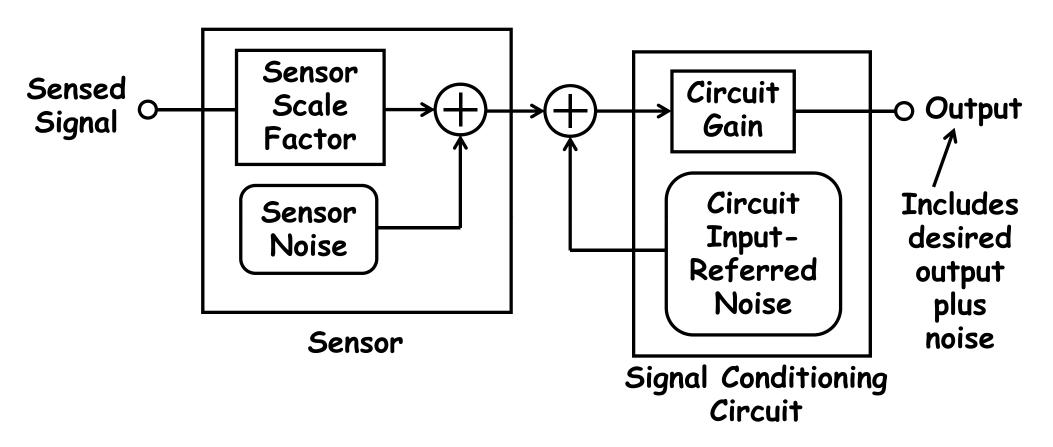

#### Move Noise Sources to a Common Point

UC Berkeley

- Move noise sources so that all sum at the input to the amplifier circuit (i.e., at the output of the sense element)

- \* Then, can compare the output of the sensed signal directly to the noise at this node to get the MDS

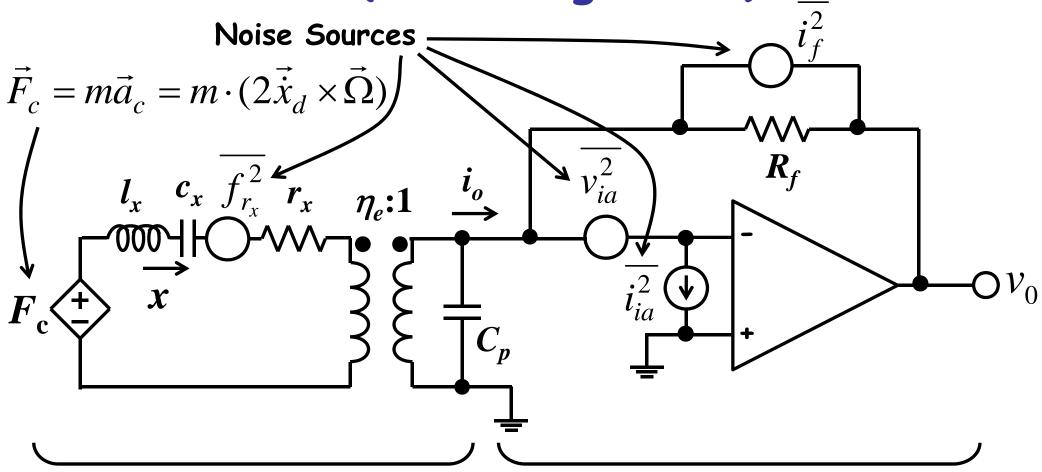

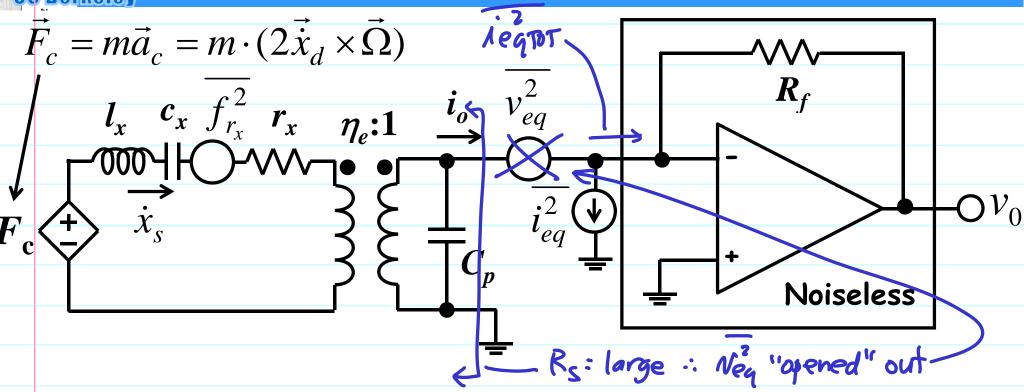

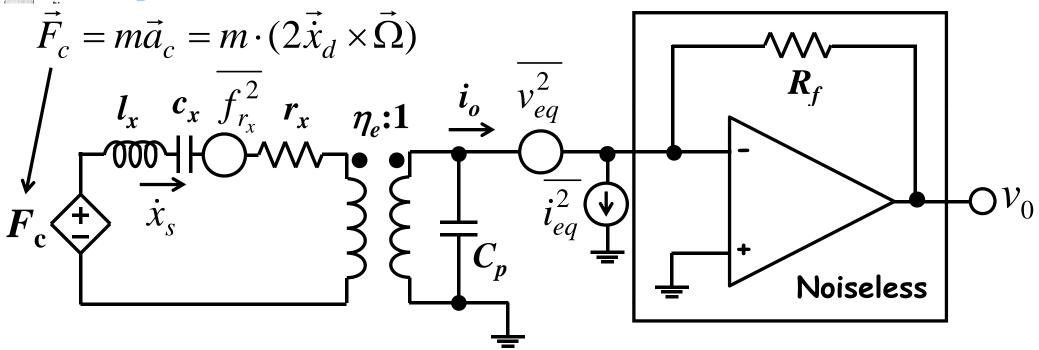

## Gyro Readout Equivalent Circuit ——(for a single tine)———

Gyro Sense Element

Output Circuit

Signal Conditioning Circuit (Transresistance Amplifier)

Easiest to analyze if all noise sources are summed at a common node

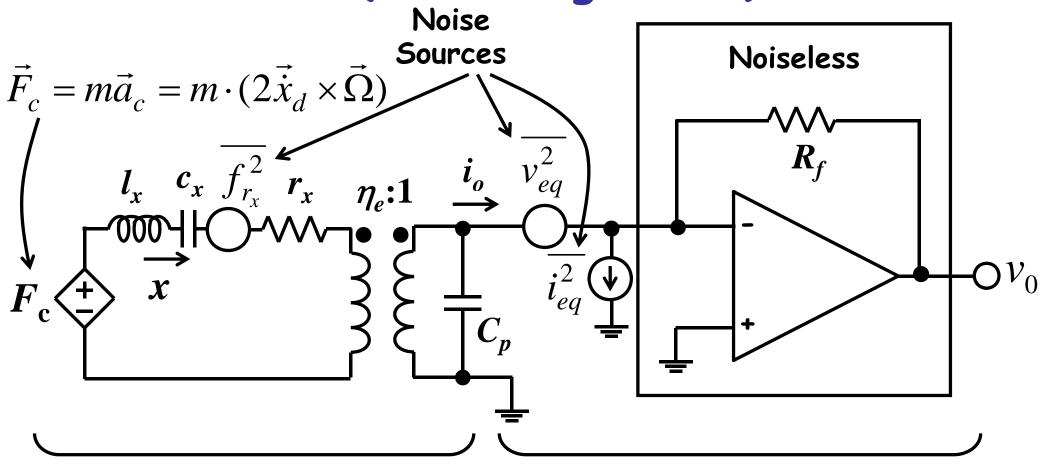

## Gyro Readout Equivalent Circuit (for a single tine)—

Gyro Sense Element

Output Circuit

Signal Conditioning Circuit (Transresistance Amplifier)

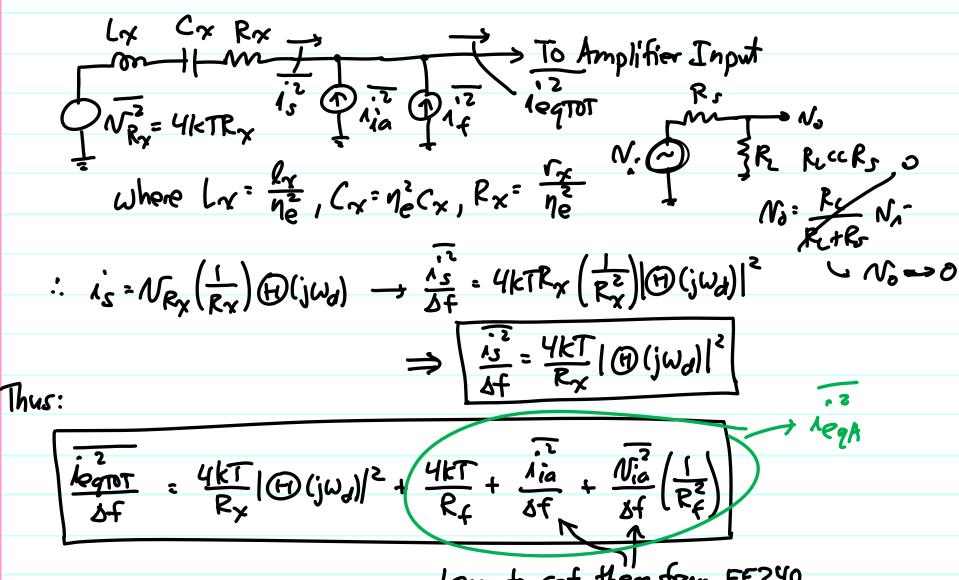

$^{\bullet}$  Here,  $v_{eq}^2$  and  $i_{eq}^2$  are equivalent input-referred voltage and current noise sources

\* Now, find the i<sub>eqTOT</sub> entering the amplifier input:

sense element  $\rightarrow$  defermined entirely by the noise in  $r_x \rightarrow f_{r_x}^2$  easiest to convert to an all electrical equiv. ckt.

UC Berkeley

Learn to get there from EE240.

or just get them from a data shoot ...

UC Berkeley

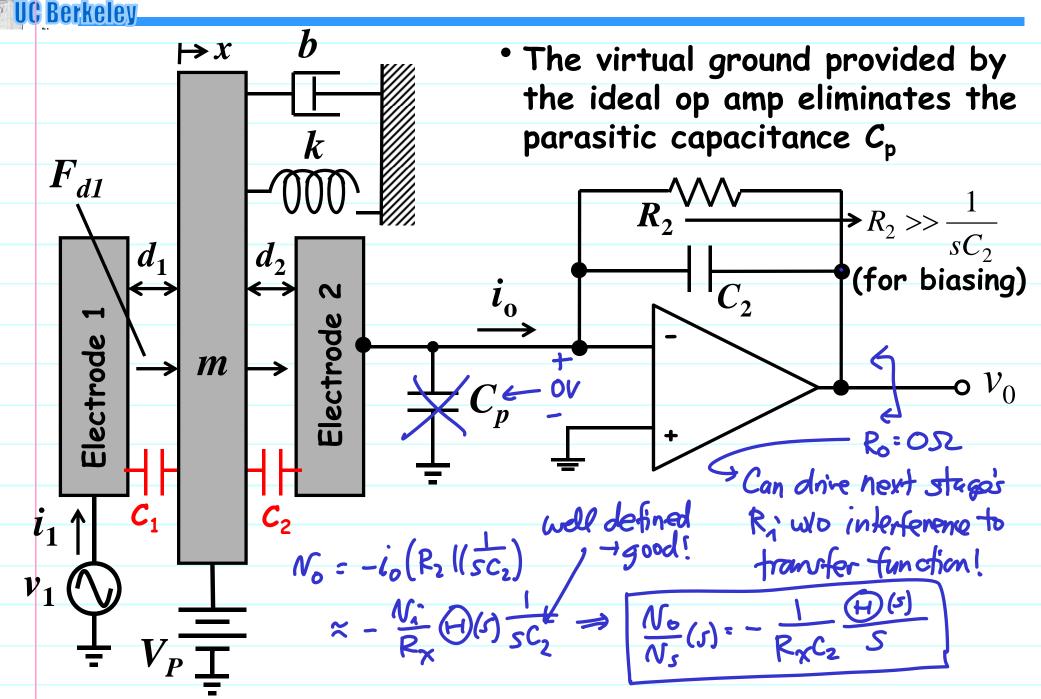

\* First, find the rotation to i<sub>o</sub> transfer function:

UC Berkeley

When  $\Omega$ :  $\Omega$  min = MOS, io: legtor—input-referred noise current embring the sense amplifier—in pA/VHZ

Easier to determine directional error as a function of elapsed time.

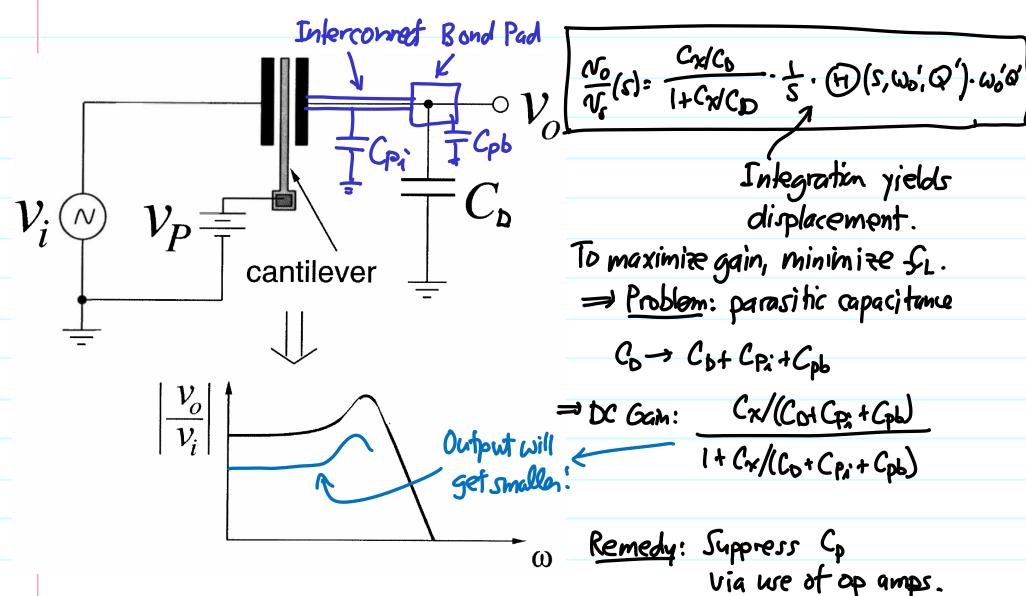

#### Sensing Circuits (cont)

UC Berkeley

To sense position (i.e., displacement), use a capacitive load

### The Op Amp Integrator Advantage

## Integration of MEMS and Transistors

EE C245: Introduction to MEMS Design Lecture 27 C. Nguyen 12/8/08

23

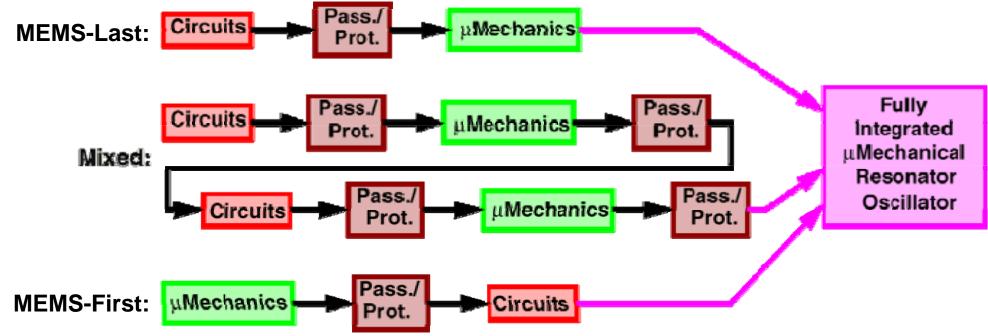

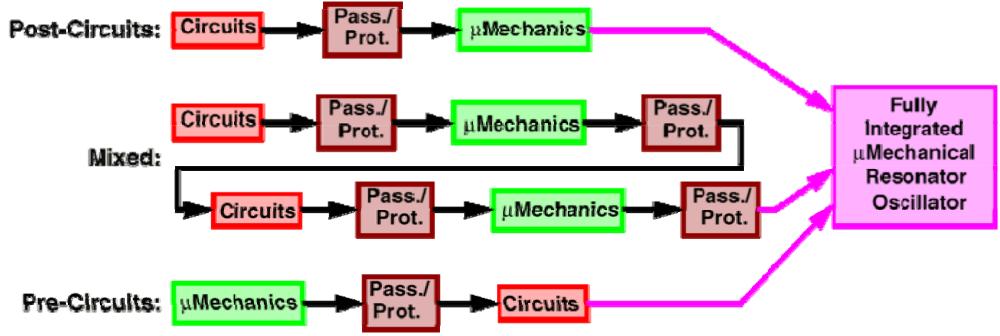

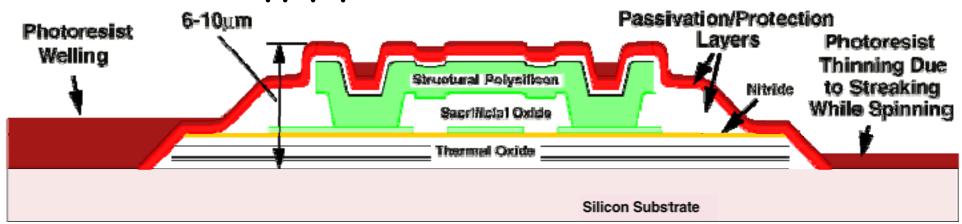

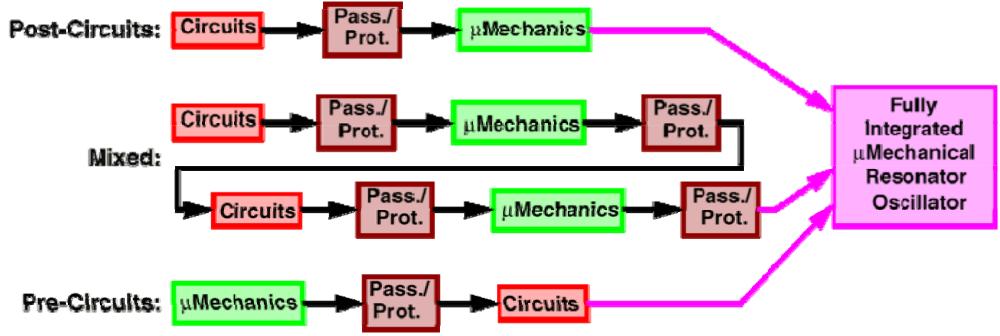

## Merged MEMS/Transistor UC Berkeley Technologies (Process Philosophy) —

- Mixed:

- $\Rightarrow$  <u>problem</u>: multiple passivation/protection steps  $\Rightarrow$  large number of masks required

- problem: custom process for each product

- MEMS-first or MEMS-last:

- $\Rightarrow$  adv.: modularity  $\Rightarrow$  flexibility  $\Rightarrow$  less development time

- $4 \times adv$ .: low pass./protection complexity  $\Rightarrow$  fewer masks

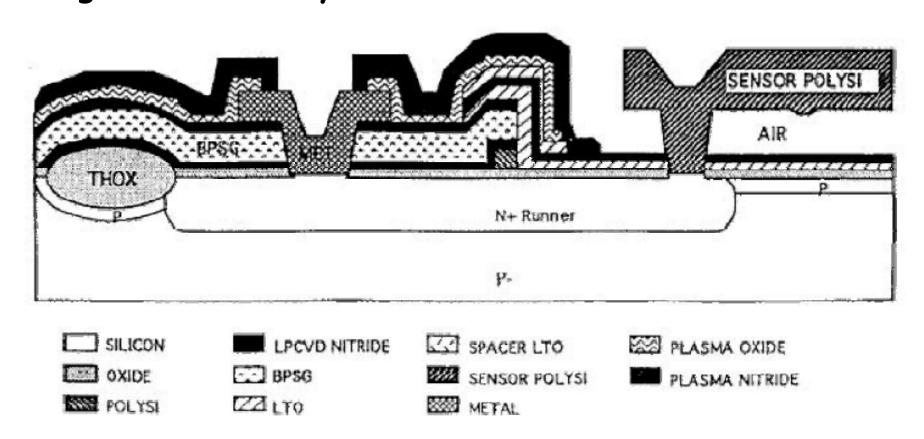

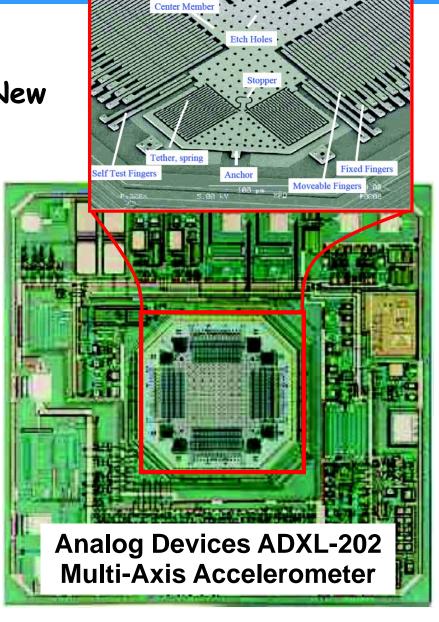

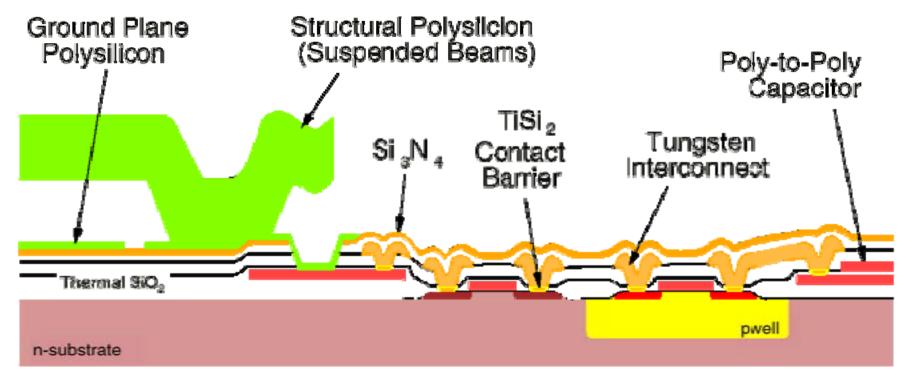

#### Analog Devices BiMEMS Process

- $^{\bullet}$  Interleaved MEMS and 4  $\mu$ m BiMOS processes (28 masks)

- Diffused n+ runners used to interconnect MEMS & CMOS

- \* Relatively deep junctions allow for MEMS poly stress anneal

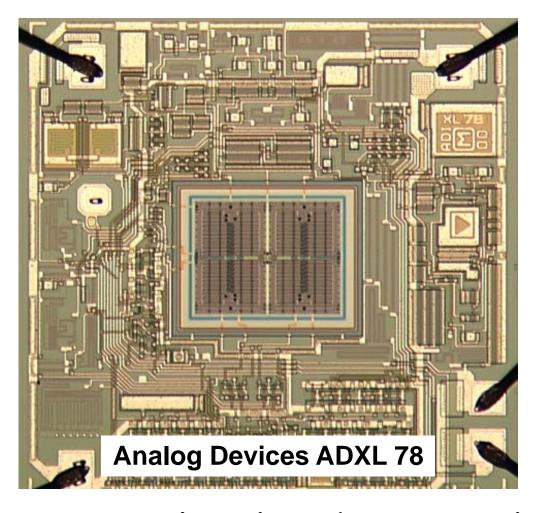

- Used to manufacture the ADXL-50 accelerometer and Analog Devices family of accelerometers

#### Analog Devices BiMEMS Process (cont)

• Examples:

C Berkeley

Old ------> New

• Can you list the advances in the process from old to new?

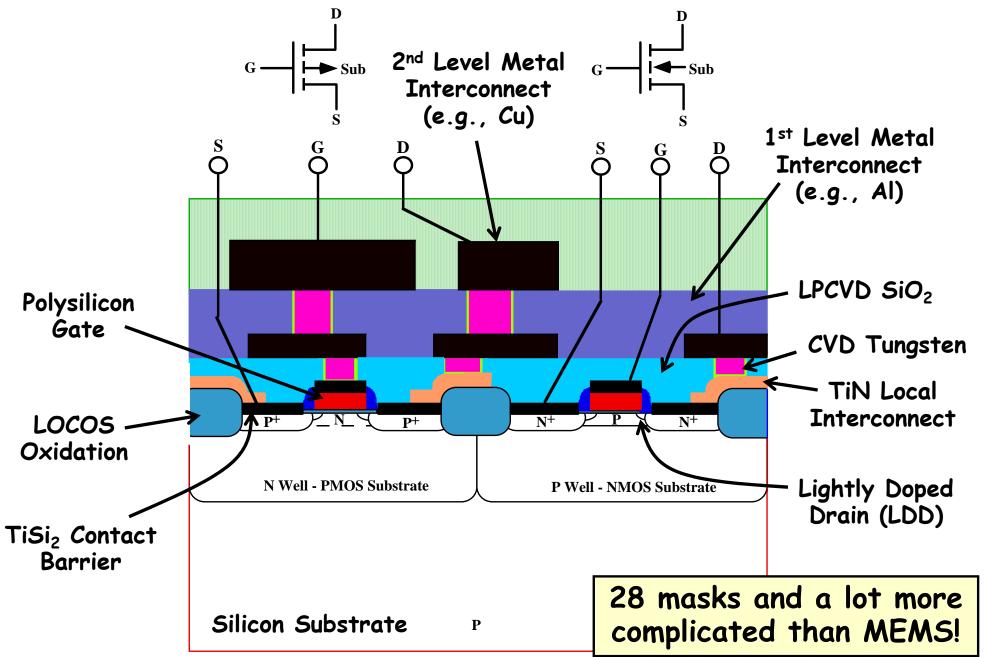

#### 250 nm CMOS Cross-Section

## Merged MEMS/Transistor UC Berkeley Technologies (Process Philosophy) —

#### • Mixed:

- problem: multiple passivation/protection steps ⇒ large number of masks required

- \$\frac{1}{2} \text{problem}: custom process for each product

- MEMS-first or MEMS-last:

- $\Rightarrow$  adv.: modularity  $\Rightarrow$  flexibility  $\Rightarrow$  less development time

- $4 \times adv$ .: low pass./protection complexity  $\Rightarrow$  fewer masks

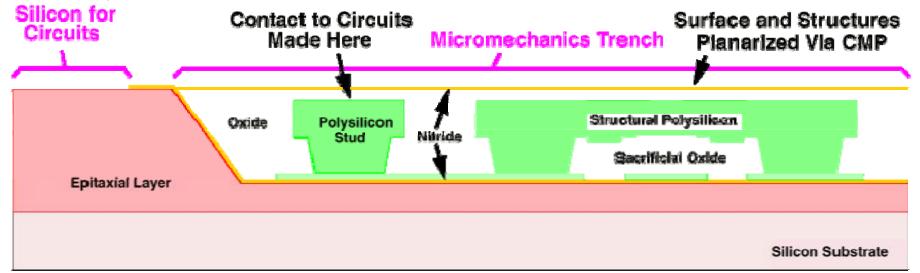

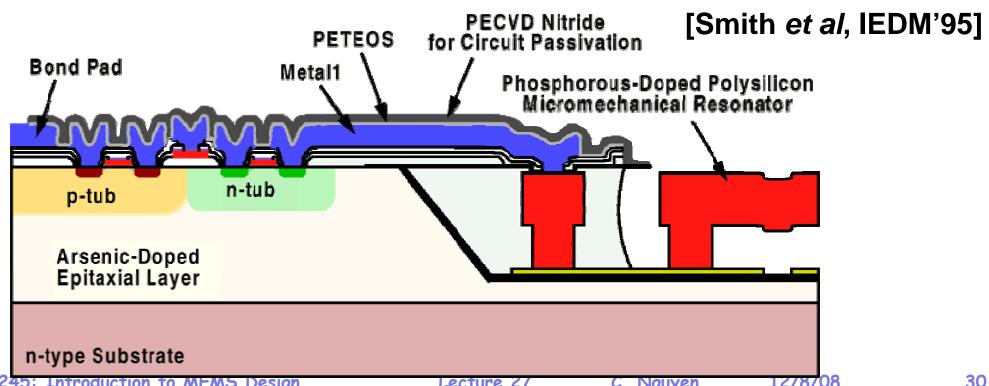

### MEMS-First Integration

\* <u>Soln</u>.: build μmechanics in a trench, then planarize before circuit processing [Smith *et al*, IEDM'95]

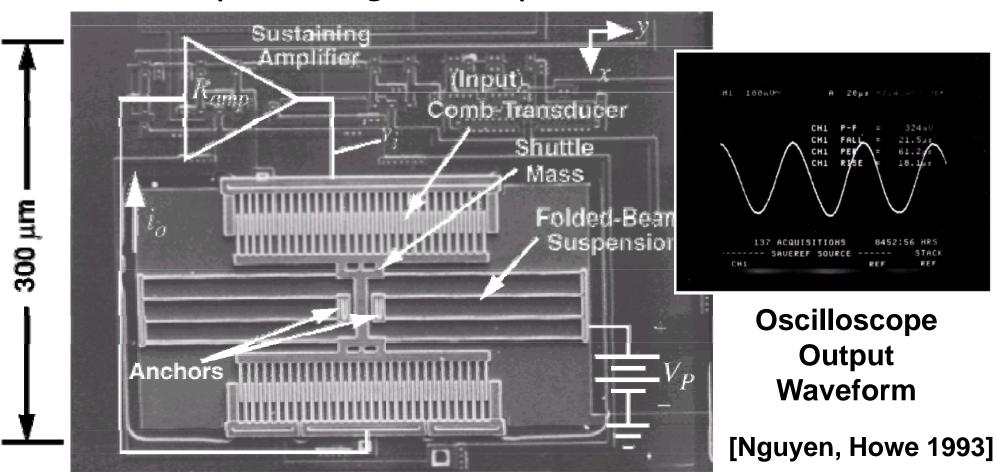

#### MEMS-First Ex: Sandia's iMEMS

- Used to demonstrate functional fully integrated oscillators

- Issues:

- $\diamondsuit$  lithography and etching may be difficult in trench  $\rightarrow$  may limit dimensions (not good for RF MEMS)

- $(>1000^{\circ}C) \rightarrow$  problem for some metal materials

- \$\times\ \text{might be contamination issues for foundry IC's}

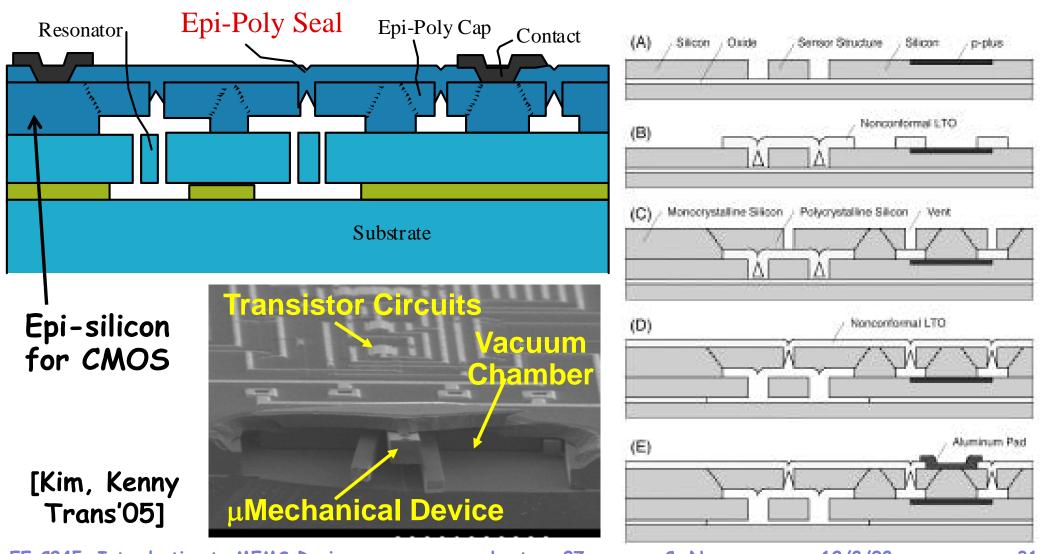

#### Bosch/Stanford MEMS-First Process

- UC Berkeley,

- Single-crystal silicon microstructures sealed under epi-poly encapsulation covers

- Many masking steps needed, but very stable structures

## Merged MEMS/Transistor UC Berkeley Technologies (Process Philosophy) -

#### • Mixed:

- $\$  problem: multiple passivation/protection steps  $\Rightarrow$  large number of masks required

- problem: custom process for each product

- MEMS-first or MEMS-last:

- $\Rightarrow$  adv.: modularity  $\Rightarrow$  flexibility  $\Rightarrow$  less development time

- $4 \times adv$ .: low pass./protection complexity  $\Rightarrow$  fewer masks

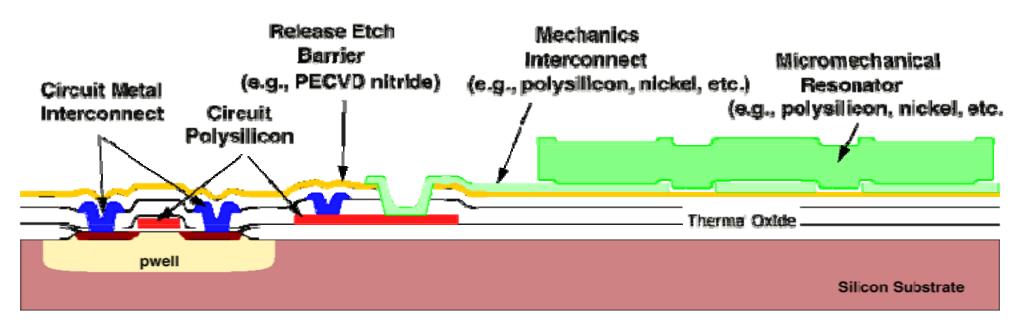

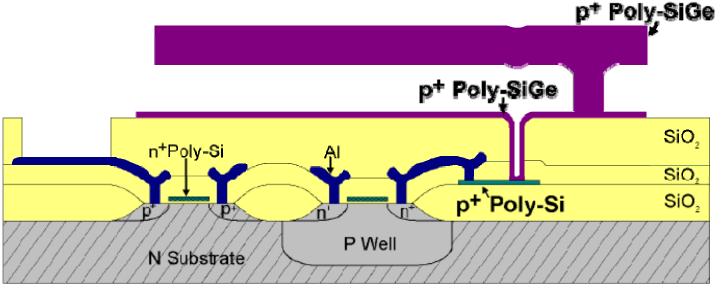

#### Berkeley Polysilicon MICS Process

- Uses surface-micromachinedpolysilicon microstructures with silicon nitride layer between transistors & MEMS

- \$\Polysilicon dep. T~600°C; nitride dep. T~835°C

- \$1100°C RTA stress anneal for 1 min.

- ♦ metal and junctions must withstand temperatures ~835°C

- \$\times\text{tungsten metallization used with TiSi2 contact barriers}

- \$\in situ doped structural polySi; rapid thermal annealing

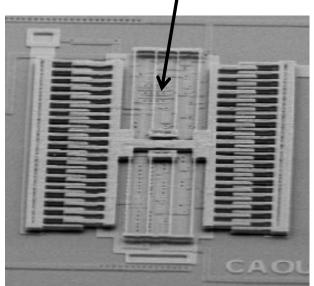

### Single-Chip Ckt/MEMS Integration

Completely monolithic, low phase noise, high-Q oscillator (effectively, an integrated crystal oscillator)

\* To allow the use of >600°C processing temperatures, tungsten (instead of aluminum) is used for metallization

#### Usable MEMS-Last Integration

- Problem: tungsten is not an accepted primary interconnect metal

- Challenge: retain conventional metallization

- minimize post-CMOS processing temperatures

- explore alternative structural materials (e.g., plated nickel, SiGe [Franke, Howe et al, MEMS'99])

- $\$  Limited set of usable structural materials  $\rightarrow$  not the best situation, but workable

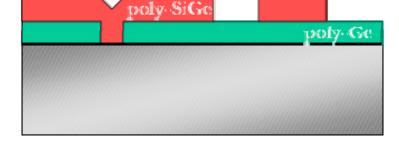

#### UCB Poly-SiGe MICS Process

\* 2 µm standard CMOS process w/ Al metallization

$^{\bullet}$  P-type poly-Si<sub>0.35</sub>Ge<sub>0.65</sub> structural material; poly-Ge

sacrificial material

#### • Process:

\$\to\$ Passivate CMOS w/ LTO @ 400°C

\$ Open vias to interconnect runners

♦ Deposit & pattern ground plane

\$RTA anneal to lower resistivity (550°C, 30s)

## Wrap Up