# EE C247B - ME C218 Introduction to MEMS Design Spring 2016

Prof. Clark T.-C. Nguyen

Dept. of Electrical Engineering & Computer Sciences

University of California at Berkeley

Berkeley, CA 94720

Module 16: Sensing Non-Idealities & Integration

EEC247B/MEC218: Introduction to MEMS Design

LecM 1

Lecture Outline

C. Nguyen

4/21/1

### @Rerkelev

- \* Reading: Senturia Chpt. 14, 15

- Lecture Topics:

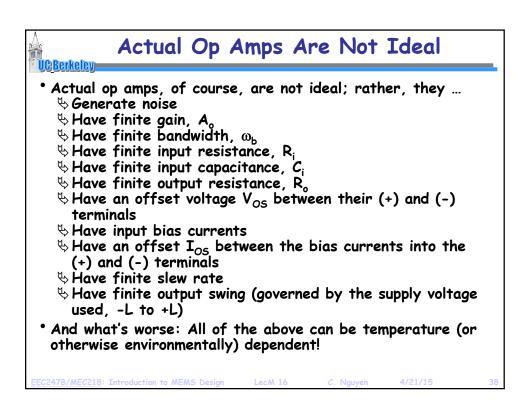

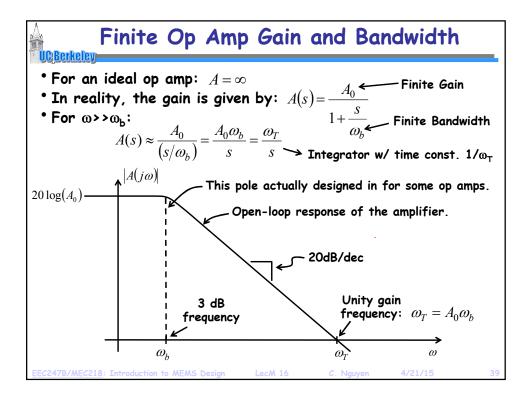

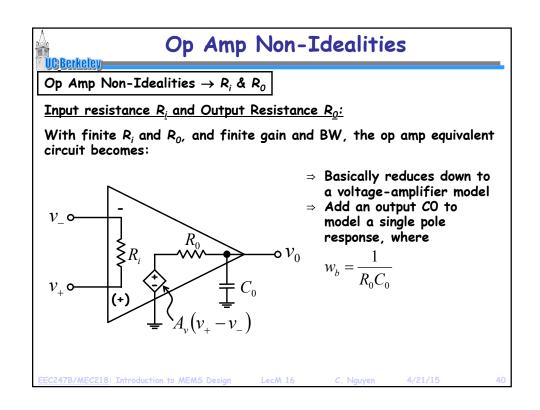

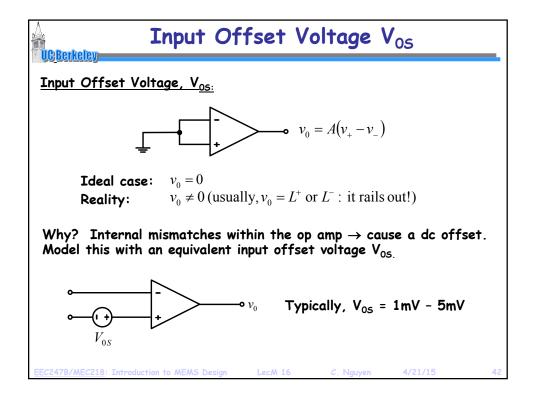

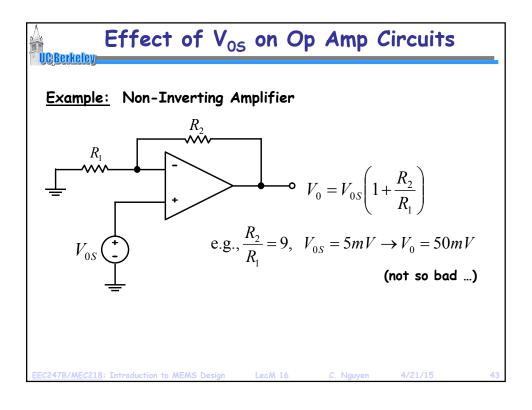

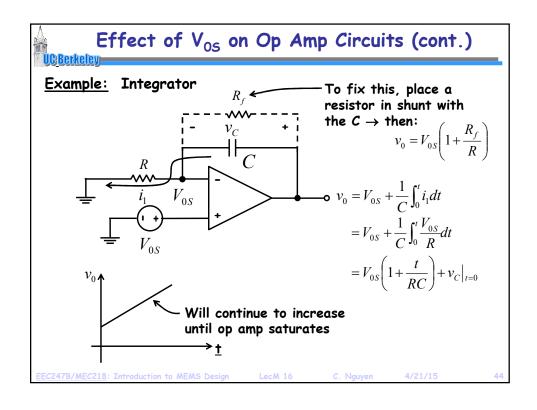

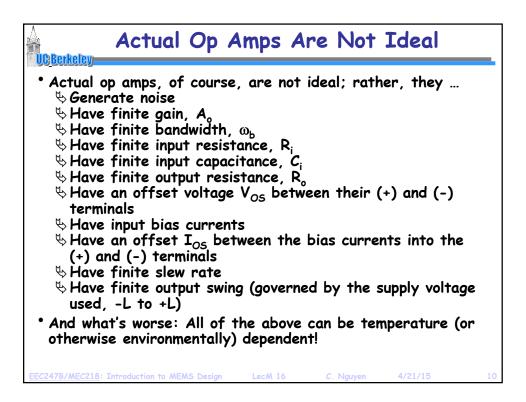

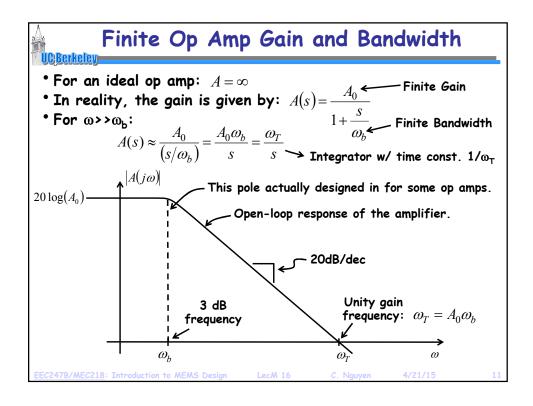

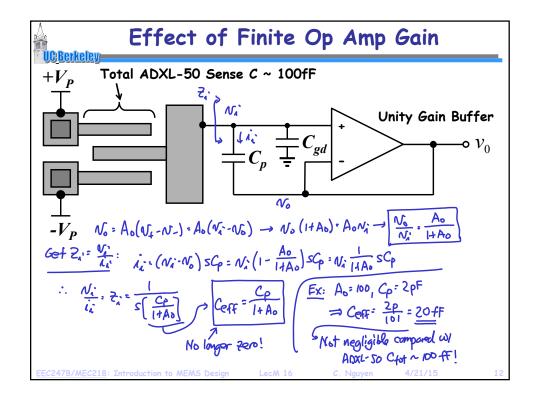

- ♦ Op Amp Non-Idealities

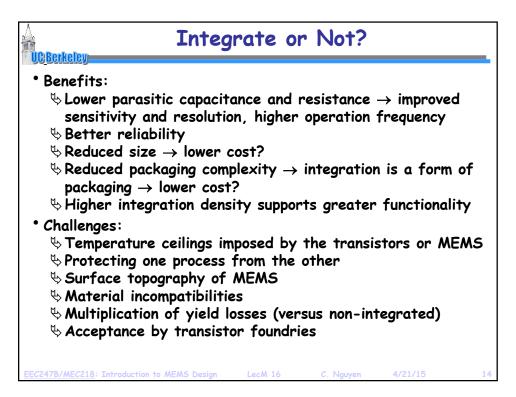

- MEMS-Transistor Integration

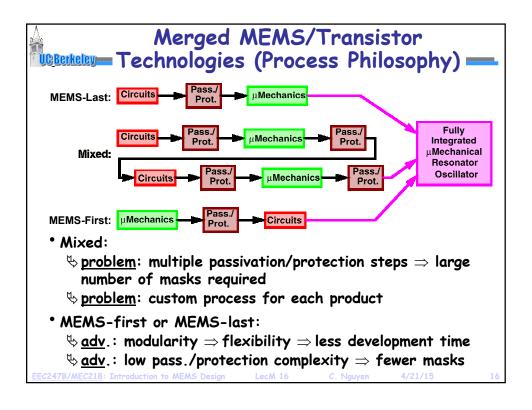

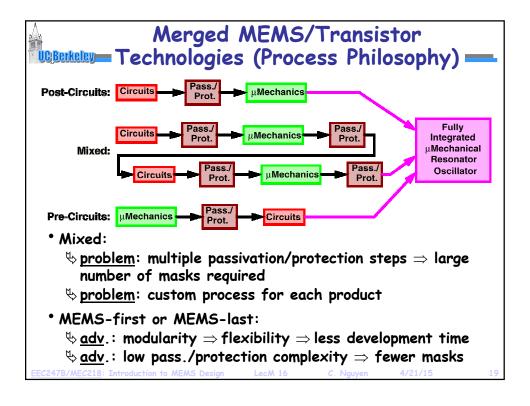

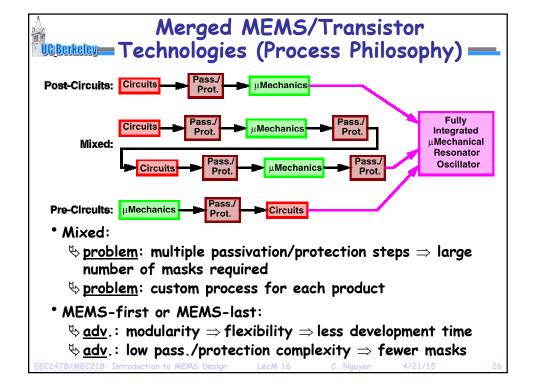

- ◆ Mixed

- ◆ MEMS-First

- ◆ MEMS-Last

- ♦ Op Amp Non-Idealities (cont.)

EC247B/MEC218: Introduction to MEMS Design

LecM 1

C. Nguyen

4/21/15

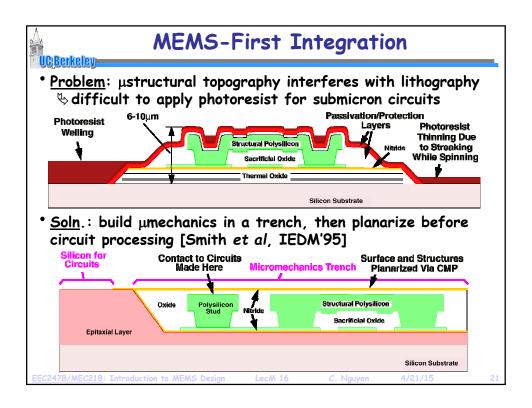

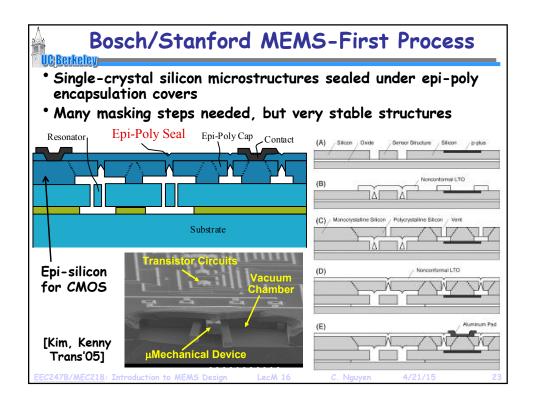

#### Problems With MEMS-First

- $^{ullet}$  Many masking steps needed, plus CMP required ightarrow cost can grow if you're not careful

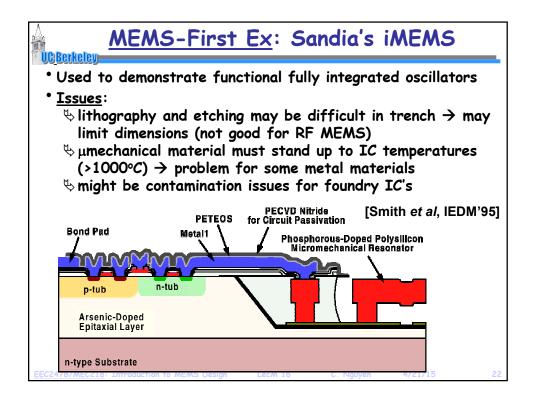

- Processes using trenches sacrifice lithographic resolution in microstructures

- MEMS must withstand transistor processing temperatures

Precludes the use of structural materials with low temperature regimts: metals, polymers, etc.

- Exotic MEMS (e.g., ZnO) that can contaminate transistors during their processing are not permissible

thus, not truly modular

- \* Foundry acceptance not guaranteed and might be rare

EEC2ATD MEC219: Tribraduction to MEMS Design | Load 14 C. Neuron | 4/21/15 | 22

## Foundry Acceptance of MEMS-First?

- Is a CMP'ed silicon surface sufficiently pure for fabrication of aggressively scaled transistors? How about if an oxide is grown over the CMP'ed surface and removed via a wet etch to yield a "pristine" surface?

- Is epi silicon grown as part of a sealing process sufficiently pure for fabrication of aggressively scaled transistors?

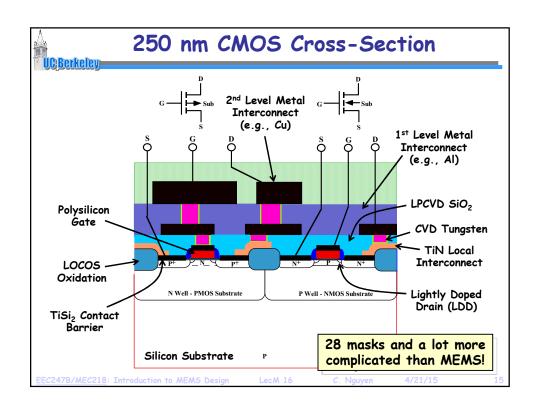

- \* CMOS is many times more difficult to run than MEMS

- \$ Feature sizes on the nm scale for billions of devices

- ♥ Contamination a big issue: many foundries may not accept pre-processed wafers for contamination reasons

- ♦ Many foundries will not accept any pre-processed wafers, MEMS or not → just can't guarantee working transistor circuits with unknowns in starting silicon

EEC247B/MEC218: Introduction to MEMS Design

.ecM 16

C. Nguye

4/21/1

25

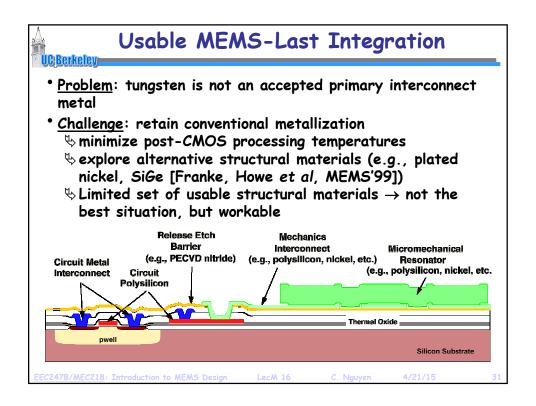

# MEMS-Last Integration

- Modular technology minimizes product updating effort

- ♦ Module 1: transistor process (planar IC technology)

- ♦ Module 2: micromachining process (planar technology)

- Adv.: foundry friendly

- $\heartsuit$  Virtually any foundry can be used  $\rightarrow$  can use the lowest cost transistor circuits (big advantage)

- <u>Adv</u>.: topography after circuit fabrication is quite small, especially given the use of CMP to planarize the metallization layers

- <u>Issue</u>: limited thermal budget limits the set of usable structural materials

- ♦ Metallization goes bad if temperature gets too high

- ♦ Aluminum grows hillocks and spikes junctions if T>500°C

- & Copper diffusion can be an issue at high temperature

- ♦ Low-k dielectrics used around metals may soon lower the temperature ceiling to only 320°C

EC247B/MEC218: Introduction to MEMS Design

.ecM 16

C. Nguyen

4/21/1

27

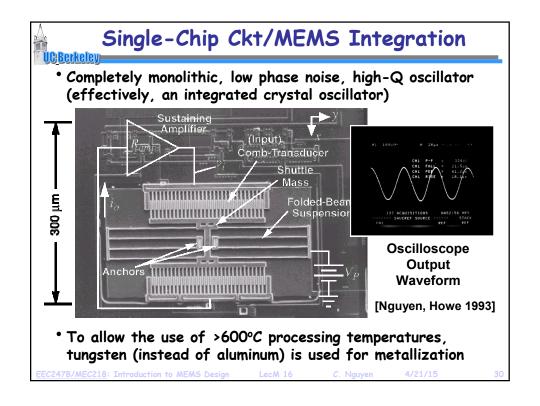

#### Berkeley Polysilicon MICS Process **UC Berkeley** Uses surface-micromachinedpolysilicon microstructures with silicon nitride layer between transistors & MEMS ♦ Polysilicon dep. T~600°C; nitride dep. T~835°C $\$ 1100°C RTA stress anneal for 1 min. ♥ metal and junctions must withstand temperatures ~835°C tungsten metallization used with TiSi2 contact barriers \$ in situ doped structural polySi; rapid thermal annealing Ground Plane Structural Polysilcion (Suspended Beams) Polysilicon Poly-to-Poly Capacitor TISI, Tungsten Si<sub>a</sub>N<sub>a</sub> Contact Interconnect Barrier Thermal SiQ. owell n-substrate