## PROBLEM SET #6

Issued: Tuesday, Oct. 30, 2012

Due (at 7 p.m.): Tuesday Nov. 20, 2012, in the EE C245 HW box near 125 Cory.

Figures PS6.1-6 show a dual-axis *x*-*y* accelerometer manufactured via the following 3-mask surface micromachining process:

- i) Deposit  $1.0 \,\mu m$  of SiO<sub>2</sub> on a Silicon wafer

- ii) Deposit 300 nm of SiN<sub>3</sub> via LPCVD

- iii) Deposit 200 nm of in-situ doped polysilicon

- iv) Lithographically define and etch polysilicon interconnects (anisotropic)

- v) Deposit 2.0  $\mu$ m of SiO<sub>2</sub> (LTO)

- vi) Lithographically define and then etch anchor openings in SiO<sub>2</sub> (anisotropic)

- vii) Deposit 3.0 µm of in-situ doped polysilicon

- viii) Lithographically define and then etch the polysilicon structure (anisotropic)

- ix) Etch SiO<sub>2</sub> completely using an HF etch, releasing structure (isotropic)

Assume all materials are stress-free at room temperature and have the material properties listed in Table PS6.1.

Table PS6.1

| Material        | $ ho_m$ kg/m <sup>3</sup> | <i>E</i><br>GPa | ν    | $\alpha_T$ µstrain/K | $\sigma_0$ MPa | Comment        |

|-----------------|---------------------------|-----------------|------|----------------------|----------------|----------------|

| Polysilicon     | 2300                      | 150             | 0.2  | 2.8                  | Varies         | Random Grains  |

| Silicon Dioxide | 2200                      | 69              | 0.17 | 0.7                  | -300           | Amorphous      |

| Silicon Nitride | 3170                      | 270             | 0.27 | 2.3                  | 1100           | Stoichiometric |

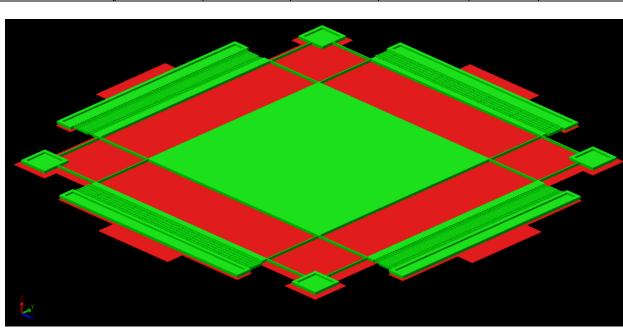

Figure PS6.1 – Perspective view of the accelerometer.

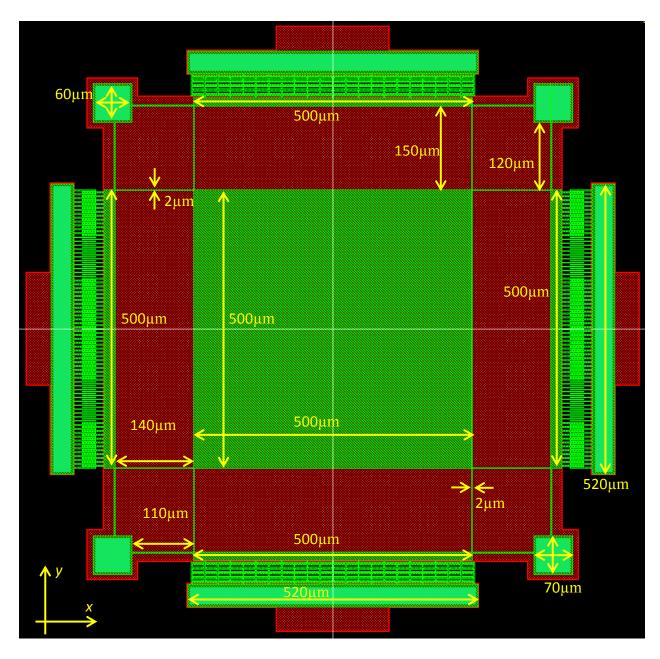

Figure PS6.2 – Top view of the accelerometer.

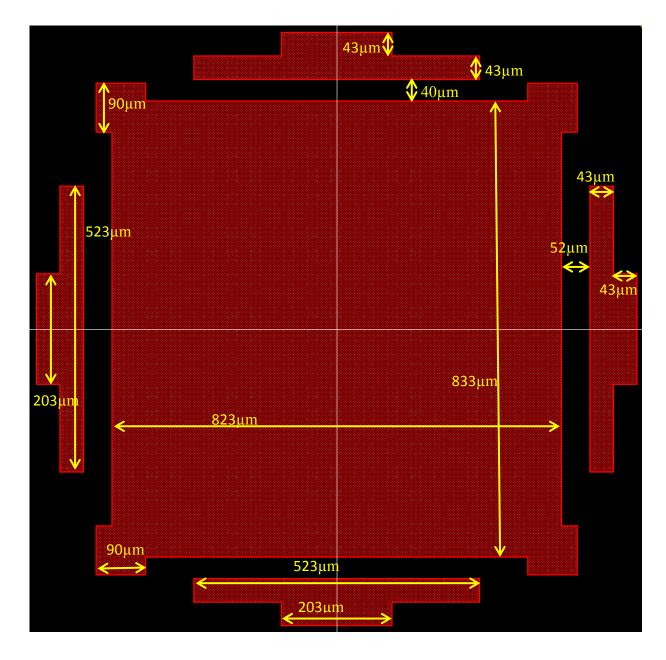

Figure PS6.3 – Top view of accelerometer showing only the interconnect layer.

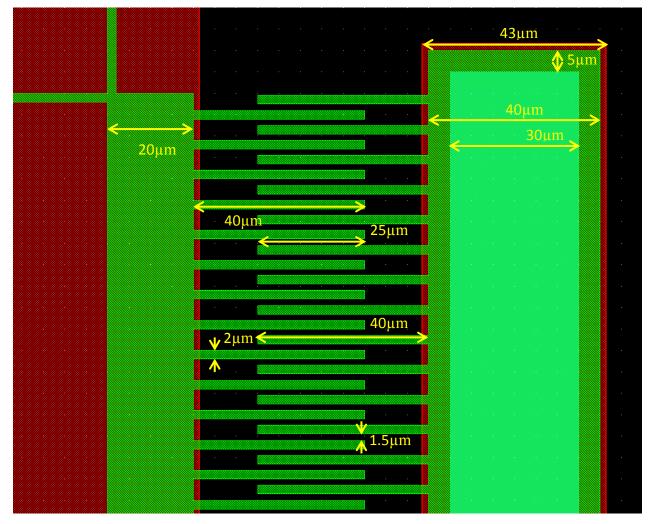

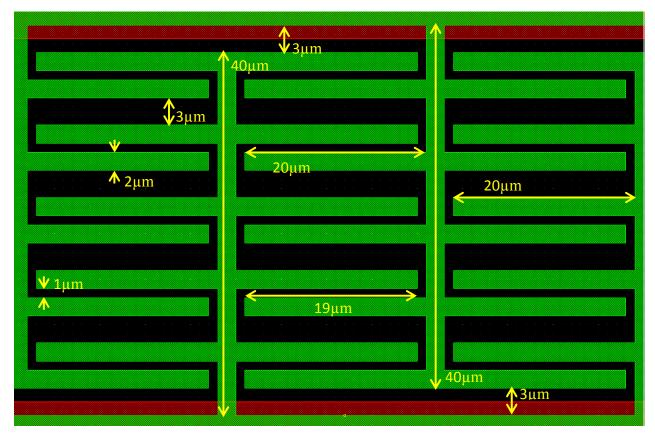

Figure PS6.4 – Zoom-in view of the *x*-direction interdigital comb finger structure. There are 71 fingers on each side of the proof mass.

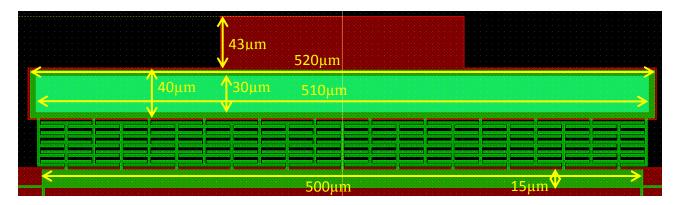

**Figure PS6.5** – Top view showing the *y*-direction capacitor structure.

Figure PS6.6 – Zoom-in view of the *y*-direction capacitor structure.

- 1. Calculate the *x* and *y*-directed resonance frequencies of the accelerometer structure with no applied DC bias, making simplifying assumptions as necessary. Do NOT neglect the beam masses in these calculations. Assuming a quality-factor Q of 5 in both directions, draw the frequency response for the accelerometer in both the *x* and *y*-directions.

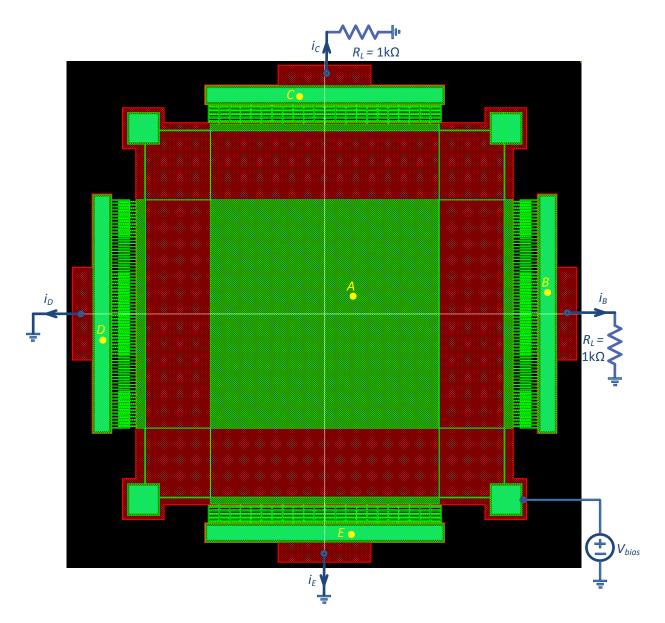

- 2. Derive an expression for the capacitance between port A and B shown in Figure PS6.7 as a function of displacement x using a parallel-plate approximation. Also, calculate the overlap capacitance between these two ports at rest.

- **3.** Derive an expression for the capacitance between port *A* and *C* shown in Figure PS6.7 as a function of displacement *y* using a parallel-plate approximation. Also calculate the overlap capacitance between these two ports at rest.

- 4. Suppose the accelerometer is now hooked up as shown in Figure PS6.7, with a DC bias  $V_{bias}$  of 10V applied to the structure.

- (a) Calculate the new x- and y-directed resonance frequencies with this DC bias.

- (b) If a sinusoidal force signal is applied to the structure in the *x*-direction with a magnitude of 1g, what will be the magnitude and phase of the resulting output current  $i_B$  as a function of frequency?

(c) If a sinusoidal force signal is applied to the structure in the *y*-direction with a magnitude of 1g, what will be the magnitude and phase of the resulting output current  $i_c$  as a function of frequency?

Figure PS6.7 – Top view of the accelerometer with circuit connections for problem 4.