# Accurate Statistical Process Variation Analysis for 0.25- $\mu$ m CMOS with Advanced TCAD Methodology

Hisako Sato, Hisaaki Kunitomo, Katsumi Tsuneno, Kazutaka Mori, and Hiroo Masuda, Senior Member, IEEE

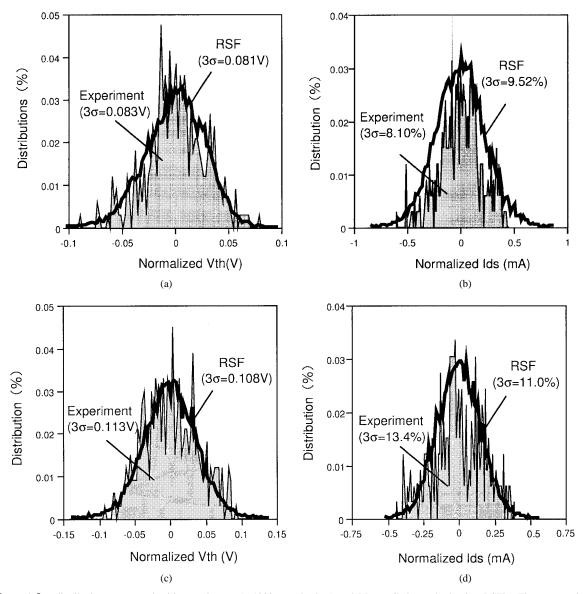

Abstract—Effects of statistical process variation on the 0.35- $\mu$ m CMOS performance have been accurately characterized by using a new calibrated TCAD methodology. To conduct the variation analysis, a series of TCAD simulations was conducted on the basis of DoE (design of experiments) with optimum variable transformations, which resulted in RSF's (response surface functions) for threshold voltage ( $V_{th}$ ) and saturation drain current ( $I_{ds}$ ). A new global calibration of the RSF model based on experimental data gives excellent accuracy within 0.02 V error in  $V_{th}$  and 3% error in  $I_{ds}$ . Using calibrated RSF, statistical process variation effects on the device characteristics have been quantitatively evaluated for each process recipe. It is found that variation of the gate-oxide formation process shows the most significant effect on the NMOS  $\Delta I_{ds}$  in the production process.

Furthermore we have designed an optimized 0.25- $\mu$ m CMOS process and device on the basis of the RSF and also predicted the process variation effects on the device performance. It is shown that the  $V_{th}$  and  $I_{ds}$  variations of the 0.25- $\mu$ m CMOS exhibit less than 10%  $I_{ds}$  variation in the production level process, which is similar to the value of 0.35- $\mu$ m CMOS experimental data. Additional TCAD simulations for MOS model parameter generation of the 0.25- $\mu$ m device was also conducted to allow circuit-designers to use predictive worst case circuit design parameters before experimental chip fabrication.

$\mathit{Index\ Terms}-$  Calibration, LSI, RSM, sensitivity analysis, TCAD.

# I. INTRODUCTION

**T**N SUB-0.5 and 0.25- $\mu$ m CMOS, statistical process variation control becomes one of the crucial issues to achieve high-performance CMOS MPU and memory. Device performance such as threshold voltage  $(V_{th})$  and saturation drain current  $(I_{ds})$  vary in various process steps sequence, which causes chip performance variation and determines its parametric yield. Therefore the circuit and chip designer needs to estimate the statistical variation of process and device characteristics through the terms of worst case and/or statistical (circuit) design parameters before actual mass-production phase. Especially in high-speed MPU and ASIC design, predictive accurate variation analysis is more important since clock-delay [1] and skew specifications become increasingly tighter in high clock cycle VLSI's. In this respect the precise estimation of process variation effects and practical worst case circuit design parameters are key design issues in 0.25- $\mu$ m CMOS LSI's before actual mass-production phase.

Manuscript received March 9, 1998; revised May 8, 1998.

H. Kunitomo is with Hitachi ULSI Systems Ltd., Tokyo 187-8522, Japan. Publisher Item Identifier S0894-6507(98)08369-9.

Recently TCAD has become one of the key approaches to predict device performance and to optimize process conditions for submicron CMOS development [2]-[4]. In this context, many works have been reported on statistical TCAD, whose approach is indispensable for worst case design of processes for scaled-down CMOS devices. The statistical technique, response surface methodology (RSM), [5], [6] is popular since it provides sensitivity data of the process factors to responses (threshold voltage and drain current) on the basis of systematic set of simulations. For the practical use of the simulationbased RSM, however, major drawbacks have to be overcome to give reliable predictions. The earlier works fail to describe the TCAD calibration methodology clearly [2]-[4]. TCAD design for process and device design seems to be unsuccessful because of difficulties in achieving the accuracy of simulation and experimental verification.

Therefore we have developed TCAD-based RSM design methodology to predict process sensitivity on the device performances [7]–[10]. To achieve a good fit to experimental data, a new global calibration and variable transformation technique have been developed, which allow the use of RSF in predictive accurate process and device design of scaled CMOS.

In this paper we will describe the accurate sensitivity analysis of process variation effects on the 0.35- $\mu$ m CMOS products on the basis of mass-production data and the predictive 0.25- $\mu$ m CMOS process/device optimization design and its variation diagnosis on the basis of the new TCAD-based RSM. Furthermore we have determined worst case MOS model parameters which have been used in a MPU circuit and chip design in a predictive manner.

## II. PROPOSED TCAD CALIBRATION FRAMEWORK

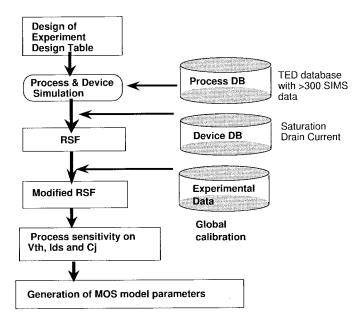

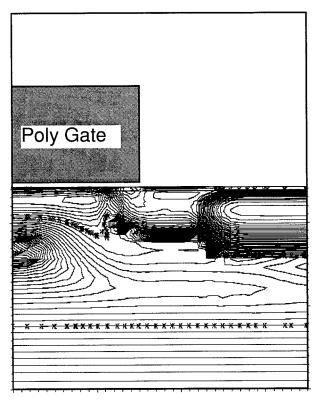

To achieve the sensitivity analysis of process variation effects on the 0.35- $\mu m$  NMOS  $I_{ds}$  distribution, we have developed a new TCAD-based methodology as shown in Fig. 1. As shown in this figure, physical models and their process parameters, e.g., implantation, diffusion, are first verified. TED (transient enhanced diffusion) parameters for low temperature impurity diffusion have especially been calibrated extensively on the basis of more than 300 SIMS (secondary ion mass spectroscopy) profile measurements, which are summarized in an in-house TED-database [8]. Fig. 2 demonstrates a simulated net-doping profile in two dimensions using the process simulator. In this figure, the equidoping contours marked with an asterisk show where the impurity concentration is  $10^{17}$

H. Sato, K. Tsuneno, K. Mori, and H. Masuda are with the Device Development Center, Hitachi, Ltd., Tokyo 198-8512, Japan (e-mail: hsato@ddc.hitachi.co.jp).

Fig. 1. Proposed TCAD flow. The hatched boxes show the new TCAD methodology.

Fig. 2. Simulated net-doping profile in two dimensions. In the figure, the equidoping contour marked with an asterisk shows where the impurity concentration is  $10^{17}$  cm-3.

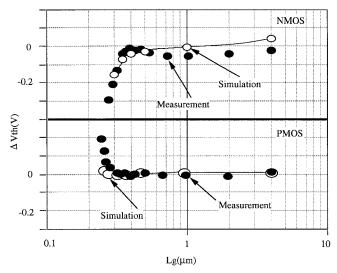

cm<sup>-3</sup>. With careful calibration of the impurity profile, the 0.35- $\mu$ m device threshold voltage  $(V_{th})$  was simulated using two-dimensional (2-D) process and device simulators. The results were verified with corresponding typical experimental data as shown in Fig. 3. It is shown that both results agree with each other within an error of <0.02 V for N and PMOS, including reverse-short-channel effect on  $V_{th}-L_g$

Fig. 3. Comparison of threshold voltage  $(V_{th})$  on gate length  $(L_g)$  between the experimental data and the results simulated with TED database at the typical process condition in NMOS and PMOS. Filled and open circles show experimental data and simulation results, respectively.

(gate length) curves. Thus the  $V_{th}-L_g$  curves based on TCAD with TED-database agree with the experimental data at the typical condition. However, it is necessary to predict the device characteristics not only at the typical condition but also at various process conditions in the actual device design. The calibrated physical models in the process simulator with a process database are inadequate for several respects such as 2-D diffusion in shallow junction formation. Therefore the RSM on the basis of systematic set of simulations is used because it provides sensitivity data of the process factors to responses (threshold voltage and drain current). To improve the accuracy of the prediction at the various process condition, the RSM with global calibration has been developed.

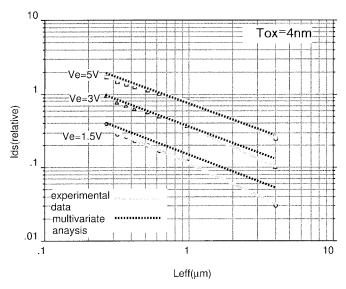

As for the drain currents, at first, we have also constructed the experimental saturation drain current database as shown in Fig. 1 [9]. The saturation experimental drain currents are fitted as the function of effective channel length ( $L_{\rm eff}$ ), effective gate voltage ( $V_e$ ), and gate oxide thickness ( $T_{ox}$ ) using about 150 data points by multivariate analysis. Fig. 4 shows an example of saturation drain current database in a NMOS. The figure shows the saturation drain current ( $I_{ds}$ ) dependence on the  $L_{\rm eff}$  and  $V_e$ . As shown in the figure, the drain currents are predicted by the regression function within an error of 10%. In order to improve the accuracy for  $I_{ds}$  prediction, the RSM for  $I_{ds}$  is also applied for 0.35- $\mu$ m CMOS device at various process conditions.

After the calibration of TCAD simulation models, process variation analysis and their effects on device characteristics are evaluated using the 0.35- $\mu$ m CMOS experimental results with a RSM. The RSM is employed to evaluate quantitative process sensitivity analyzes on  $I_{ds}$  and  $V_{th}$ . In RSM, each simulation point is assigned on the basis of DoE (design of experiment). After simulation, the quadratic equation, which is called the RSF (response surface function), is found by the least square

Fig. 4. Example of experimental saturation drain currents database. The experimental drain currents are fitted as a function of effective channel length ( $L_{\rm eff}$ ), effective gate voltage ( $V_e$ ) and gate oxide thickness ( $T_{ox}$ ). The solid and dotted lines show experimental data and the regression equation, respectively.

TABLE I

TRANSFORMATION FORMS OF PROCESS VARIABLES

WHICH REFLECT REVERSE SHORT CHANNEL EFFECT

| Parameter | Function zo: center point                             |

|-----------|-------------------------------------------------------|

| Implant 1 | $X=3.15 \frac{(z-zo)}{zo}$                            |

| Implant 2 | $X=3.75 \frac{(z-zo)}{zo}$                            |

| Implant 3 | $X=6\frac{(z-z_0)}{z_0}$                              |

| Lg        | $X=83.42Log\frac{Z}{ZO}+89.8(Exp\frac{(Z-ZO)}{ZO}-1)$ |

| Tox       | $X=12.5 \frac{(z-zo)}{zo}$                            |

TABLE II A WELL-KNOWN CCC (CIRCUMSCRIBED CENTRAL COMPOSITE) DESIGN TABLE IN FIVE PROCESS VARIABLES

|   |    | x1 | x2 | хЗ | х4 | x5   | Vth    | lds      |

|---|----|----|----|----|----|------|--------|----------|

|   | 1  | 1  | 1  | 1  | 1  | 1    |        |          |

|   | 2  | 1  | 1  | 1  | -1 | -1   |        |          |

|   | 3  | 1  | 1  | -1 | 1  | -1   |        |          |

|   | 4  | 1  | 1  | -1 | -1 | 1    |        |          |

|   | 5  | 1  | -1 | 1  | 1  | -1   | TCAD   |          |

|   | 6  | 1  | -1 | 1  | -1 | 1    | Simula | ation "" |

|   | 7  | 1  | -1 | -1 | 1  | 1    | Maid   | 2000     |

|   | 8  | 1  | -1 | -1 | -1 | -1   | Result | lS       |

| ~ |    |    |    |    |    |      |        |          |

|   | 25 | 0  | 0  | 0  | 0  | 1.5  |        |          |

|   | 26 | 0  | 0  | 0  | 0  | -1.5 |        |          |

|   | 27 | 0  | 0  | 0  | 0  | 0    |        |          |

method. The quadratic equation of the RSF used is given by

$$y = b_o + \sum_{i=1}^{n} b_i X_i + \sum_{i=1}^{n} \sum_{i \neq j}^{n} b_{ij} X_i X_j + \sum_{i=1}^{n} b_{ii} X_i^2.$$

(1)

Here  $X_i$ ,  $X_j$ , and y are the *i*th and *j*th process variables and the response, respectively. n is the number of variables.

#### TABLE III

BASIC IDEA OF THE GLOBAL EXPERIMENTAL CALIBRATION.  $b_o,\ b_i,\$ and  $b_{ij}$  Stand for the Coefficients of Simulation-Based RSF, Which are Derived from (1).  $b_o,\ b_i,\$ and  $b_{ij}$  Are Replaced by the Experimental Data

| Original RSF<br>on the basis of<br>simulation | Transformation of RSF with minimum experimental data |

|-----------------------------------------------|------------------------------------------------------|

| b (Simulation)                                | b (Experiment )                                      |

| b <sub>i</sub> (Simulation)                   | b (Experiment)                                       |

| b ij (Simulation)                             | b <sub>ij</sub> (Simulation) α α j                   |

|                                               | $\alpha_{i} = b_{i} (Experiment)/b_{i}(Simulation)$  |

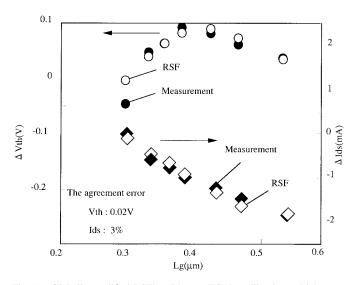

Fig. 5. Globally modified RSF's with new TCAD calibration, which prove to be in excellent agreement with experimental data of  $V_{th}-L_g$  and  $I_{ds}-L_g$  curves. Here the filled and open symbols show experimental data and results on the basis of RSF, respectively. The circle and square symbols show threshold voltage and saturation drain current, respectively. The threshold voltage agrees with the experimental data within 0.02 V error. The saturation drain current agrees with the experimental data within an error of 3%.

$b_o, b_i, b_{ij}$ , and  $b_{ii}$  denote constant, linear, cross, and quadratic coefficients of RSF, respectively. To perform the accurate statistical process variation analysis, five major process parameters (gate length, gate oxide thickness, and channel and source/drain implant doses) were selected, on the basis of their influence on the variations of threshold voltage and drain current. To obtain an accurate RSF, special care on the variable transformation and its range in DoE should be paid [7]. It is important to lineralize the variables for the responses. In Table I, we show transformation forms for five-process variables. They demonstrate a well-designed transformation of  $L_q$ , which is utilized to reflect reverse-short channel effect on the  $V_{th}$ . The  $L_g$  was transformed as the combination of logarithm and exponential functions mathematically to demonstrate the reverse short channel effect. Implant doses and gate oxide thickness were transformed by the linear functions because the  $V_{th}$  and  $I_{ds}$  depend linearly on these variables physically. Here  $X, z, z_o$  denote the transformed

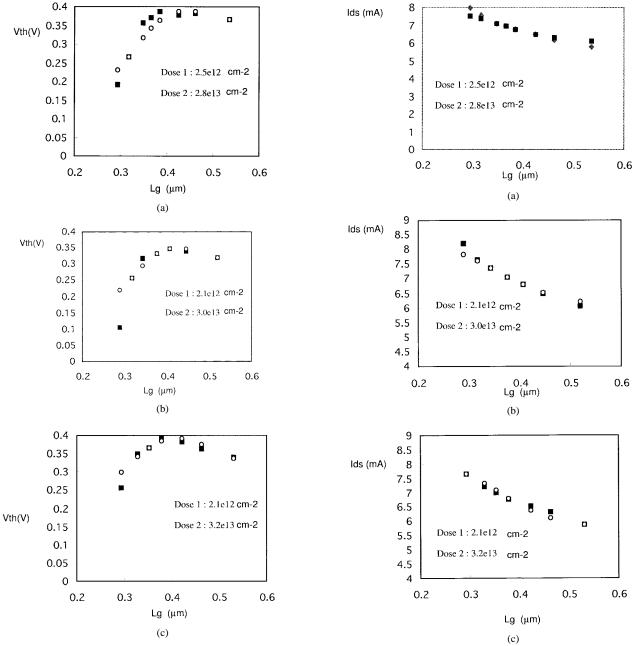

Fig. 6. Globally calibrated RSF achieved with TCAD and a new coefficients extraction procedure at the various process conditions for  $V_{th}-L_g$ . Filled and open symbols show the experimental data and RSF, respectively.

Fig. 7. Globally calibrated RSF achieved with TCAD and new coefficients extraction procedure at the various process conditions for  $I_{ds}-L_g$ . Filled and open symbols show the experimental data and RSF, respectively.

variable, actual value of the variable and the center value, respectively. The normalized values were calculated by the range of variables. The design table used in the series of TCAD simulations is shown in Table II, a well-known CCC (circumscribed central composite) table [11]. A set of variables and their ranges are combined considering the experimental data. For the five variables, twenty-seven simulations were performed according to the CCC design table.

Next step is an experimental global calibration after obtaining TCAD-based RSF for  $V_{th}$  and  $I_{ds}$  as parameters of  $L_g$ ,  $T_{ox}$ , and channel doping conditions. It is noted that this step is really important to get the reliable RSF which can be used in practical process/device RSF models. The experimental

calibration is performed after the formation of the simulation-based RSF using the minimal number of experimental data [7]. The basic idea of experimental calibration is shown in Table III. The constant and linear coefficients are replaced by experimental data and the quadratic and correlation coefficients are calculated using the equation as shown in Table III. This relation is derived on the basis of the assumption that the simulation-based RSF is correct in terms of relative relationship between the linear and quadratic terms. The coefficients of RSF on the basis of simulation were kept in case of unknown experimental data for the variables. Moreover these final coefficients are determined by the optimization method numerically. Fig. 5 shows resulting calibrated RSF's on the

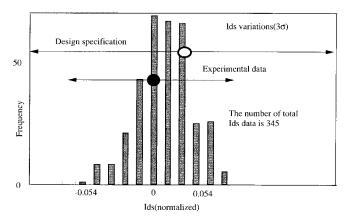

Fig. 8. Experimental saturation drain current ( $I_{ds}$ ) distributions of 0.35- $\mu$ m NMOS. The total number of data is 345. The original design specification disagrees with the experimental statistical data.

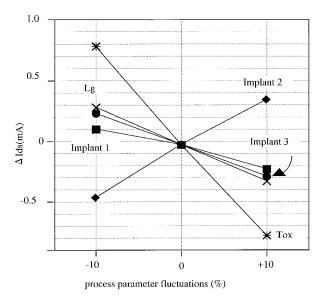

Fig. 9. Process sensitivity analysis on the  $I_{ds}$  variation using calibrated RSF. In this figure, each variable fluctuates  $\pm 10\%$  independently.

$V_{th}$  and  $I_{ds}$  at the typical process condition. The errors between the calibrated RSF's and experiments are 0.02 V for the  $V_{th}$  and 3% for the  $I_{ds}$  in RSM calculation. Figs. 6(a)–(c) and 7(a)–(c) compare  $V_{th}$  and  $I_{ds}$  between the calibrated RSF's and experimental data at the various combination of the implant doses, respectively. As shown in these figures, the calibrated RSF's agree with the experimental data to within 0.02 V for  $V_{th}$  and 3% for  $I_{ds}$  including the worst case doping conditions. Accordingly RSF's with global calibration can be predicted for  $V_{th}$  and  $I_{ds}$  within an error of 0.02 V and 3% at the various doping conditions, respectively, which agree excellently with fabricated experimental data not only under the typical but also worst case process conditions.

Finally the modified RSF is used to predict the device performance of the target device and to analyze the sensitivity of process parameters to the device performance. To obtain the accurate sensitivity of process variables, the PQC (process quality control) data in the mass-production are collected for the 0.35- $\mu$ m CMOS. Based on the sensitivity analysis, the

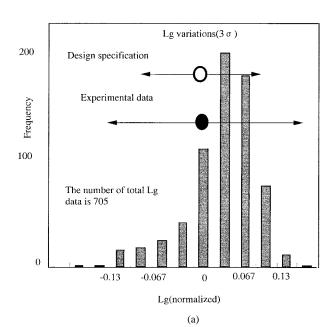

Fig. 10. (a) Actual experimental process variations of  $L_g$  (gate length). The total number of  $L_g$  data is 705. (b) Actual experimental process variations of  $T_{ox}$  (gate oxide thickness). The total number of  $T_{ox}$  data is 930.

MOS model parameters are extracted with additional TCAD simulations of worst case process conditions in 0.25- $\mu$ m CMOS.

#### III. PROCESS VARIATIONS ANALYSIS

Process variation analysis and their effects on device characteristics are evaluated using production-level 0.35- $\mu$ m CMOS experimental results and TCAD-based methodology which leads to an accurate process component sensitivity analysis on the device performance.

Experimental  $I_{ds}$  (normalized) distributions of 0.35- $\mu$ m NMOS is shown in Fig. 8. The experimental data used in the figure were collected during a couple of months of electric-test data. The total number of the  $I_{ds}$  data is 345. In the figure, the  $I_{ds}$  variations  $(3\sigma)$  for both design specification and experimental data are demonstrated, which make it clear

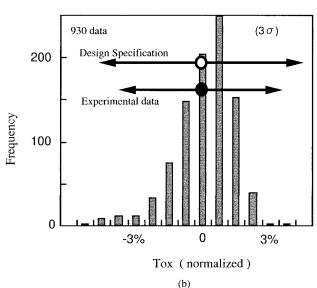

Fig. 11.  $V_{th}$  and  $I_{ds}$  distributions compared with experiments (>1000 sample data) and Monte Carlo method using RSF's. The gray region and solid lines show the experimental and RSF-Monte Carlo distribution, respectively. (a)  $V_{th}$  distribution in NMOS, (b)  $I_{ds}$  distribution in NMOS, (c)  $V_{th}$  distribution in PMOS, and (d)  $I_{ds}$  distribution in PMOS.

that the original estimation on  $\Delta I_{ds}$  does not reflect correctly the actual production level process variation. The original specification is too strict as compared to the actual production data. It is noted that the over specification of process variation effect results in difficulties in the worst case design of optimum high speed clock distribution network. Fig. 9 shows predicted process sensitivity analysis using calibrated RSF on the  $I_{ds}$  variation by assuming process parameter fluctuations of  $\pm 10\%$  independently. Note that the  $T_{ox}$  (gate oxide thickness) fluctuation affects  $I_{ds}$  variation much more than the  $L_g$  variation effect in the 0.35- $\mu$ m NMOS. To perform the accurate process component sensitivity analysis, it is necessary to investigate the actual process variation of not only  $L_g$  but also  $T_{ox}$ .

We investigated actual process variations of  $L_g$  CD (critical dimension) control,  $T_{ox}$  variation, and channel and source/drain implant doses, etc. The measured  $L_g$  variation using 705 points PQC data (>100 wafers) and measured  $T_{ox}$  variation using 930 points are shown in Fig. 10(a) and (b).

Compared to the  $L_g$  variation between experimental data and design specification, the experimental frequency shows a wide distribution. On the other hand, experimental variation of  $T_{ox}$  is almost the same as those of the design specification. As shown in these figures, the  $L_g$  and  $T_{ox}$  variations were determined  $\pm 13\%$  and  $\pm 3\%$ . In Fig. 11(a)–(d),  $V_{th}$  and  $I_{ds}$ distributions are compared between the experiments (>1000 samples) and Monte Carlo methods using RSF's in 0.35-μm N and PMOS. These process parameters, that is,  $T_{ox}$ ,  $L_q$ , and implant doses are changed to correspond to the actual process variations of  $\pm 3\%$ ,  $\pm 13\%$ , and  $\pm 3\%$ , respectively. In the Monte Carlo method, the correlation of each process parameter is calculated randomly. As shown in these figures,  $V_{th}$  and  $I_{ds}$  variations are 0.081 V, 9.52% for RSF's, and 0.083 V, 8.10% for experimental data in NMOS, respectively.  $V_{th}$  and  $I_{ds}$  variations are 0.108 V, 11.0% for RSF's, and 0.113 V, 13.4% for experimental data in PMOS, respectively. The variations for  $V_{th}$  and  $I_{ds}$  in PMOS are larger than those

TABLE IV PROCESS COMPONENTSENSITIVITY ANALYSIS ON THE DEVICE PERFORMANCE. EACH SENSITIVITY WAS CALCULATED BY THE CALIBRATED RSF'S EXCEPT  $W_G$  (GATE WIDTH). AN EMPIRICAL VALUE IS USED FOR SENSITIVITY OF  $W_G$

| Ids                                  | NMOS           |                | PMOS           |                |  |

|--------------------------------------|----------------|----------------|----------------|----------------|--|

| Process<br>Parameter                 | 0.35μm<br>CMOS | 0.25μm<br>CMOS | 0.35μm<br>CMOS | 0.25μm<br>CMOS |  |

| Lg                                   | ±3.4%          | ±6.7%          | ±5.6%          | ±7.0%          |  |

| Implant 1                            | ±0.6%          | ±0.7%          | ±1.0%          | ±1.8%          |  |

| Implant 2                            | ±1.5%          | $\pm 0.2\%$    | ±1.0%          | ±0.6%          |  |

| Implant 3                            | ±1.0%          | ±0.5%          | ±1.5%          | ±0.9%          |  |

| Tox                                  | ±6.4%          | ±6.7%          | ±3.8%          | ±3.2%          |  |

| Wg                                   | ±4.0%          | $\pm 0.3\%$    | ±4.0%          | ±0.3%          |  |

| Total<br>Sensitivity                 | ±8.3%          | ±9.5%          | ±8.1%          | ±7.9%          |  |

| Total<br>Sensitivity<br>(Experiment) | ±8.1%          |                | ±13.5%         |                |  |

of NMOS because the PMOS is a buried channel device. Both the  $V_{th}$  and  $I_{ds}$  variations (3 $\sigma$ ) of RSF Monte Carlo method agree with experimental data, which validate the proposed TCAD methodology.

### IV. VARIATION STUDY OF 0.25- $\mu$ m CMOS

To predict 0.25  $\mu$ m CMOS process sensitivity based on these actual process variation data, an accurate process component sensitivity analysis on the device performance  $(I_{ds})$ are conducted and shown in Table IV. Each sensitivity for each process parameter was calculated using the calibrated quadratic RSF's for 0.35- $\mu$ m CMOS independently while the other process parameters are set at the typical value. As shown in Fig. 10, these process parameters, that is,  $T_{ox}$  and  $L_g$  are changed to correspond to the actual process variations of  $\pm 3\%$ ,  $\pm 13\%$ , respectively. The fluctuation of implant doses was determined to be  $\pm 3\%$  by measurement of sheet resistance on wafer. An empirical value is used for the sensitivity for  $W_q$ (gate width). The total sensitivity is calculated as the square root of the summation of each sensitivity of the process parameter. It can be seen that experimental  $I_{ds}$  variation agrees well with the one calculated in 0.35- $\mu$ m CMOS. It is noted that the correlation of each process recipe is found to be quite small on the total  $\Delta I_{ds}$  in the NMOS process. On the contrary, Table IV and Fig. 11(d) indicate that the correlation of each process recipe is significant in PMOS because the total sensitivities were calculated  $\pm 8.1\%$  and  $\pm 11.0\%$  in the calculation and Monte Carlo method, respectively. The discrepancy between Monte Carlo method ( $\pm 11.0\%$ ) and experiment ( $\pm 13.5\%$ ) is assumed to occur from the structure effect. Further study will be needed to analyze error between calculation and experiment. The over specification is corrected by the accurate component analysis as shown in Fig. 6. In Table IV predicted variation analyzes are also given for a newly optimized 0.25 μm CMOS process/device with calibrated RSF. The variations

Fig. 12. Extracted worst case MOS model parameters determined on the basis of TCAD for 0.25- $\mu$ m CMOS: (a)  $V_{th}-L_g$  characteristics and (b)  $I_{ds}-L_g$  characteristics. In theses figures, the worst case condition is defined as the  $\pm$ 10% variation of gate oxide thickness  $(T_{ox})$ . The filled and open symbols show the typical and worst case conditions, respectively.

Lg (µm)

10

100

1.0

Tox +10%

-4 – 0.1

for process condition, e.g., implant doses, energies, and oxide thickness, are assumed to be the same as those for the 0.35- $\mu$ m CMOS process. We have also determined that the predicted optimum  $0.25~\mu$ m process shows process controllability as good as that of the 0.35- $\mu$ m process as shown in the table for both N and PMOS.

Worst case process conditions have been determined based on circuit types and chip performance estimation methodology. On the basis of Table IV, the variation for each process parameter is confirmed for the 0.35- $\mu$ m CMOS. Therefore the worst case definition was determined for 0.25  $\mu$ m CMOS, e.g.,  $\pm 10\%$  by  $T_{ox}$  was determined as the worst case condition. After that, additional TCAD simulations generate the current-voltage (I-V) curves (drain current versus drain voltage) for the worst cases and parameter extractions have been conducted using a compact MOS model. Examples of the generated MOS model parameters for the typical and worst

cases of  $\pm 10\%$  of  $T_{ox}$  are shown in Fig. 12(a) and (b), in terms of  $I_{ds}-L_g$  and  $V_{th}-L_g$  characteristics. Using these circuit parameters, the circuit designers are able to perform the predictive circuit design at the worst process conditions before experimental chip fabrications.

#### V. CONCLUSION

The new global calibration and variable transformation technique of the RSF on the basis of experimental data improve substantially the accuracy of the RSF model to within 0.02 V error in  $V_{th}$  and 3% error in  $I_{ds}$ . Using this method, we have designed an optimized 0.25  $\mu$ m CMOS process and device on the basis of the RSF and also predicted its process variation effect on the device performance. It is shown that the  $V_{th}$  and  $I_{ds}$  variations of 0.25  $\mu$ m CMOS exhibit less than 10% variation of  $I_{ds}$  in production level process by the calibrated TCAD methodology. Also additional TCAD simulations for MOS model parameter generation of 0.25  $\mu$ m device were conducted to allow circuit-designers to use predictive worst case circuit design parameters before experimental chip fabrication.

#### ACKNOWLEDGMENT

The authors would like to thank T. Takahashi and Y. Anata for providing experimental data.

#### REFERENCES

- K. Aoyama, K. Ise, H. Sato, K. Tsuneno, and H. Masuda, "A new characterization of sub-μm parallel multilevel interconnects and experimental verification," *IEEE Trans. Semiconduct. Manufact.*, vol. 9, pp. 20–26, Feb. 1996.

- [2] C. Pichler, R. Plasun, R. Strasser, and S. Selberherr, "Simulation environment for semiconductor technology analysis," in *Int. Conf Simulation Semiconductor Processes Devices, SISPAD'96*, 1996, p. 147.

- [3] T. Tatsumi, H. Ansai, K. Hayakawa, and M. Mukai, "BARAS: Novel and highly efficient simulation system for process control sweeping and statistical variation," in *Int. Conf Simulation Semiconductor Processes Devices, SISPAD'96*, 1996, p. 149.

- [4] K. Hasnat, S. Murtaza, and A. F. Tasch, "A manufacturing sensitivity analysis of 0.35 μm LDD MOSFET's," *IEEE Trans. Semiconduct. Manufact.*, vol. 7, pp. 53–59, Feb. 1994.

- [5] D. S. Boning and P. K. Mozumder, "DOE/OPT: A system for design of experiments, response surface modeling and optimization using process and device simulation," *IEEE Trans. Semiconduct. Manufact.*, vol. 7, p. 233, May 1994.

- [6] M. J. Van Dort and D. B. M. Klassen, "Sensitivity analysis of an industrial CMOS process using RSM techniques," Simul. Semicond. Devices Processes, vol. 6, p. 432, 1995.

- [7] H. Masuda, F. Otsuka, Y. Aoki, S. Sato, and S. Shimada, "Response surface methods for sub micron MOSFET's characterization with variable transformation technology," *IEICE Trans. Electron.*, vol. E-74, p. 1621, 1991.

- [8] H. Sato, K. Tsuneno, and H. Masuda, "Evaluation of two-dimensional transient enhanced diffusion of phosphorus during shallow junction formation," *IEICE Trans. Electron.*, vol. E77-C, no. 2, pp. 106–111, 1994

- [9] K. Tsuneno, H. Sato, and H. Masuda, "Modeling and simulation on degradation of submicron NMOSFET current drive due to velocitysaturation effects," *IEICE Trans. Electron.*, vol. E77-C, pp. 161–165, 1994.

- [10] H. Sato, K. Aoyama, K. Tsuneno, T. Nakamura, H. Kunitomo, and H. Masuda, "A new hierarchical RSM for TCAD-based device design in 0.4 μm CMOS development," *IEICE Trans. Electron.*, vol. E79-C, no. 2, pp. 226–233, 1996.

- [11] G. E. P. Box and N. R. Draper, Empirical Model-Building and Response Surfaces. New York: Wiley, 1987.

**Hisako Sato** was born in Ehime, Japan. She received the B.S. degree in applied chemistry from Waseda University, Tokyo, Japan, in 1981, the M.S. degree in chemistry from the University of Tokyo in 1983, and the Ph.D. degree in theoretical chemistry from Hokkaido University, Hokkaido, Japan, in 1992

In 1983, she joined the Device Development Center, Hitachi, Ltd., Tokyo, Japan. From 1983 to 1989, she researched the lithography process and simulation. Since 1989, she has been engaged in

the research of process model and TCAD simulation with statistical theory.

Dr. Sato is a member of the Japan Society of Applied Physics and Chemical Society of Japan.

**Hisaaki Kunitomo** was born in Osaka, Japan, in 1971. He received the B.S. degree in electrical engineering from Osaka Institute of Technology, Osaka, Japan, in 1993.

In 1993, he joined Hitachi Microcomputer System, Ltd., Tokyo, Japan. He has been working on the simulation and modeling of semiconductor devices at Hitachi ULSI Systems Ltd., Tokyo.

**Katsumi Tsuneno** was born in Chiba, Japan, in 1968. He received the B.S. degree in electronic engineering of science and technology from Nihon University, Chiba, in 1991.

He then joined the Device Development Center, Hitachi, Ltd., Tokyo, Japan. He has been working on the simulation and modeling of semiconductor devices.

**Kazutaka Mori** was born in Hiroshima, Japan, in 1958. He received the B.S. degree from the University of Tokyo. He spent a year as a graduate student at Princeton University, Princeton, NJ, from 1987 to 1988, and received the M.S.E.E. degree in 1988.

In 1980, he joined the Device Development Center, Hitachi Ltd., Tokyo, where he was engaged in circuit design and development of CMOS device for microprocessors. He is currently working on the development of submicrometer CMOS devices.

**Hiroo Masuda** (M'71–SM'90), for a photograph and biography, see this issue, p. 526.