#### **EE 40**

### **FINAL EXAM**

# December 13, 2002

# PLEASE WRITE YOUR NAME ON EACH ATTACHED PAGE PLEASE SHOW YOUR WORK TO RECEIVE PARTIAL CREDIT

| Problem 1: 10 Points Possible |                                                                       |

|-------------------------------|-----------------------------------------------------------------------|

| Problem 2: 10 Points Possible |                                                                       |

| Problem 3: 15 Points Possible |                                                                       |

| Problem 4: 15 Points Possible |                                                                       |

| Problem 5: 30 Points Possible |                                                                       |

| Problem 6: 30 Points Possible |                                                                       |

| Problem 7: 60 Points Possible |                                                                       |

| Part 7a: 30 Points Possible   | Complete 2 of these 3 parts of Problem 7, for a total of 60 points.   |

| Part 7b: 30 Points Possible   | If you complete all 3 parts, your 2 highest-scoring parts will count. |

| Part 7c: 30 Points Possible   |                                                                       |

| Problem 8: 30 Points Possible |                                                                       |

| Problem 9: 1 Point Possible   |                                                                       |

| TOTAL: 201 Points Possible    |                                                                       |

| Name                          | e: Solutions Page                                                                                                                                                                                                                                                                                 |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Probl                         | <u>em 1</u> : 10 Points Possible                                                                                                                                                                                                                                                                  |  |  |

| Match                         | each description below to a substance by writing the number next to the substance.                                                                                                                                                                                                                |  |  |

| Note:                         | Some substances have more than one matching description!                                                                                                                                                                                                                                          |  |  |

| 1.                            | Makes a good material for transistor gate because of its low resistance and ability to withstand high temperature anneals                                                                                                                                                                         |  |  |

| 2.                            | Deposited onto wafer by "sputtering"                                                                                                                                                                                                                                                              |  |  |

| 3.                            | 3. Implanted into wafer by high-energy ion impact and heated to a temperature > 800 °C                                                                                                                                                                                                            |  |  |

| 4.                            | "Grown" on wafer through thermal oxidation                                                                                                                                                                                                                                                        |  |  |

| <b>5</b> .                    | Medium which allows designer to pattern layers using a mask                                                                                                                                                                                                                                       |  |  |

| 6.                            | Protects materials from removal during "etching"                                                                                                                                                                                                                                                  |  |  |

| 7.                            | Serves as insulator between conducting layers                                                                                                                                                                                                                                                     |  |  |

| 8.                            | Deposited by shooting argon atoms at a target made of the deposit material, knocking loose atoms which fall on the wafer surface                                                                                                                                                                  |  |  |

| 9.                            | Parts which are exposed to light wash away in a developing liquid                                                                                                                                                                                                                                 |  |  |

| 10.                           | Deposition of this material causes damage to wafer, requiring "annealing" to repair                                                                                                                                                                                                               |  |  |

| Silicon Dioxide Dopants 3, 10 |                                                                                                                                                                                                                                                                                                   |  |  |

| Alumi                         | num $\frac{2,8}{}$ Photoresist $\frac{5,6,9}{}$                                                                                                                                                                                                                                                   |  |  |

| 8. 9. Silico                  | Deposited by shooting argon atoms at a target made of the deposit material, knocking loose atoms which fall on the wafer surface  Parts which are exposed to light wash away in a developing liquid  Deposition of this material causes damage to wafer, requiring "annealing" to repair  Dioxide |  |  |

Polysilicon

| Name: | <br> |

|-------|------|

|       |      |

#### Problem 2: 10 Points Possible

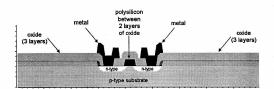

Consider the NMOS transistor with cross-section shown. Put the steps involved in the fabrication of this device in correct order.

| Pattern metal                | Step 1: Grow Oxide 500 nm   |

|------------------------------|-----------------------------|

| Grow oxide (20 nm thick)     | Step 2: Pattern Oxide       |

| Implant donors               | Step 3: Implant donors      |

| Deposit polysilicon          | Step 4: Grow Oxide 20 nm    |

| Grow oxide (500 nm thick)    | Step 5: Deposit polysilican |

| Deposit metal                | Step 6: Pattern polysilicon |

| Pattern polysilicon          | Step 7: Deposit oxide 750nm |

| Pattern oxide                | Step 8: Pattern oxide       |

| Deposit oxide (750 nm thick) | step 9: Deposit metal       |

| Pattern oxide                | Step 10: Pattern Metal      |

#### Problem 3: 15 Points Possible

Suppose we have connected the output of CMOS inverter 1 to the input of CMOS inverter 2, where the inverters have the following characteristics:

Both inverters:

$\mu_N = 500 \text{ cm}^2 / (Vs)$

$\mu_P = 250 \text{ cm}^2 / (\text{Vs})$

$V_{T(N)} = -V_{T(P)} = 1 V$

$t_{OX} = 10 \text{ nm (oxide thickness)}$

k<sub>ox</sub> = 4 (oxide dielectric constant)

$V_{DD} = 5 \text{ V}$

L<sub>i</sub> = 20 µm (interconnect length)

$W_l = 1 \mu m$  (interconnect width)

$\varepsilon_0 = 8.85 \times 10^{-12} \text{ F/m}$

Inverter 1:

$L_N = L_P = 2 \mu m$

$W_N = 6 \mu m$

$W_P = 24 \mu m$

$C_{DB(P)} = C_{DB(N)} = 50 \text{ fF}$

Inverter 2:

$L_N = L_P = 2 \mu m$

$W_N = 8 \mu m$

$W_P = 16 \, \mu m$

$C_{DB(P)} = C_{DB(N)} = 75 \text{ fF}$

Find the propagation delay for the output of inverter 1, when the input of inverter 1 changes from logic 0 to logic 1 instantaneously (after being logic 0 for a long time).

$$\begin{split} & t_{p} = 0.69 \, T \\ & T = R_{N} \left( C_{D3N_{1}} + C_{D8P_{1}} + C_{G3N_{2}} + C_{G3P_{2}} + C_{I} \right) \\ & R_{N} = 0.75 \, V_{DD} / I_{DSAT_{1}} = 0.75 V_{DD} / \left( \frac{\omega_{N_{1}}}{2 \, L_{N_{1}}} \mu_{n} C_{OX} (V_{SSN_{1}})^{2} \right) \\ & = 0.75 (5) / \left[ \left( \frac{6 \cdot 10^{-6}}{2 \cdot 2 \cdot 10^{-6}} \right) (500 \cdot 10^{-4}) \left( \frac{4 (8 \cdot 8 \cdot 10^{-12})}{10 \cdot 10^{-9}} \right) (5 - 1)^{2} \right] \\ & = 883 \, \mathcal{R} \\ & C_{G3N_{2}} = C_{OX} \, W_{N_{2}} L_{N_{2}} = \frac{4 (8 \cdot 8 \cdot 10^{-12})}{10 \cdot 10^{-9}} \left( 8 \cdot 10^{-6} \right) \left( 2 \cdot 10^{-6} \right) = 56 \, f \, F \\ & C_{G3P_{2}} = C_{OX} \, W_{P2} L_{P2} = \frac{4 (8 \cdot 8 \cdot 10^{-12})}{10 \cdot 10^{-9}} \left( 1 \cdot 10^{-6} \right) \left( 2 \cdot 10^{-6} \right) = 70 \, f \, F \\ & C_{I} = C_{OX} \, W_{I} \, L_{I} = \frac{4 (8 \cdot 8 \cdot 10^{-12})}{10 \cdot 10^{-9}} \left( 1 \cdot 10^{-6} \right) \left( 20 \cdot 10^{-6} \right) = 70 \, f \, F \end{split}$$

tp=0.69(883)(56+112+70+50+50)10

#### Problem 4: 15 Points Possible

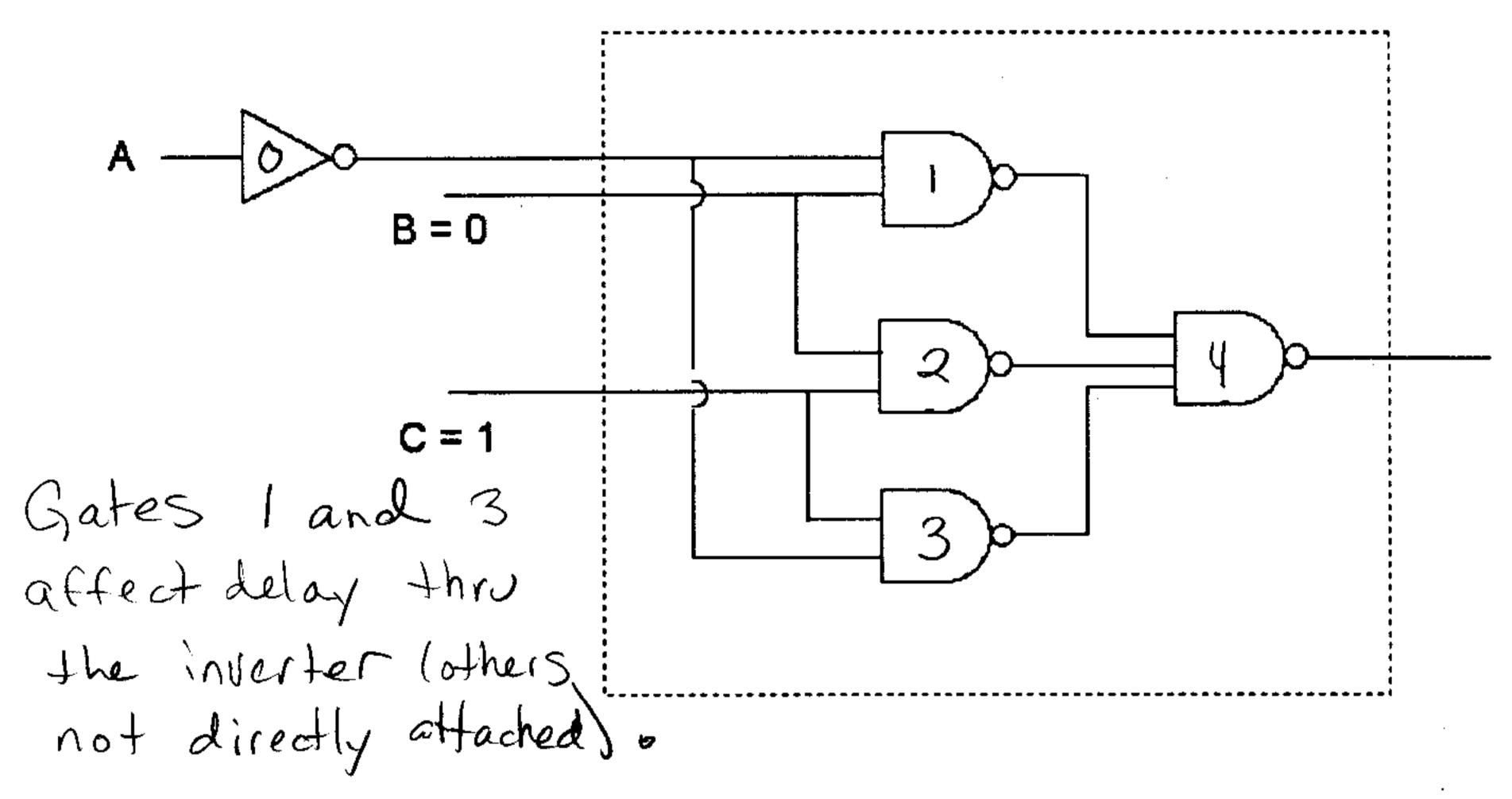

Suppose I hook an inverter up to one of the inputs of our 3-bit adder's most significant digit function. Find the propagation delay from the input to the output of the inverter when the inverter input A goes from low to high (with the other adder inputs held constant as shown).

For all of the gates, use

$C_{DB(P)} = C_{DB(N)} = 50 \text{ fF}$

$C_{GB(P)} = 50 \text{ fF}$

$C_{GB(N)} = 75 fF$

$C_1 = 100 fF per gate$

$R_N = 3 k\Omega$

$R_P = 2 k\Omega$

A NAND-NAND implementation of the circuit is shown below.

One connection to gate I and one connection to gate 3: Use 2 gate capacitances (CGBN and CGBD) forgate I and for gate 3. Use 2 CI (2 gates connected).

tp = 0.69 RN (CDBNO + CDBPO + CGBN, +CGBP, +CGBN3+CGBP3) = 0.69 (3000)(50 + 50 + 75 + 50 + 75 + 50 + 2.100)10-15

#### Problem 5: 30 Total Points Possible

a) 10 Points Possible

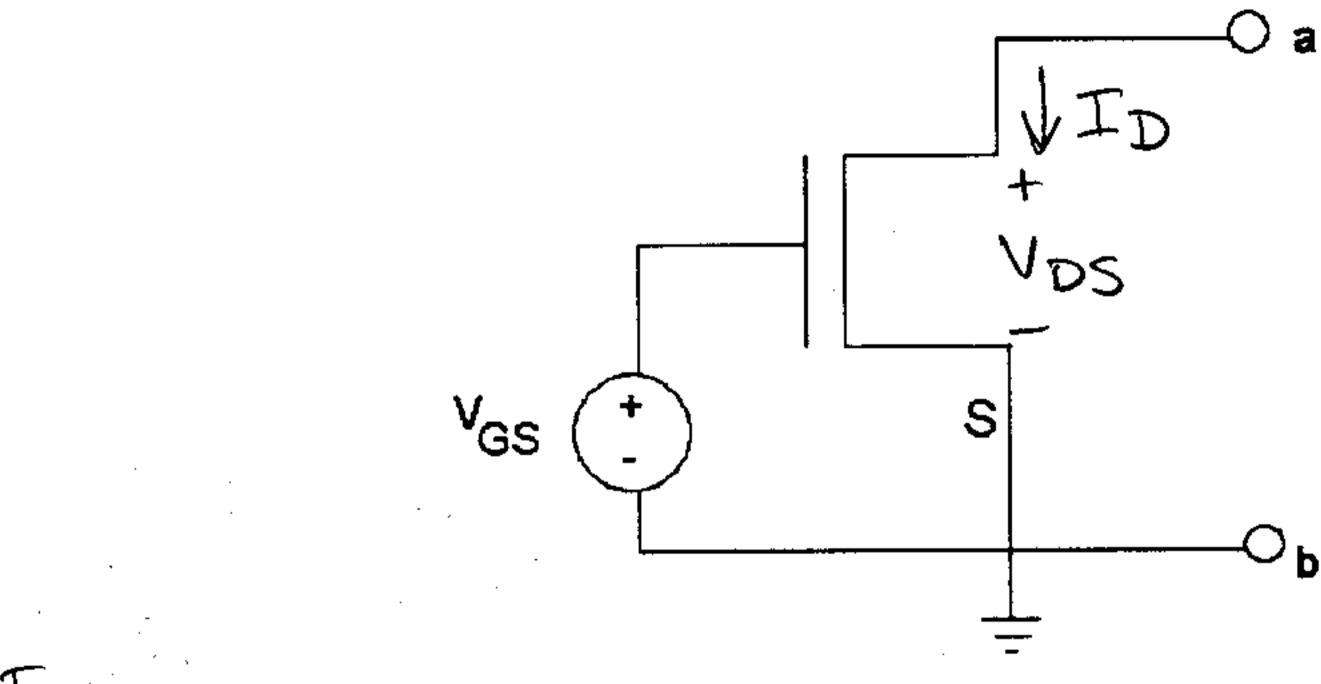

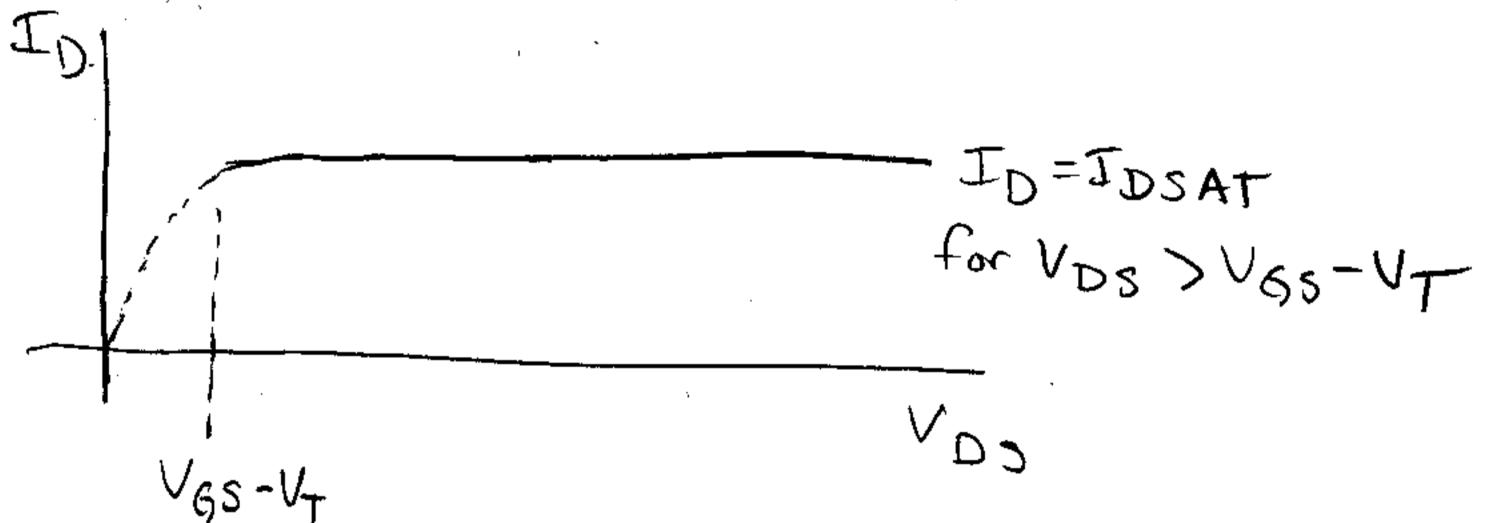

Consider the NMOS transistor circuit below, where V<sub>GS</sub> is constant and above V<sub>T</sub>.

Assume  $\lambda = 0$ . Graph the I<sub>D</sub> vs. V<sub>DS</sub> relationship for V<sub>DS</sub> > V<sub>GS</sub> - V<sub>T</sub>.

Does this circuit have a Thevenin and/or Norton equivalent for this region of operation (when  $V_{DS} > V_{GS} - V_{T}$ )? If yes, give the equivalents. If no, explain why the equivalents do not exist.

Constant corrent, any voltage => corrent source

Norton equivalent:

Thevenin equivalent: does not exist for current source

IDSAT (V) (note direction)

#### **Problem 5 continued**

#### b) 10 Points Possible

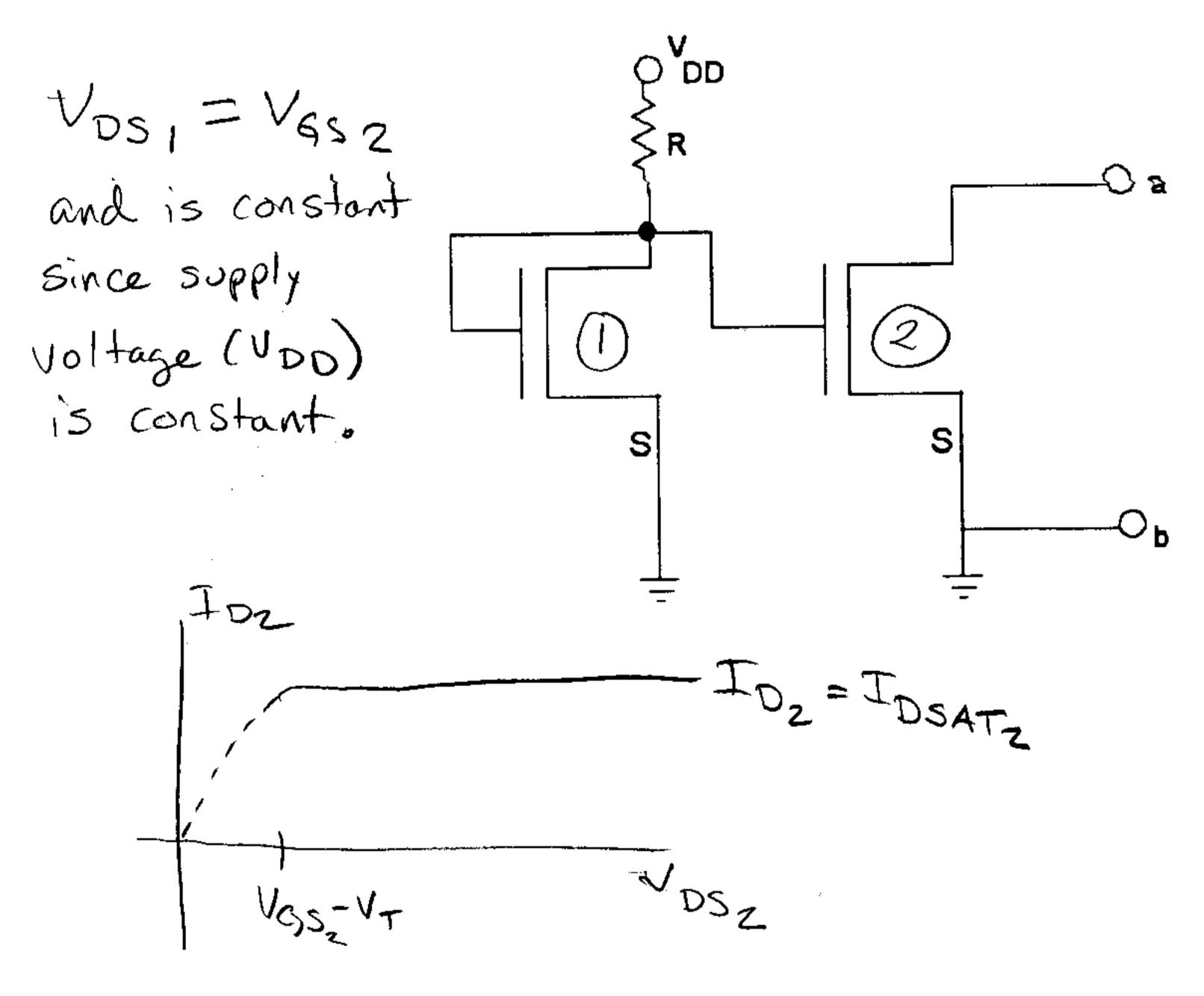

Consider the NMOS transistor circuit below, where  $V_{DD}$  is constant and above  $V_{T}$ .

Assume that both transistors have all the same parameters, and  $\lambda = 0$ .

Graph the  $I_{D(2)}$  vs.  $V_{DS(2)}$  relationship for  $V_{DS(2)} > V_{GS(2)} - V_T$ .

Does this circuit have a Thevenin and/or Norton equivalent for this region of operation (when  $V_{DS} > V_{GS} - V_{T}$ )? If yes, give the equivalents. If no, explain why the equivalents do not exist.

Norton equivalent:

Thevenin equivalent!

does not exist

for corrent source

#### **Problem 5 continued**

#### c) 10 Points Possible

Suppose that as the circuits operate, they heat up. This causes an increase in the electron mobility  $\mu_N$ . How does this affect the operation of the circuit in Part a? How does this affect the operation of the circuit in Part b?

Part as When up increases, IDSAT increases.

The current supplied by this

"Current source" circuit increases.

Part b: When un increases, both JDSAT, and IDSATZ increase.

An increase in IDSAT, means that the voltage over the resistor increases.

Since RIDSAT, + VDS, = VDD (constant), VDS, most decrease.

this decreases the value of VBSZ and therefore decreases IDSATZ.

The increase in the corrent supplied by the corrent source will be smaller for parta due to this negative feedback.

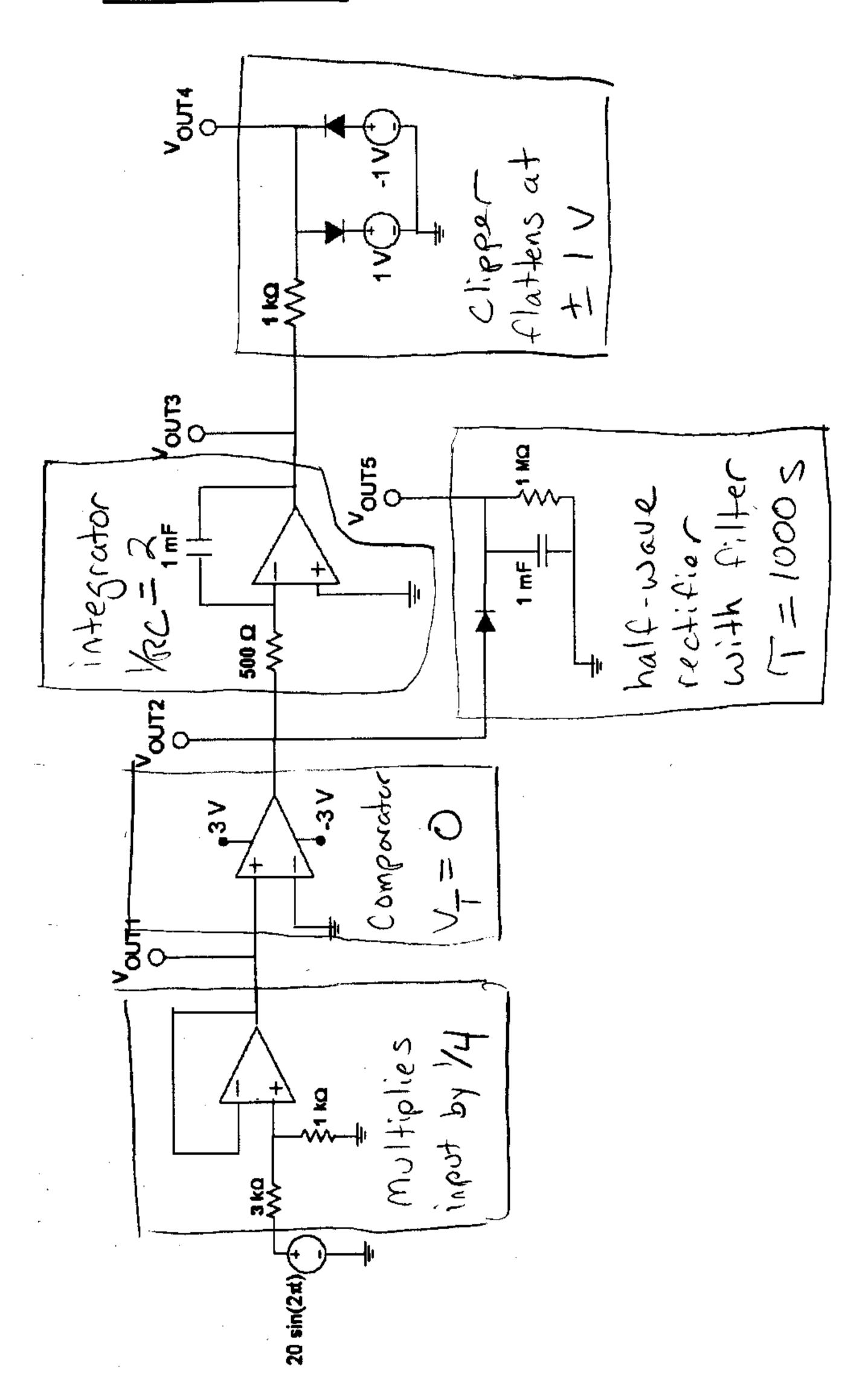

#### Problem 6: 30 Points

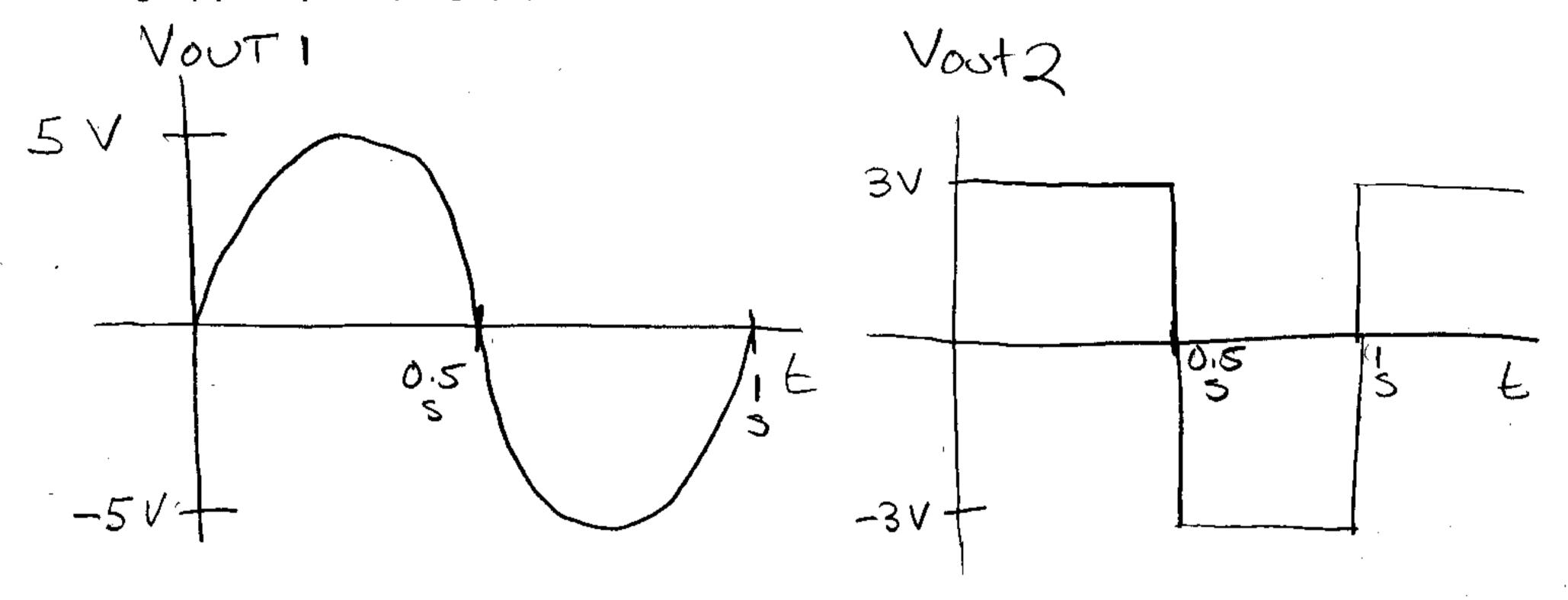

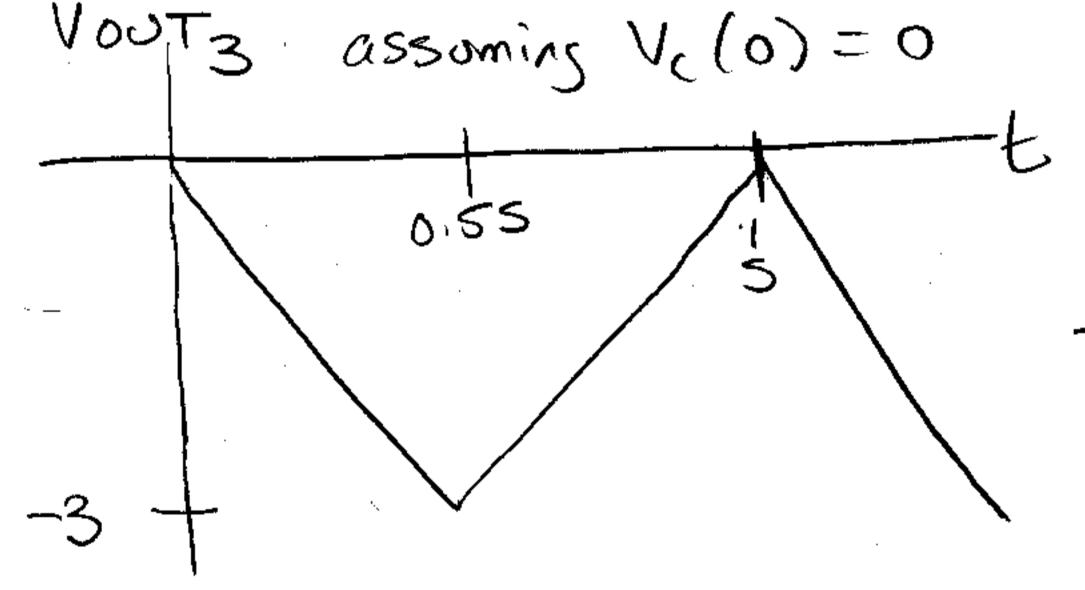

The circuit on the next page has 5 outputs:  $V_{OUT1}$ ,  $V_{OUT2}$ ,  $V_{OUT3}$ ,  $V_{OUT4}$ , and  $V_{OUT5}$ . Graph each of these outputs with respect to time. The more detailed your graphs are, the more points you get (up to 6 points per graph).

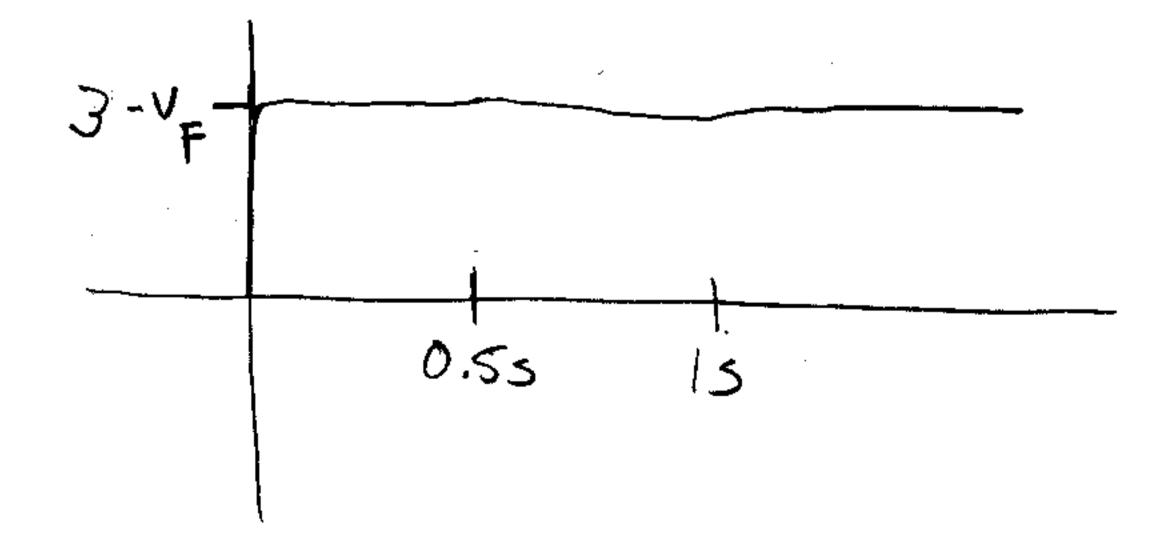

Nouts and Vouty may look different depending on initial phase when circuit started operation. Assuming O phase, outs assuming  $V_c(0) = 0$  Vouty assuming ideal diades

Vouts assuming small-signal diade

- · Charging is almost immediate since diode resistance small

- · Discharging extremely slow, keeps 99.95% of value after 0.55

## Problem 6 continued

#### Problem 7: 60 Points Possible

Perform 2 of the following 3 designs, worth 30 points each. If you complete all 3 designs, the 2 highest scores will be counted.

Indicate clearly which design problem you are answering, and what your final design is. Indicating the important features of your design will help us give you maximum credit.

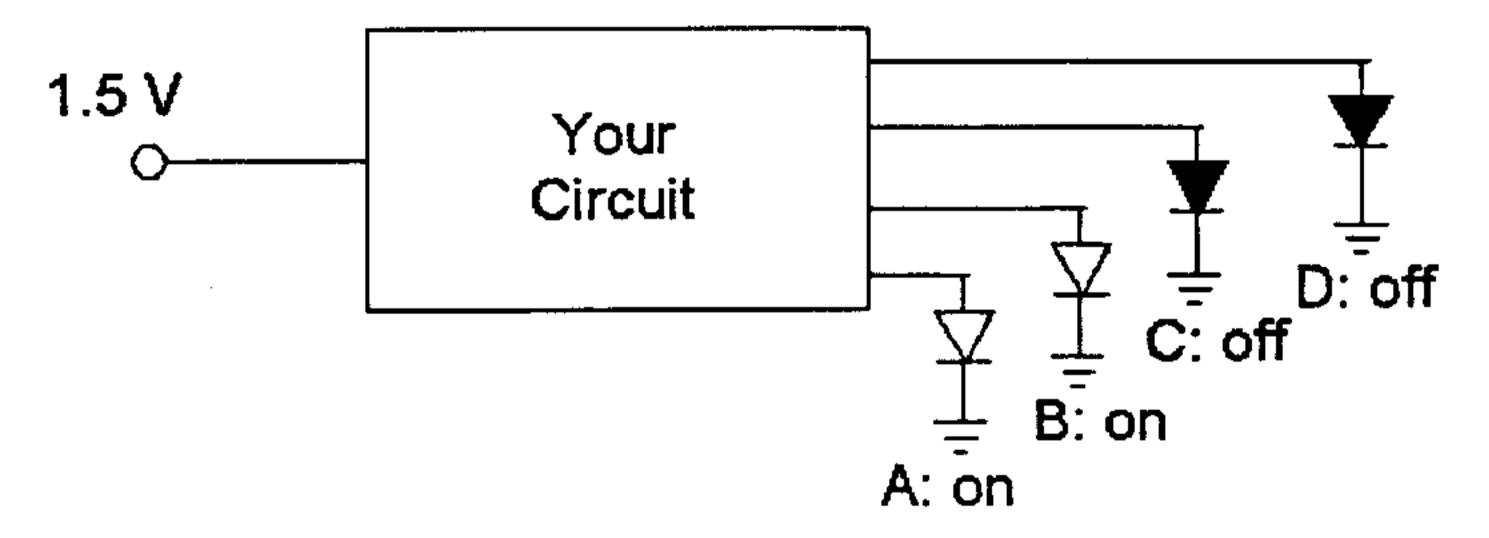

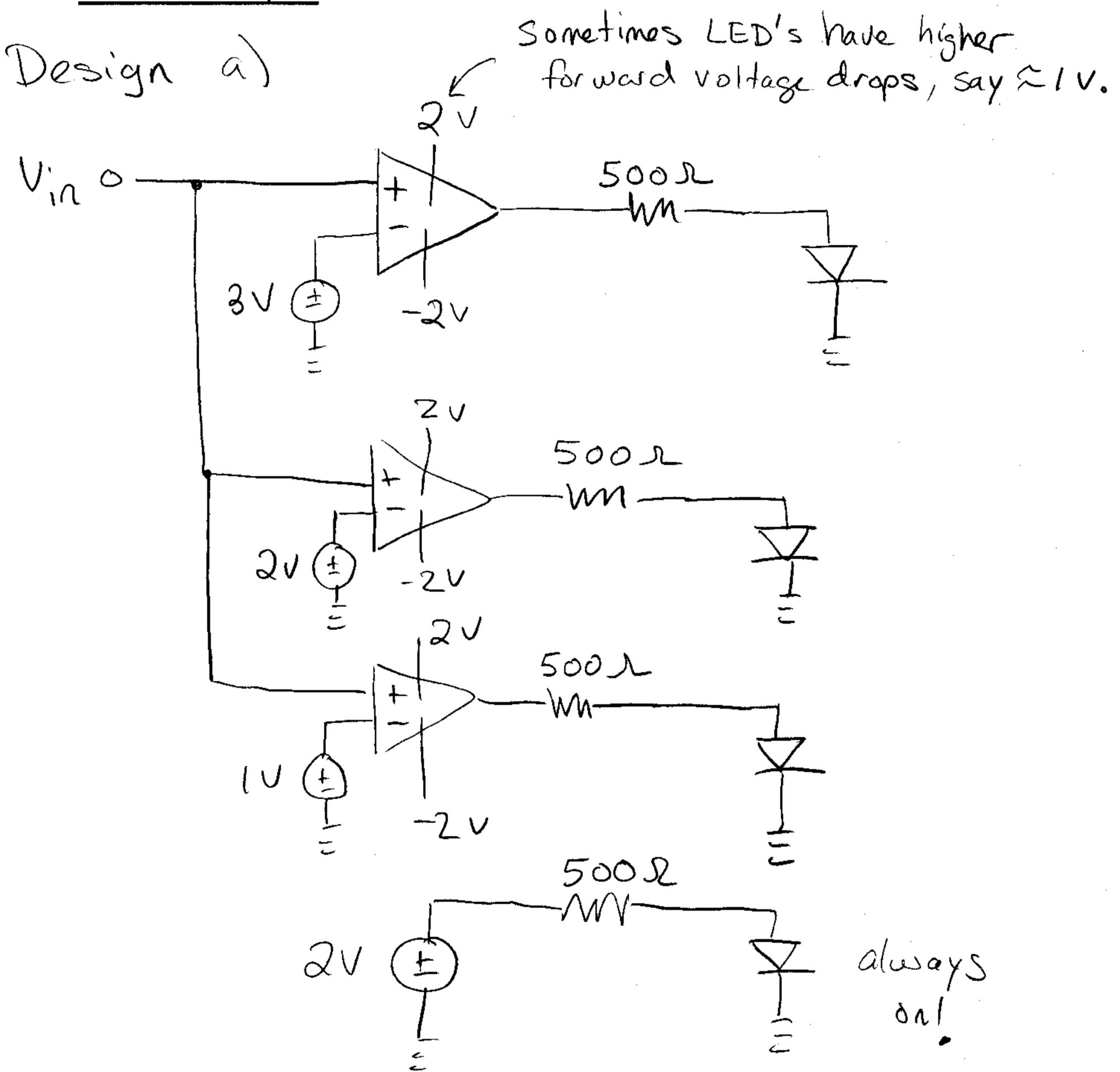

a) As input, you are given an analog voltage (continuous voltage) between 0 V and 4 V. You are also given 4 LED's named A, B, C and D.

If the input voltage is below 1 V, LED A should light up. If input is between 1 V and 2 V, LED's A and B light up. If input is between 2 V and 3 V, LED's A, B and C light up. If input is above 3 V, LED's A, B, C, and D light up.

#### Example:

Vin = 1.5 V, so LED's A and B light up:

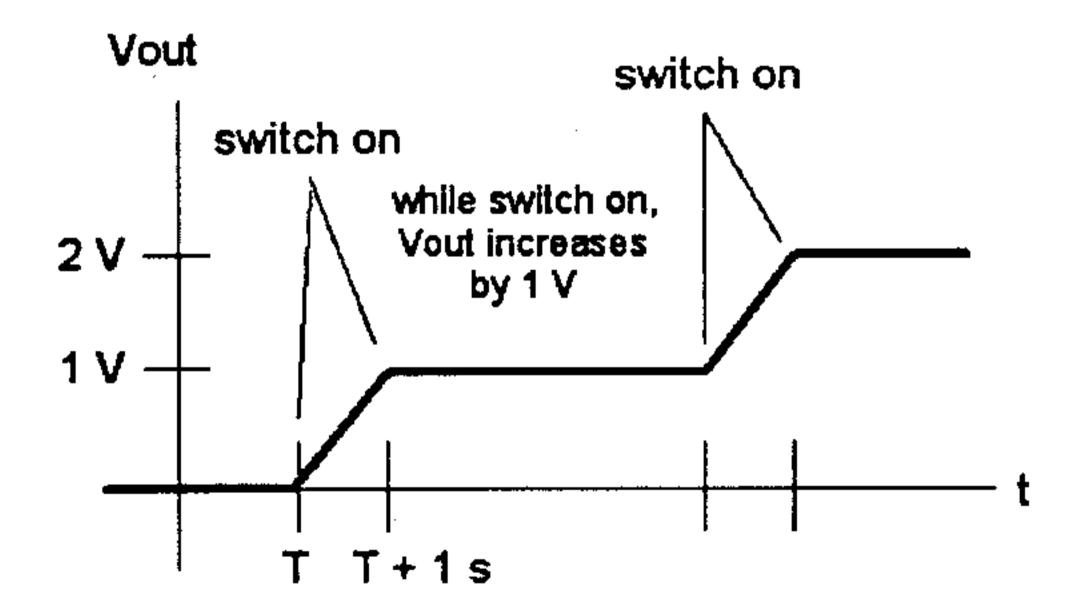

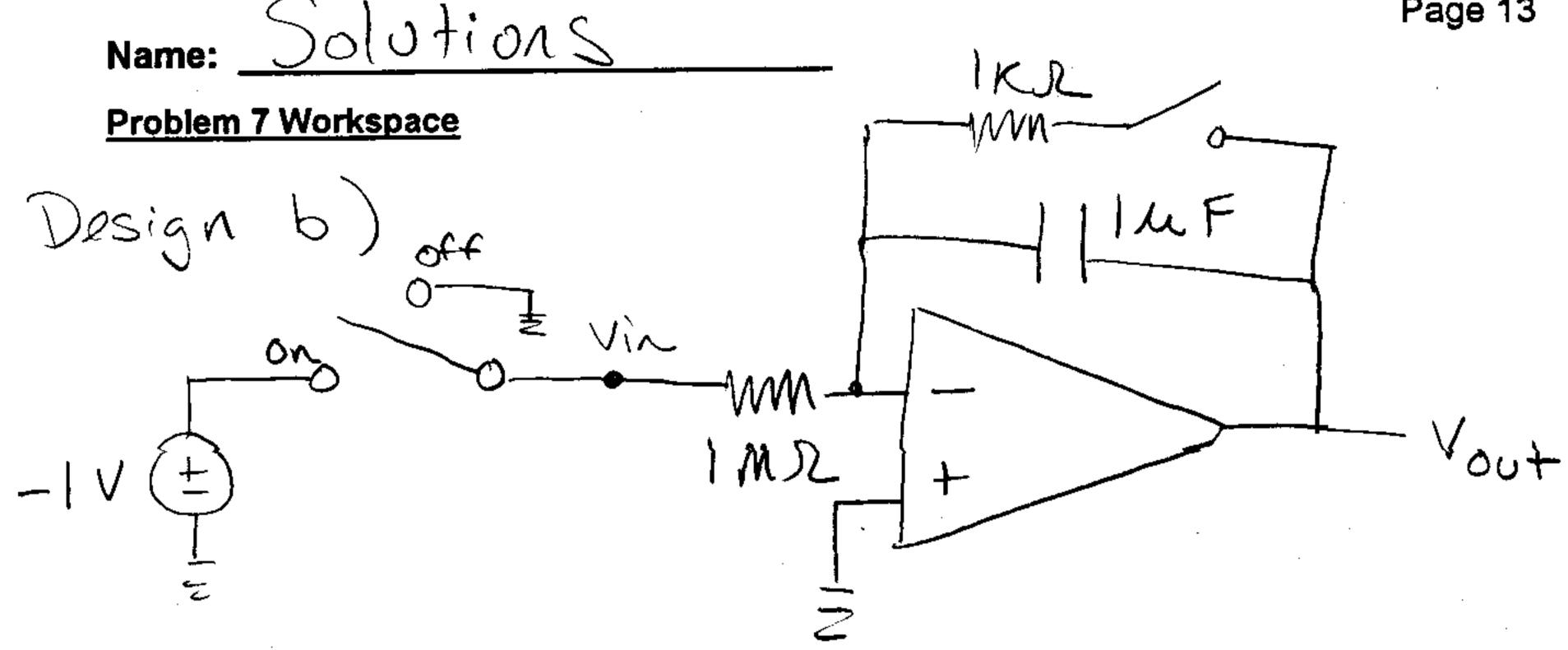

b) A user will occasionally flip a switch on, leave it on for 1 second and then turn it off. Create a circuit that counts how many times the user has done this. The output should look like this:

Include a way to reset the counter in your design, that is, a way to take the output back to zero at the flip of a switch. You may use push-button or regular switches.

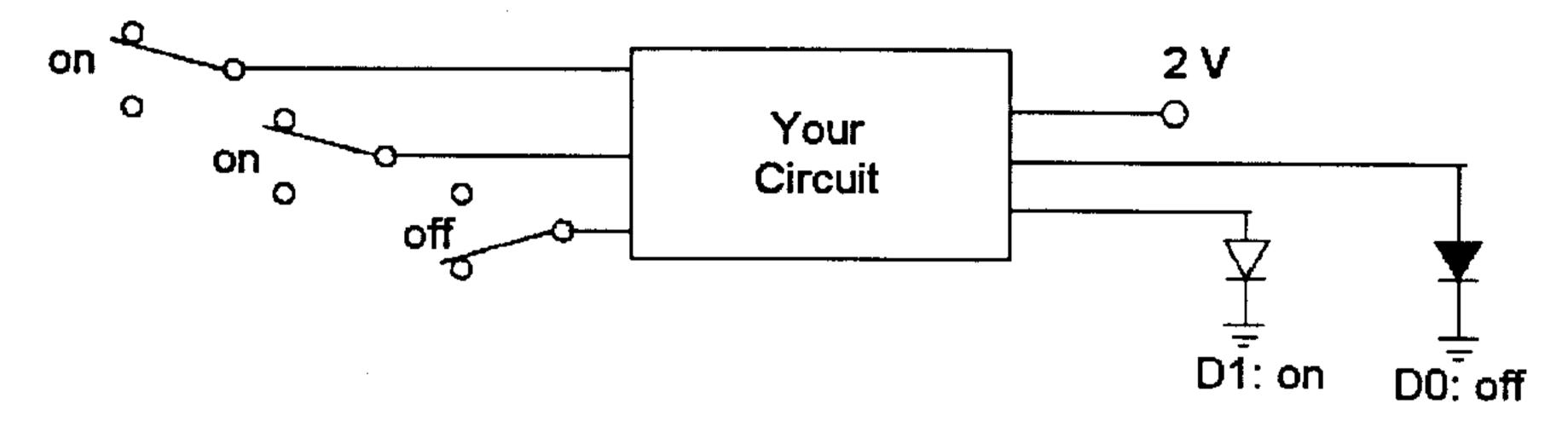

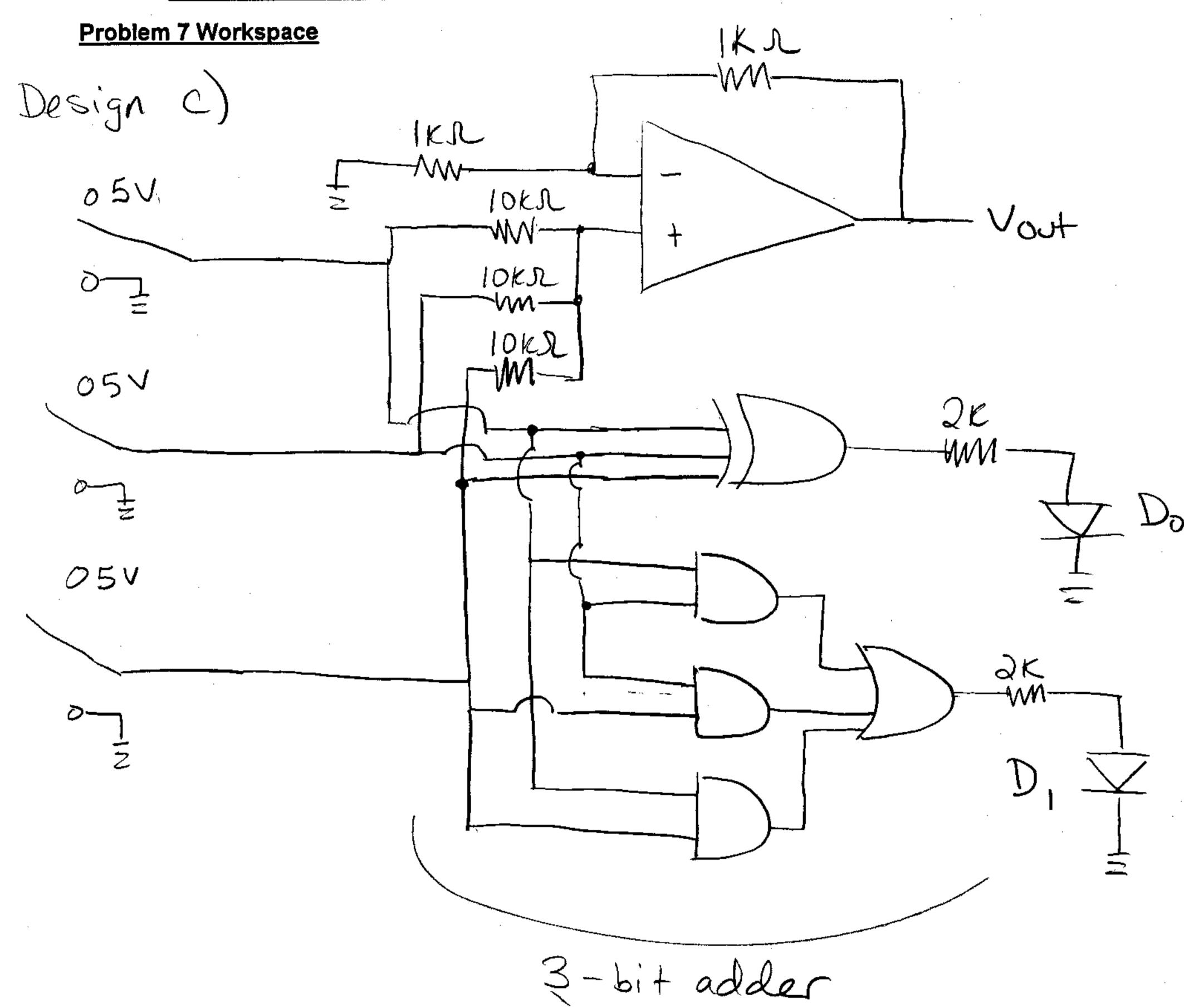

- c) You are given 3 ordinary switches which can be in the "on" position or the "off" position. Create a circuit that counts the number of switches that are "on" and provides output:

- 1) in binary (LED's that represent the binary number of "on" switches)

- 2) and as an analog voltage (output 0 V for 0 switches on, 1 V for 1 switch on, 2 V for 2 switches on, 3 V for 3 switches on).

#### Example:

2 switches turned on, so binary output is 10 and analog output is 2 V:

(You would have to attach something to the on/off terminals on each switch to make this work, that is not shown here for simplicity).

#### Problem 7 Workspace

This is just one of many possible designs.

So makins Rc = 1s accomplishes our needs. Note:

- · When resetting circuit, make Vin = Ov. 100 could attach an override switch that makes Vin = OV when reset swich down.

- · Try to choose small capacitance to make reset time constant small. It you do this with small reset resistance, conent will be high.

- a Operation continues normally until Vout hits a rail. Make the rail your max counter Value.

Too should avoid using logic voltages below 3 v Unless you have special technology.