### <u>EE 40</u>

#### Homework #8

Due Friday, December 6, 2002 at 2 PM

## Problem 1:

Consider the CMOS inverter circuit. Let  $V_M$  be the input voltage which makes  $V_{OUT}$  equal to  $V_{IN}$ . For this input voltage, both the PMOS and NMOS transistors will be in saturation mode.

Let  $\lambda$  equal zero for both transistors, so  $I_D = I_{DSAT}$  for each transistor. With

$$I_{DSAT(N)} = \frac{W_{N}}{2L_{N}} \mu_{N} C_{ox} (V_{GS(N)} - V_{T(N)})^{2} \qquad I_{DSAT(P)} = -\frac{W_{P}}{2L_{P}} \mu_{P} C_{ox} (V_{GS(P)} - V_{T(P)})^{2}$$

$$V_{T(N)} = -V_{T(P)} = 1 V C_{OX} = 5 \text{ fF}/\mu\text{m}^2 L_N = L_P = 1.5 \ \mu\text{m}^2$$

$$\mu_N = 500 \ \text{cm}^2/(\text{Vs}) \mu_P = 250 \ \text{cm}^2/(\text{Vs}) W_P = 10 \ \mu\text{m}^2$$

find the value of  $W_N$  that will lead to  $V_M = 1.5$  V.

#### Problem 2:

Suppose we have connected the output of CMOS inverter 1 to the input of CMOS inverter 2, where both of the inverters have the following characteristics:

| $V_{T(N)} = -V_{T(P)} = 1 V$                | $L_N = L_P = 2 \ \mu m$                    | $W_N = 6 \ \mu m$                       |

|---------------------------------------------|--------------------------------------------|-----------------------------------------|

| $\mu_{\rm N} = 500 \ {\rm cm}^2/({\rm Vs})$ | $\mu_{p} = 250 \text{ cm}^{2}/(\text{Vs})$ | $W_P = 12 \ \mu m$                      |

| t <sub>ox</sub> = 10 nm (oxide thickness)   | $k_{OX} = 4$ (oxide dielectric constant)   | $V_{DD} = 5 V$                          |

| $L_{I} = 30 \ \mu m$ (interconnect length)  | $W_I = 1 \ \mu m$ (interconnect width)     | $C_{DB(P)} = C_{DB(N)} = 50 \text{ fF}$ |

Find the propagation delay from the input of inverter 1 to the output of inverter 1 for a perfect high to low input transition.

Use  $W_N$ ,  $L_N$ ,  $W_P$ ,  $L_P$  as the channel dimensions (for calculating  $I_{DSAT}$ ) as well as the gate dimensions (for calculating  $C_{GB}$ ). Let  $\lambda$  equal zero for all transistors.

# Problem 3:

Consider a CMOS inverter with

$$\label{eq:constraint} \begin{split} \mathsf{R}_{\mathsf{N}} &= 3 \; \mathsf{k} \Omega \qquad \qquad \mathsf{C}_{\mathsf{DB}(\mathsf{P})} = \mathsf{C}_{\mathsf{DB}(\mathsf{N})} = \; \mathsf{C}_{\mathsf{GB}(\mathsf{P})} = 50 \; \mathsf{fF} \\ \\ \mathsf{R}_{\mathsf{P}} &= 2 \; \mathsf{k} \Omega \qquad \qquad \mathsf{C}_{\mathsf{GB}(\mathsf{N})} = 75 \; \mathsf{fF} \end{split}$$

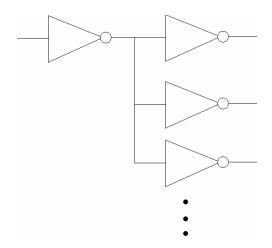

The output of this inverter is connected to the input of several other identical inverters, as shown at right.

Each inverter connected at the output adds an interconnect capacitance  $C_1$  of 100 fF.

Determine the number of inverters that can be connected (the "fan-out") if the propagation delay from the input to output of the first inverter may not exceed 20 ns.

## Problem 4:

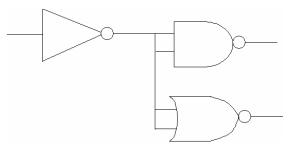

Consider a CMOS inverter with output connected to both inputs of a NAND gate and both inputs of a NOR gate as shown.

Using the resistance and capacitance values given in Problem 3 for the transistors, determine the propagation delay from the inverter input to inverter output for both low to high and high to low (perfect) input transitions.